PREST PI

Research Project

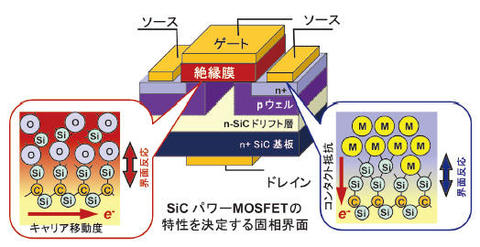

Interface Engineering for High Performance SiC MOSFETs with Low On-state Resistance

Profile

Koji Kita

Outline

The reduction of on-state resistance is inevitable to achieve high performance SiC-MOSFETs for power device applications. In this study the device performance improvement will be demonstrated by developing new process technologies based on precise control of hetero-solid-interface reactions. The process to form a high-quality ultrathin oxide layer on SiC, by suppressing the defect formation due to imperfect oxidation of SiC, will be developed for the enhancement of carrier mobility. In addition the process to reduce the SiC-metal contact resistance, by tuning the energy barrier at the interface, will be also investigated.