成果概要

スケーラブルで強靭な統合的量子通信システム[1] 強靭で大規模な通信網を実現する新しいネットワークアーキテクチャ・プロトコルの開発

2024年度までの進捗状況

1. 概要

分散型量子コンピュータの実現には、単に多数の量子コンピュータを接続するだけでなく、それぞれの処理能力を統合的に活用し、全体として一体的な量子アプリケーションを実行可能にする分散量子情報処理環境の構築が不可欠です。その実現には、量子コンピュータ本体、通信インターフェース、量子通信ネットワークの3要素が求められます。特に、量子通信ネットワークは、大量の量子データを扱っても全体の性能低下を起こさない効率性、スケーラビリティ、耐障害性、および運用性が必要になります。

全体的な研究開発プログラムにおいて、本プロジェクトは分散型量子コンピュータの実用化に必要な基盤技術を提供し、他のプロジェクトにおいて開発される量子コピュータのネットワーク化による早期の大規模誤り耐性量子計算の実現を目指しています。

本年度の本項目では、量子ネットワークの実証に向け、ハードウェア指標の最終的な定式化に着手するとともに、量子リンクプロトコルの古典的側面の実装を開始しました。モジュール間インターフェース仕様を詳細化し、1000ノード規模のシミュレーション拡張を通じて実装に向けた研究を進めました。また、ノイズ低減技術や動的ネットワーク設計指針を明確化し、異なる精製プロトコルの性能比較を数値解析によって実施しました。

本項目では、特にアーキテクチャ、プロトコル、古典制御の観点から適切なネットワーク設計を行うことを目的としています。実際のシステム設計とテストベッドでの計測に加え、対応するネットワークシミュレーションも駆使してシステムとして実際に実現できる性能がどのように決まるのかを明らかにしました。

2. これまでの主な成果

今年度は量子ネットワーク実用化に向け、エラー確率や光子ロス率などのパラメータを詳細に評価し、量子通信プロトコルの実装モデル構築とエラー対応策の具体化を進めました。

また、リンクレイヤ構築にあたり空間分割および時分割方式の検討を進め、高精度時刻同期のためFPGAを用いたTime-to-Digital Converter実装やDragonfly型時刻同期手法(TidyFly)の検討を開始しました。

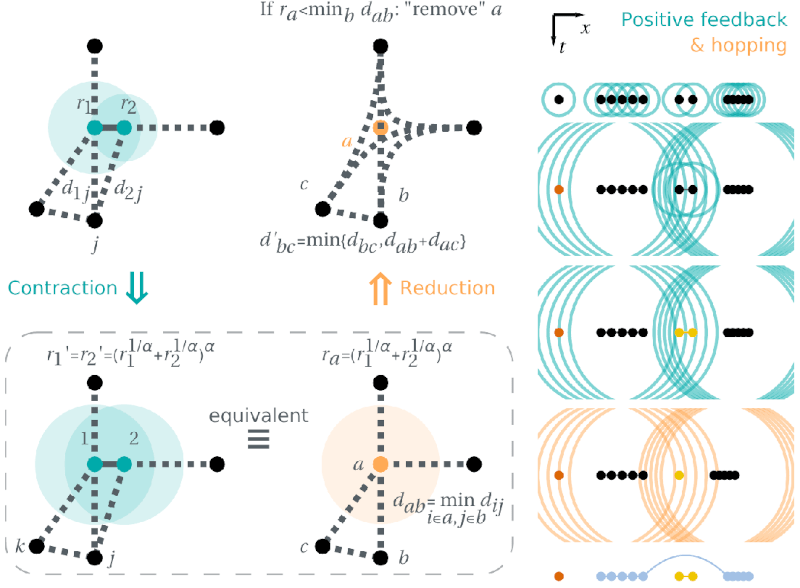

ネットワークインターフェースとしてQ-Flyアーキテクチャを中心に検討を深め、光スイッチを利用した初の物理的な実証実験を実施しました。これに伴い、量子ネットワークの仕様策定やデバイス制御ソフトウェア(PnPQ)の開発、リピータグラフ状態に基づくアーキテクチャ設計を進め、小規模なシリコンフォトニクスチップの設計も実施しました。加えて、量子状態の純化アルゴリズム開発およびジョブスケジューリングの課題にも取り組みました。

ノイズ低減に関しては、ボソニックコードを用いた量子中継システムを評価・改善し、特にキャットコードに量子メモリを統合することで性能を大幅に向上させました。また、遅延を伴うネットワークの動的構造解析を行い、最適な構成とプロトコル設計を提案しました。さらに、二者間・多者間状態の精製ツールを開発し、表面符号実装のためのモジュール型アプローチの実現可能性を評価しました。また、GHZ状態の直接生成法により、量子コンピュータの実装簡素化を目指した研究も開始しました。最後に、極低温超伝導量子ビットと光量子通信を組み合わせた誤り耐性通信の基本パターンを定義し、その実現に必要な各種性能指標を設定しました。

3. 今後の展開

引き続き、理論、実証、シミュレーションを組み合わせて賢いネットワーク設計を進め、大規模分散量子計算機の効率的な実現に向けて開発を進めていきます。特に、量子光通信技術、量子メモリ・中継技術、分散量子アプリケーションでの開発要素を通信プロトコルや古典制御技術を用いて繋ぎ合わせ、テストベッドを通信システムとして動かすことを目指していきます。また、他のプロジェクトとも連携し、大規模分散量子計算アーキテクチャの観点から今後の開発指針を得ることを目指します。