成果概要

拡張性のあるシリコン量子コンピュータ技術の開発[1] 拡張性を有する誤り耐性Si量子ビットデバイス技術

2024年度までの進捗状況

1. 概要

本研究開発項目では、誤り耐性を有する大規模化に適したSi量子ビットデバイス技術の開発を目指します。これまでに少数量子ビット系では誤り耐性閾値を上回る高精度な制御が達成されていますが、この量子ビット制御性を維持しながら、大規模化可能なアーキテクチャ・量子ビットレイアウト・試料構造・信号伝送技術の開発に取り組みます。これらの要素技術を確立し、真に拡張性を有するSi量子ビットデバイスを追究します。

本項目では各量子ビットパラメータの電圧制御が可能であり、試料中の均一性にも優れたSi/SiGe量子井戸型の量子ビットデバイスを作製します(図1)。産業プロセスとも連携し、高精度な量子演算操作を実証することで、大規模な誤り耐性量子計算の実現に向けたブループリントを描くことを目指します。

2. これまでの主な成果

- ① 12量子ビット試料を試作し、実験準備を完了

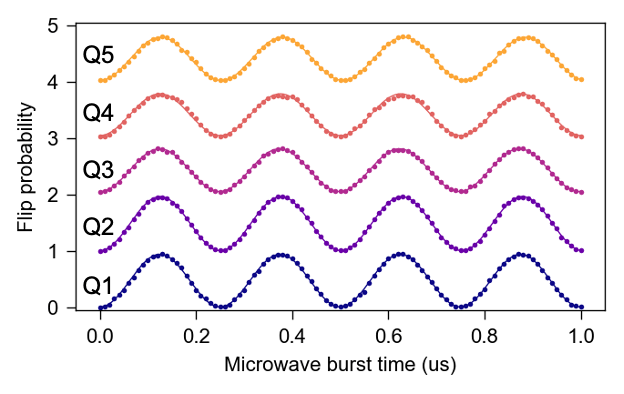

- ② 99.99%を上回る1量子ビットゲート忠実度を実証

- ③ 2量子ビットの制御位相ゲート操作におけるエラーのメカニズムを解析し、その補償方法を解明

- ④ 量子誤り訂正に求められる高速・高忠実度な量子ビット読み出しおよびアクティブリセットを実証

- ⑤ 大規模量子ビット制御に対応するパルス信号生成回路と信号伝送用シリコン貫通ビアプロセスを開発

量子計算の基本要素である1ビット、2ビットゲート操作のエラーをゲートセットトモグラフィーおよびランダム化ベンチマーク法などの手法で解析し、制御波形を体系的に最適化することで世界最高レベルの制御忠実度を達成しました(②、③)。また、エラーの起源に関わる量子ビットのノイズ相関を検出・解析しました。

さらに量子誤り訂正の実装に不可欠な高速・高精度量子ビット読み出し(1µsで忠実度99%以上)とフィードバック制御によるビット反転・初期化操作を実証しました(④)。

また、多数の量子ビットを高い精度で制御するためのパルス信号生成器を開発しました。希釈冷凍機の信号経路上で劣化するパルス波形を高い分解能で補正する回路を考案し、実機による動作確認を行いました(図3(a))。さらに、密集した量子ビットに高品質な信号を供給するため、ボンディングワイヤを使わないチップパッケージング構造を目指し、シリコンインターポーザに貫通ビアを形成するプロセスを開発しました(図3(b)、⑤)。

以上の技術を統合し、12量子ビット高忠実度実験の実施に向けたセットアップと試料の準備を完了しています(①)。

3. 今後の展開

高精度な量子ビット制御に求められる技術的要件の明確化とエラーのメカニズム解明が進展しました。この成果をもとに、量子ビットの集積化に伴う課題である、スピンシャトリング等の遠隔量子ビット結合の導入や、密集した量子ビットに対するシグナルインテグリティを担保する技術の開発に取り組みます。これらの要素を統合して誤り耐性の獲得に適したスケーラブルなSi量子ビットデバイスの設計を目指して研究を推進します。