成果概要

拡張性のあるシリコン量子コンピュータ技術の開発[3] 誤り耐性を満たす同位体制御Si/SiGe基板技術

2024年度までの進捗状況

1. 概要

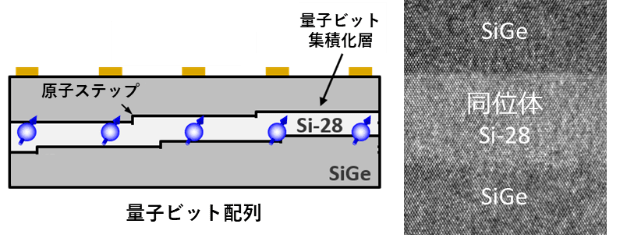

本研究開発項目では、誤り耐性を有するシリコン量子計算機の実現に向けて、量子ビットデバイスと中距離量子結合を搭載するのに必要な母体材料である、磁気的雑音を排除した同位体制御シリコン・シリコンゲルマニウム(Si/SiGe)の基板開発を目指します。量子ビットの性能を最大限に引き出し、誤り耐性閾値を超えた忠実度を保持したまま、量子ビットを自在に配列制御するために、集積化層となる同位体Si-28がSiGe薄膜に埋め込まれた高品位な量子井戸型の基板材料が必要となります。

本項目では、量子ビットの制御性と配列自由度を格段に向上させるため、①量産プロセスに適応し、高品質な同位体層の成膜が可能な同位体制御技術、及び②原子ステップというヘテロ界面の段差を抑制する界面制御の基盤技術の開発に取り組みます。また、③同位体基板の材料性能を広範囲に評価するプロセス基盤の技術確立を並行し、半導体産業との互換性を維持して大規模な誤り耐性型シリコン量子計算の実現に向けた新たな基盤技術の確立に挑戦します。

2. これまでの主な成果

① 高品質成膜を可能とする同位体制御技術の開発

配列した量子ビットを安定的に動作させ、量子状態を保持したまま長距離にわたってコヒーレントに伝送するには、集積化するスケールで同位体基板を高品質化し、試料構造内のポテンシャルの均一性を確保することが重要です。これまでに、電荷トラップとなる不純物濃度の低減、同位体層での界面の急峻性と平坦性の向上、また歪みや組成の揺らぎに起因する不均一性を抑制した小規模な同位体基板を試作し、量子ビットを搭載する基板側全体の高品質化要件に基づいた量産対応の同位体成膜システムの稼働を進めています。

② 軽元素を用いた界面制御に向けた要素基盤技術の開発

量子ビット配列と干渉し得る界面ステップの微視的起源の理解に基づいた発生抑制手法として、軽元素である水素の欠陥終端や結合切断といった相反的特性に着目し、同位体基板の内部構造改変による新たな界面制御技術を考案しました。この原理検証に向けた基盤技術として、同位体界面のステップ間隔をあらわす構造因子をマルチスケールで精密測定する顕微評価技術を開発しました。現在、界面の傾斜角度に対する高い計測精度と観測エリアにおける拡張性及び実用性を備えた観測技術を基に、効率的な局在水素導入とそれによる界面傾斜の抑制効果を検証する試験を進めています。

③ 同位体基板の大面積プロセス評価技術の開発

量子ビットを大規模集積化する同位体基板に内在する結晶欠陥に関して、広範囲にデバイス性能評価する技術開発に取り組みました。量子ビットの性能を左右し得る、同位体基板内の電気的雑音を高速計測するための一次元なスプリット型構造配列によるデバイス設計・試作を進めました。

また、①で開発している界面平坦性を高めた同位体基板において一定数の量子ビットを実装し、量子操作性の向上に必要なバレー分離を含む性能調査を行いました。これまでに巨大なバレー分離を実現すると同時に、量子ビットの位置に応じてバレー分離の不均一性が生じることを見出しています。これにより同位体基板本来の性能を引き出し、スケールアップに必要な知見を得ました。

3. 今後の展開

誤り耐性閾値を超える量子ビット配列を搭載可能で、量子状態を転送する中距離量子結合のスケールで結晶欠陥による散乱がない、拡張性を有する高品位な同位体制御Si/SiGe基板の技術開発を進めます。今後、軽元素導入による界面制御技術の原理検証を進め、大面積デバイス評価による同位体基板の実用性の検証と改善に取り組みます。また、同位体基板の供給と項目間での知見共有を進め、半導体産業との連携強化に向けた根幹技術としていきます。これらの要素技術を基に、同位体基板の品質と量子ビットのデバイス性能を紐づける新たなスケーリング技術の確立を目指し、真に誤り耐性を満たすシリコン量子ビットの基板材料プラットフォームの実現に向けた研究開発を推進します。