成果概要

拡張性のあるシリコン量子コンピュータ技術の開発[2] 中距離量子結合技術

2024年度までの進捗状況

1. 概要

将来の大規模な量子プロセッサを実現するには、半導体中の量子ビットを安定的かつ柔軟に接続・配置できる技術が不可欠です。本研究開発項目では、ナノメートルの精度で集積できる半導体技術を活用しつつ、マイクロメートルスケールで量子情報を結ぶ「中距離量子結合」の実現に取り組んでいます。

2. これまでの主な成果

2024年度までに、以下のような成果を得ています。

1. 各種量子ビット伝送方式の実現可能性の検証

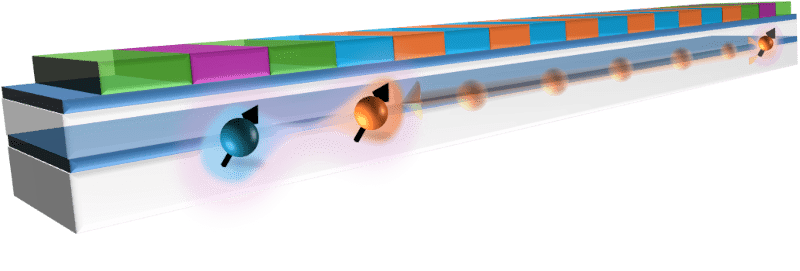

半導体量子ビットを伝送する主な方式には、トンネル効果で順に移動させる「バケツリレー方式」、電位を連続的に移動させる「コンベイヤーモード方式」、または、中継量子ビット間の交換相互作用を利用する方式などがあります。それぞれについて、小規模の電磁界・波動関数シミュレーションを行い、方式ごとの特性や課題、適した動作方法を検証しました。

2. 多重量子ドットの測定と制御系の検証

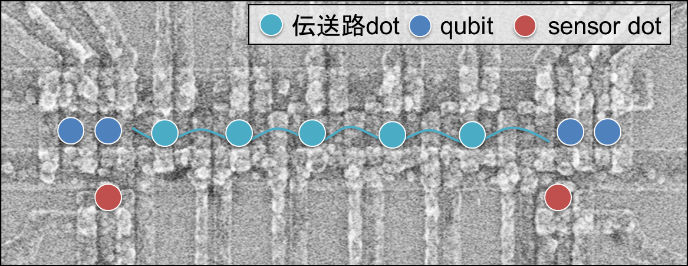

中距離量子結合技術の検証には、量子ビットを伝送するための伝送路構造が必要です。この伝送路として、量子ビットを閉じ込めるための量子ドットを一次元に並べた多重量子ドットの構造を用います。

これまでに、研究室レベルのデバイス作製技術を応用してこの構造を開発し、極低温下での測定を実施しました。この測定を通じて、今後の中距離量子結合技術の実証に必要な電圧制御システムを整備しています。

3. コンベイヤーモード方式へ向けたデバイス開発

これまでの検討により、周期的な電極構造と周期的な電圧信号を利用するコンベイヤーモード方式が、構造の規則性やスケーラビリティの観点から有望であることが明らかになってきました。この方式の実現には、移動中の量子ビットの状態を励起してしまわない電圧制御や補償技術などのハードルが残されています。これらを克服できれば、量子ビット間の自由な配線に近づき、誤り訂正技術の大規模化に向けたブレークスルーが期待されます。

3. 今後の展開

本研究で得られた成果は、将来的な大規模量子プロセッサの構築に向けた基盤技術となります。特に、産業レベルの集積技術と適合可能な構造の中で、量子ビット間の結合を高精度かつ高速に実現する方法の開発が、今後本格的に必要となります。現在はその実証に向けた準備段階にあり、量子ビットの一つ一つの動きを追うことで、スケーラブルで再現性の高い中距離量子結合技術の確立を目指しています。