成果概要

スケーラブルな高集積量子誤り訂正システムの開発[3] 光/Cryo CMOS集積回路によるスケーラブルな古典-量子インターフェース

2024年度までの進捗状況

1. 概要

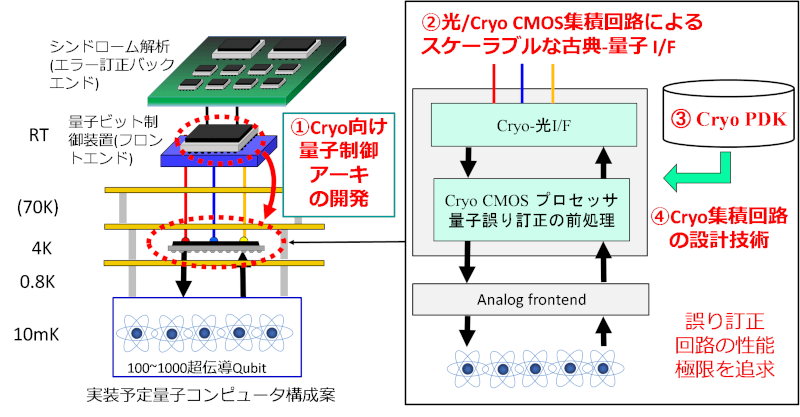

スケーラブルな量子コンピュータを実現するためには、室温環境-極低温環境をまたぐ膨大な配線をコンパクトにしつつ、古典-量子間で通信される膨大な量のデータを効率的に伝送する必要がある。本研究開発項目では、図1の通り、古典-量子の境界で動作する光/Cryo CMOS集積回路を開発し、高効率な情報伝送を実現する。キー技術として図1の①~④を開発している。進捗状況として、(a)量子ビット制御アーキテクチャ、(b)光集積回路の低温特性測定、(c)Cryo CMOS向けPDK、(d)Cryo集積回路の設計技術において成果を得ている。

2. これまでの主な成果

(a)量子制御アーキテクチャ

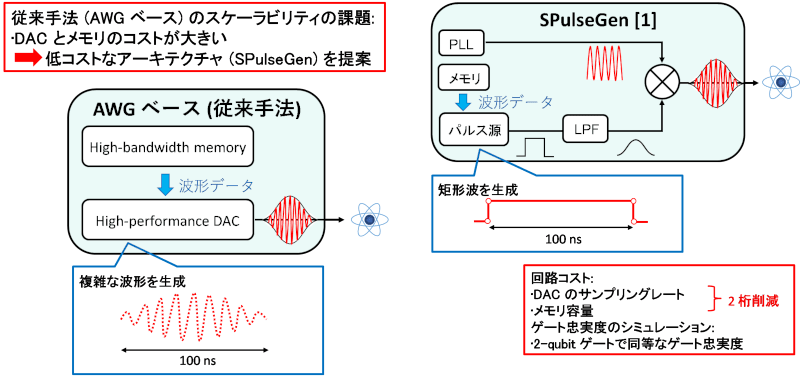

図2に示す低コスト量子ビット回路アーキテクチャを提案し、従来よりも大幅に簡素な素子で十分なゲート忠実度を実現可能なことを明らかにした。加えて、得られた知見を基にデザインガイドラインの構築を進めた。

(b)光集積回路の低温特性測定

液体窒素中に光集積回路を入れ、その動作測定を測定した。室温動作時と同様のスイッチング特性を確認した(図3)。液体ヘリウム環境下での光集積回路の特性評価環境を構築した。

(c)Cryo CMOS向けPDK

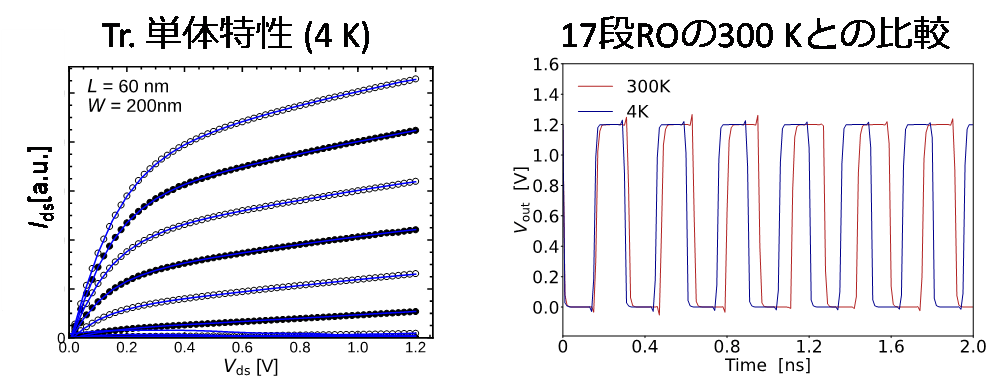

昨年度行った機械学習ベースのモデル化手法に加えて、業界標準モデル化手法および表面電位に基づくモデリング手法を開発した。業界標準モデルについては広く採用されているBSIM4を対象として電流の基板バイアス依存性をモデル化した(図4左)。リング発振器設計に応用し、試作することなく、基板バイアス印加と電圧スケーリングにより電力最適化設計ができることを実証した(図4右)。

(d)Cryo集積回路の設計技術

極低温環境におけるCMOS回路の信頼性向上に向け、極低温動作可能な測定環境(クライオスタット、FPGA制御基板等)を構築するとともに、これを用いてトランジスタのランダムテレグラフ雑音(RTN)特性の統計的解析を行った(図5)。極低温領域ではRTNの影響が100K付近で一時的に緩和される一方で、3.8Kといった極低温ではむしろ顕著となることを実験的に明らかにした。

3. 今後の展開

各要素技術の統合を積極的に検討し、提案システムの実証およびスケーラビリティ見積もりを狙う。