成果概要

大規模集積シリコン量子コンピュータの研究開発[4] 小規模回路による量子演算

2024年度までの進捗状況

1. 概要

本研究開発項目は、大規模なシリコン量子ビットアレイ構造の開発と並行して、将来的にその一部を構成する小規模実験回路を活用することにより、量子コンピュータ実現に向けた課題の早期抽出を目指しています。

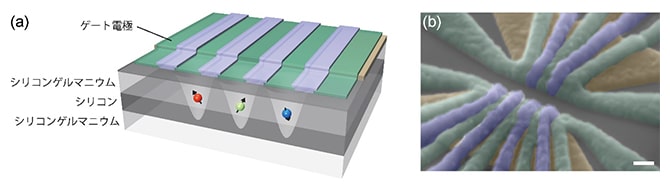

図1に示すような、量子ビットとしての動作が確立している小規模実験回路を用いて、量子ビットの初期化、読み出し、コヒーレント制御といった基本動作の高性能化を追究し、それらを組み合わせた量子演算操作を実証します。大規模な系での誤り耐性量子計算の実現可能性や、アレイ構造と両立する量子ビットの演算方式を検証し、プロジェクトの目指す大規模アレイ構造の設計指針を与えることを目指します。

2. これまでの主な成果

主に以下の6つに大別されます。

- ①アレイ内部の量子ビット初期化・読み出し手法を確立

- ②3つの量子ビットに対する汎用的な制御を実現

- ③誤り耐性閾値を上回る高精度2量子ビット操作を実現

- ④量子ビット制御の高速化とエラー低減の関係性を解明

- ⑤3つの量子ビットによる位相誤り訂正操作を実証

- ⑥量子ビット間の誤り相関を観測

このうち、①は一次元シリコン量子ビットアレイ構造内部の量子ビットの初期化および読み出し手法を確立するものです。これまで困難だったアレイ内部の量子ビットの初期化・読み出し操作を実証しました。

②では、3つのシリコン量子ビットに対する汎用的な(ユニバーサルな)量子操作を実証しました。高い忠実度(88%)で3つのシリコン量子ビットの量子もつれ状態を生成できていることを世界で初めて確認しました。

③、④では、これまで量子ビット制御のボトルネックとなっていた2つの量子ビット間の制御NOT操作の高忠実度化を実現しました。誤り耐性量子計算の実現に十分な水準の高忠実度(99.5%)を実証し、雑音の低減によるさらなる高精度化に向けた研究開発の指針を得ました。

⑤では、3つの量子ビットの高忠実度制御を組み合わせて、位相誤り訂正回路をシリコン量子ビットで初めて実証しました(図2)。誤り耐性シリコン量子コンピュータの開発における重要なマイルストーンを達成したと言えます。

⑥では、アレイ構造における量子誤り訂正で課題となる、量子ビット間の誤り相関を評価しました。シリコン量子ビットに誤りをもたらす位相回転速度のゆらぎの測定(図3)から、隣接サイト同士でシリコン量子ビット間の誤り相関が強くなりうること、相関が距離に応じて減衰することなどが明らかになりました。また、相関に着目した雑音源の特性評価手法の開拓、電荷雑音相関評価の新規手法確立など、シリコン量子コンピュータの将来設計と性能向上に資する成果が得られました。

3. 今後の展開

誤り耐性量子コンピュータの実現にむけて、これまでの高忠実度制御のパフォーマンスを損なわずに大規模化を図る方策の開発と、シリコン量子ビット誤り相関の理解深耕および活用に取り組んでいきます。シリコン量子ビットおよびアレイ構造の特徴、特性、制約等を踏まえて、大規模化に適した操作、初期化、読み出しなどの制御手法を検討し、大規模アレイ構造への適用を目指します。