成果概要

大規模集積シリコン量子コンピュータの研究開発[1] 量子コンピューティングシステム

2024年度までの進捗状況

1. 概要

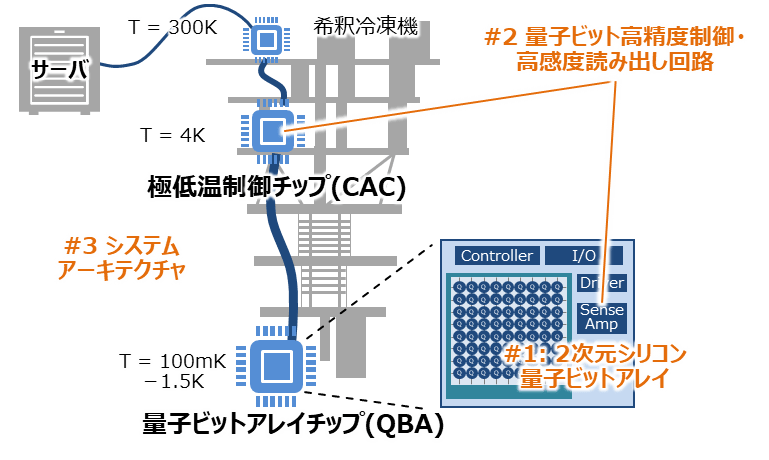

本研究開発項目は、プロジェクト全体を統括して量子コンピュータをシステムとしてまとめる役割を担いますが、図1の三つ(#1、#2、#3)の具体的な研究開発課題に取り組んでいます。

一つ目は、シリコン量子コンピュータを大規模化する際のマイルストーンである量子ビットの「2次元量子ビットアレイ」化に関する研究です。二つ目は、この量子ビットアレイを高精度に制御し量子情報を高感度に読み出すために必要となる「量子ビット高精度制御・高感度読み出し回路」を開発します。三つ目は、システム全体をコンピュータとして動作させるための「システムアーキテクチャ」を開発します。これらによって、シリコン半導体技術の特徴を活かした大規模集積シリコン量子コンピューティングシステムの実現をめざしていきます。

2. これまでの主な成果

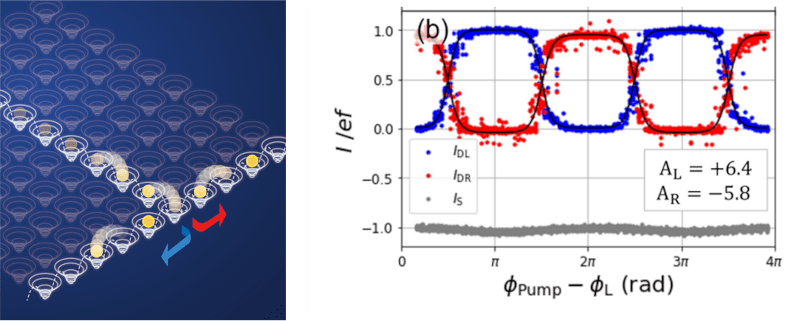

2次元量子ビットアレイ化に関する研究では、アレイ構造の試作・評価を通じ、1量子ビット、2量子ビットのスピン操作を行いました。スピン操作においてコヒーレンスをさらに改善させるスピン操作シーケンスについて検討し、スピン量子ビットにおいて、外界からのノイズを削減し、コヒーレンス時間を延伸させる量子ビット操作技術(CCD)を開発しました。また、2量子ビットのエンタングル状態を反映したCROTスペクトルを観測するとともに、CROTによる2量子ビット操作に成功しました(図2)。

量子ビット高精度制御・高感度読み出し回路の研究では、量子ビットの更なる高精度制御を目的に、位相低減方式であるポーラー変調方式の適用したマイクロ波発生回路チップの詳細設計を完了し、振幅変調を間欠動作させることで電力効率を改善、位相変調用のLOブロックにはサンプリングPLL方式を採用し位相低減を図りました。検討の結果、位相誤差成分であるジッタを137fsecから80fsecに低減できる見込みを得ました。

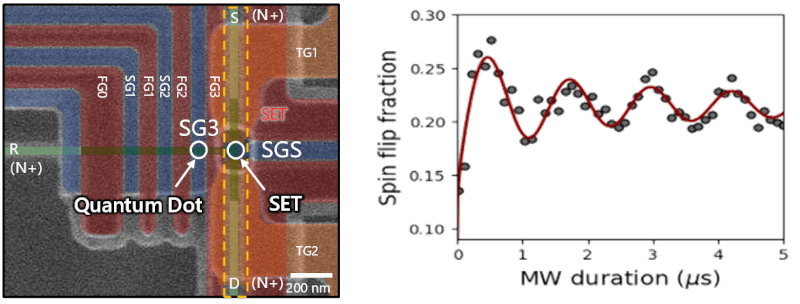

システムアーキテクチャの研究では、実験者支援のための量子オペレーティングシステムの拡張と、1量子ビットのラビ振動測定を自動化するワンクリック量子ビット測定システムを開発しました。分析処理の自動化手法を検討し、自動校正ライブラリの実装を完了した。天然シリコンデバイスを用いた実証試験の結果、自動校正によって測定時間を81%削減できることを確認するとともに、動作状態のトレーサビリティの確保と温度・デバイス特性変動時に対する自動校正機能を確認しました(図3)。

3. 今後の展開

FTQC実現に向けては常識にとらわれない様々なイノベーションが必要です。プロジェクト内外との連携によって、半導体技術を最大限に活用した量子ビットアレイ構造での量子ビット操作を実現し、さらにシステムレベル実装によってその高信頼・効率化に取り組みます。