成果概要

誤り耐性型量子コンピュータにおける理論・ソフトウェアの研究開発[1] クロスレイヤー協調設計モデルの開発と拡張

2024年度までの進捗状況

1. 概要

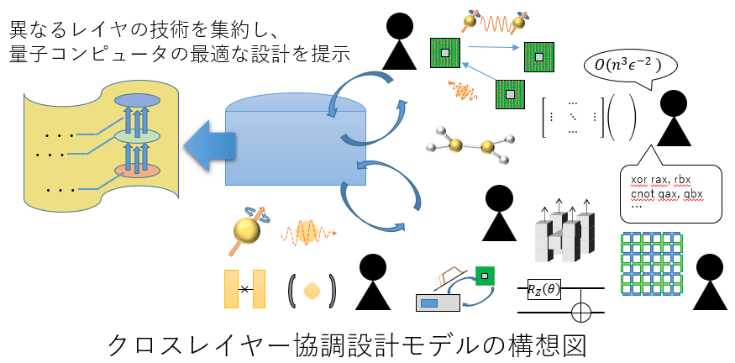

本研究開発項目では誤り耐性型量子コンピュータの設計を効率的に行う枠組みを構築します。通常の計算機には計算機の全体像を切り分け最適な設計を探求する種々の枠組みがありますが、誤り耐性型量子コンピュータにはこうした基盤が存在しません。このことが長期的な計画の立案や将来必要となる技術を先取りした開発を困難にしてきました。この問題を解決するため、本研究開発項目では誤り耐性型量子コンピュータで技術的なレイヤーを超えた協調設計を可能にするソフトウェア基盤「クロスレイヤー協調設計モデル」を構築します。このシステムを活用することで、誤り耐性型量子コンピュータの全体像を見据えた研究開発や、今後必要となる技術や要求性能を先読みした研究テーマの設定が可能となります。こうした取り組みはムーンショット目標6が目指す実用的な誤り耐性型汎用量子コンピュータの実現を計画的に行う上で重要となります。

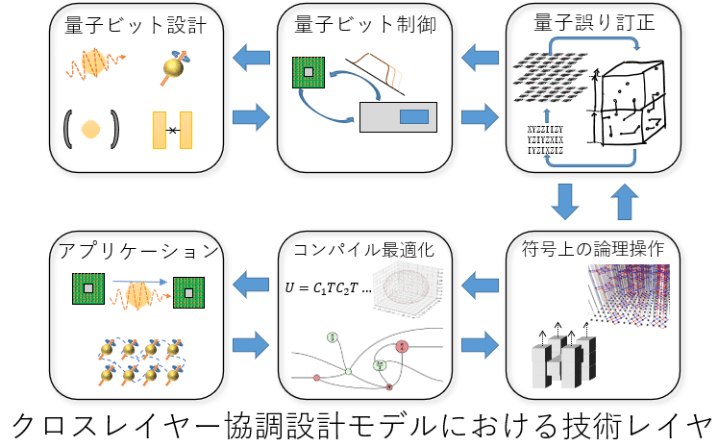

クロスレイヤー協調設計モデルの開発は以下のような手続きで進めます。まず、誤り耐性型量子コンピュータで必要となる要素を技術レイヤーごとに分解し、各レイヤーにおいて誤り耐性型量子コンピュータを構成するのに必要な構成要素を列挙したミニマルモデルを構築します。このモデルをもとに将来的な技術的課題を洗い出し、他項目の研究者と連携して課題を一つずつ解決します。そこで得られた結果をミニマルモデルに肉付けする形で還元し、複数の技術を組み合わせた現実的で洗練された量子コンピュータを設計する仕組みを組み上げます。

2. これまでの主な成果

- ① 実用的な超伝導量子計算機の要件の定量化

- ② 多様なデバイスへの横展開

- ③ 量子計算機の性能改善手法の提案

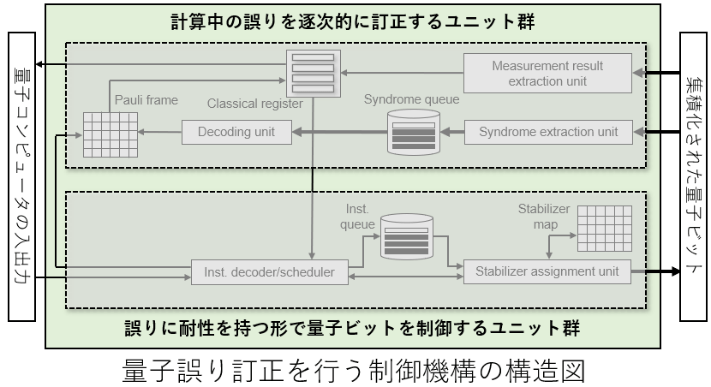

我々はまず量子計算機を構成する各レイヤーの技術要素を設計し評価するミニマルモデルを、超伝導量子ビットに向けて構築しました。これにより、実用的なタスクでの高速化の実現に必要なシステムの要件が定量的に明らかになりました(成果①)。この成果を、イオンや中性原子といった他の量子デバイスに横展開し、各種デバイスで目標の規模を明らかにするとともに、実用化への技術的課題を洗い出しました(成果②)。このようにして得られた技術課題を解決するべく、二つの方向性の研究を行いました。一つは長時間運転に伴う障害やデバイスの歩留まりなど各デバイスの拡張を阻害する問題を解決するアーキテクチャや制御手法の提案です。もう一つはハードウェアに適した命令セットやコンパイル手法の提案であり、プログラムの並列化やロードストア型設計の採用などにより、必要なデバイスの要求を大幅に緩和する手法を提案しました。この二つの取り組みを通し、実用化というゴールを定量的に見据えつつ、ハードウェアの拡張性の改善と必要なハードウェア要求の軽減を並行して実現しました(成果③)。

本課題の成果はレイヤーごとに網羅的に設計された評価基盤により可能となったものです。この成果は開発目標の具体化と性能の改善を可能にしただけでなく、技術的なレイヤーを跨いだ設計探索や、計算機、物理、回路設計分野などとの深い連携の実現にも貢献しています。

3. 今後の展開

引き続きソフトウェア、量子ビット、計算機の設計、回路集積化に取り組むグループとの連携を密にして、量子計算機の開発と性能改善の提案に取り組みます。また、現時点までに得られた最適化の手法や枠組みをソフトウェアの形で実装することで、誤り耐性量子計算の効率的な設計を加速する体制の実現に取り組みます。