成果概要

誤り耐性型量子コンピュータにおける理論・ソフトウェアの研究開発[4] 分散型構造を持つ誤り耐性型量子コンピュータの研究開発

2024年度までの進捗状況

1. 概要

本研究開発項目は、分散型構造を持つ誤り耐性量子コンピュータの可能性を理論的に探究することを担っています。この研究開発項目の達成により、分散構造を持つことで初めてスケールアップが可能な物理系を用いた量子計算や、モノリシックで開発が進む量子計算機の結合による更なるスケールアップの可能性が明らかになり、プロジェクトの目指す2050年の誤り耐性量子コンピュータの設計に指針を与えます。

この達成に向けては、離れた量子ビットとインターフェースで構成されるモジュールを通信ネットワークで結ぶ基本スキームの設計を始め、計算上の役割分担に基づく分散設計や、分散型に適合する量子誤り訂正符号や誤り耐性量子計算方式の同定が課題となっており、これらを挑戦的テーマとして取り組んでいます。従来とは異なり、クロスレイヤー協調設計と照らし合わせ、誤り耐性量子計算のみならず、量子通信の先端知識を導入することで、この課題の解決を目指しています。

2. これまでの主な成果

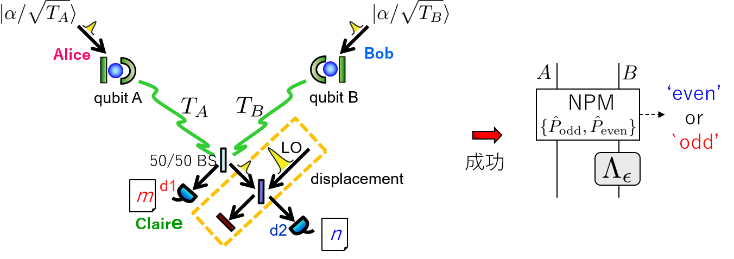

①コヒーレント状態伝送に基づく最適量子もつれ供給法[Azuma et al., PRA 105, 062432 (2022)]

分散型誤り耐性量子計算において基本となるのは、離れた量子ビットに対しCNOT演算を施すことで、これは離れた量子ビットに忠実度の高い量子もつれを供給することで実現されます。本成果では、量子ビットと量子もつれ状態にあるコヒーレント状態を、損失通信路を通じて伝送することで、離れた量子ビット対に一種類のエラーしかもたない量子もつれを供給する方式を考え、それらの方式が与え得る量子もつれの産出レートの原理限界を導出しました。その結果、遠隔非破壊パリティ測定に基づいて量子もつれを供給することが最適であることが明らかになりました。また、量子もつれ生成方式が十分効率的な場合、従来必要とされた「量子もつれ蒸留」なしに分散量子計算を行う方が効率的で優れた設計である可能性が見出されました。

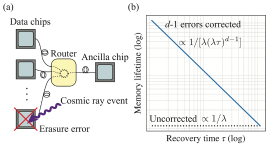

②チップレベルの破壊的な誤りに対する分散型量子誤り訂正手法を提案[Xu et al., PRL 129, 240502 (2022)]

大規模な量子コンピュータでは、飛来した宇宙線によるデータの破壊が問題となることが指摘されています。本成果では、分散型の構造を持つ量子コンピュータにおいて、複数のノードにまたがって量子誤り訂正を実行する方法を提案しました。複数の量子コンピュータチップを相互接続し、さらにデータ復元用のスペアノードを接続することで、ひとつのチップのあらゆるデータが破壊されたとしても、消失誤りの訂正技術により、データを回復できます。この手法により、壊滅的なデータ破壊の頻度を、例えば10秒に1回から1ヶ月に1回に削減できると見積もられます。

③メモリとプロセッサを分散したロードストア型量子計算機の提案 [Kobori et al., HPCA pp.304-320, (2025)]

通常の量子計算機では計算能力を持つレジスタと呼ばれる領域に全てのデータを保管するのが一般的です。この設計はシンプルですが、殆ど演算を行わない記憶領域にも計算能力を付与しなければならないため拡張性が低いという問題がありました。本成果では通常の計算機と同じく、量子計算機の機能を「計算能力を持つが拡張性の低いプロセッサ」と「計算能力はないが拡張性の高いメモリ」に分散させることで、実用的なアプリの実行に必要な量子ビットの数を約40%削減しました。この際、メモリにあるデータを計算に用いようとするとデータ通信の時間オーバーヘッドが生じますが、通常の計算機でいうキャッシュに似た構造を作りアクセスされやすいデータを即座に移動できるようにすることで、計算時間の増加を3%程度に抑えました。

3. 今後の展開

今後は、分散量子計算の候補となる物理系の特性を踏まえた基本スキームの現実的な理論モデルを作り込み、それを、分散型に適合する量子誤り訂正符号や誤り耐性量子計算方式に結合することで、分散型構造を持つ誤り耐性量子コンピュータの青写真を描きます。