成果概要

ナノファイバー共振器QEDによる大規模量子ハードウェア[2] ナノファイバー共振器QED方式に適した量子誤り訂正理論

2024年度までの進捗状況

1. 概要

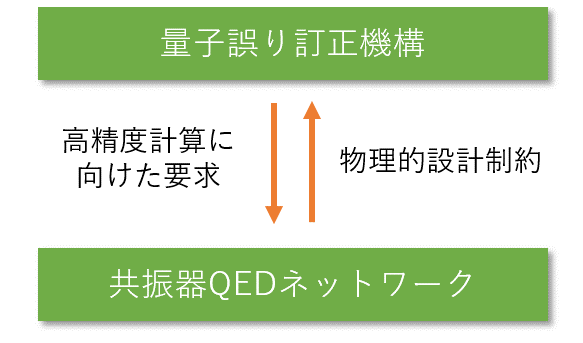

実用的な問題サイズの計算を高い精度で実行するためには、量子誤り訂正機構を備えた大規模な量子コンピュータが必要になります。量子誤り訂正機構とは、量子コンピュータのデータ保持を担う量子ビットに起こるエラーを随時訂正し、正しい情報を保持するための機構です。このような大規模化で考えなければいけないのが、物理プラットフォームの設計制約の中で構築可能な量子誤り訂正機構はどのようなものか、安定して量子誤り訂正機構が機能するためにはどのような精度のデバイスや制御装置が必要なのか、といった問題です。

本研究課題では、ナノファイバー共振器QED技術に基づく量子コンピュータ実装に合わせて上記問題を具体化し、最適な設計方針を打ち出すことを目的としています。

2. これまでの主な成果

これまで我々は、(1)共振器QEDに基づく量子計算デバイスの性能向上や最適設計の提案、(2)共振器QEDに基づく誤り訂正機構の構築に必要な条件の解明、に取り組んできました。

(1)では、共振器にトラップされた原子量子ビット間でゲートを行う際の共振器の最適な設計の解明や共振器QEDによる高性能光子生成器の提案、ゲート性能の理論的限界の評価を行いました。これらの研究は、デバイスの設計方針の指針を提示し、実験の精度をどこまで上げることが有益か、などの情報を実験側に提供しています。

(2)の研究は、安定した誤り訂正機構を構築するために実験でどのような条件を達成すべきかの指針を与えています。例えば、複数の共振器QEDネットワーク構造を考え(図2)、それぞれについて誤り耐性量子計算(FTQC)を実現するために必要な共振器性能を明らかにしました(図3)。さらに最近では、共振器QEDネットワーク特有のエラーに対する誤り訂正符号の復号処理の工夫によるFTQC条件の緩和や、FTQC条件が達成しやすい測定型量子計算方式の提案も行っています。

3. 今後の展開

今後は、引き続き量子デバイス性能を向上させる方法を検討するとともに、より現実に即した実験での制約を考慮したFTQC条件の検討やアーキテクチャの改善を行っていきます。共振器QEDに基づく誤り訂正機構搭載型の大規模量子計算に対して具体的な設計指針を与える研究は世界でもまだ類を見ないものであり、今後より一層注目されていくと考えています。