成果概要

超伝導量子回路の集積化技術の開発[3] 量子誤り訂正用エレクトロニクスの研究開発

2024年度までの進捗状況

1. 概要

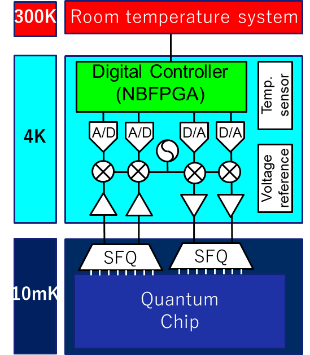

現在の超伝導量子ビット回路の典型的なセットアップでは、極低温に置かれた量子ビットチップと室温で動作するマイクロ波エレクトロニクスが、量子ビット一つ当たり1本以上の同軸ケーブルにより配線されています。しかし冷凍機のスペースや冷却能力の限界から、この方法では量子ビットのスケールアップに対応できません。本研究開発項目では、この問題を解決するために、なるべく量子ビット近傍で動作する量子ビット制御、読出しのエレクトロニクスを開発し、集積化に向けた配線のボトルネックを打破することを目的としています。

この開発においては、限られた冷凍機のスペースや冷却能力の中で、如何にして量子誤り訂正を効率的に実行する制御システムを実現するかが課題です。本研究開発項目では数十GHzでの動作が可能かつ超低消費電力回路である単一磁束量子回路、柔軟性に優れ高度な処理が可能かつ低消費電力なナノブリッジFPGAを軸に、それらが協調動作する低温エレクトロニクスシステムの開発を行います。

2. これまでの主な成果

①単一磁束量子回路による信号分配回路の14 mK動作を実証し、量子ビットモノリシックチップを完成

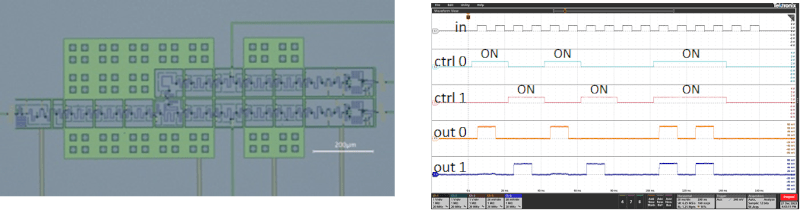

単一磁束量子(SFQ)回路は、これまで主に液体ヘリウム温度の4.2 Kでの動作を想定して設計されてきました。しかし本研究開発では量子ビットと同じ希釈冷凍機内の約10 mK環境での動作を目指しており、従来のSFQ回路をさらに低消費電力化する必要があります。デバイス特性の変化も考慮しつつ、SFQ回路に用いるジョセフソン接合の臨界電流値を1/10以下に低減すると同時に駆動電圧を下げることで、消費電力を1/50〜1/250に低減するための回路設計指針を策定し、これまでにSFQ回路の回路要素(配線や論理ゲートなど)を順次「セル」として設計用のライブラリに登録することを行ってきました。今年度は、開発したこの超低消費電力SFQセルライブラリを組み合わせて設計した信号分配回路を希釈冷凍機内で動作することを実証しました。また、この信号分配回路を複数の超伝導量子ビットに接続したモノリシックチップを完成させました。

②4K向けナノブリッジFPGAの製造を完了

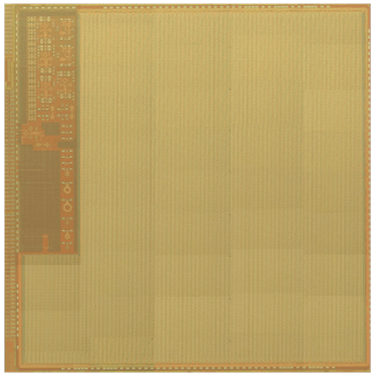

誤り訂正処理を行う際、多様な訂正アルゴリズムに対応するため低温で動作するFPGAの開発を行っています。FPGAは4 Kでの動作を想定しており、本研究プロジェクトでは、市販のCMOSベースのFPGAに比べて、室温にて1/4程度の消費電力であるナノブリッジFPGAを、低温で動作可能にすることを軸に開発を進めています。昨年度までに標準CMOSプロセス(65 nm)でのナノブリッジFPGAを混載した低温SOCの製造が完了し、低温用評価ボードに実装を行いました。FPGA部にテスト回路として積和演算回路を実装し、室温動作に比べて4Kの動作が低消費電力でできる結果を得ました。

3. 今後の展開

SFQ回路については、試作したモノリシックチップの評価を進め、SFQ信号分配回路を用いた複数の超伝導量子ビットのデジタル制御実験にチャレンジします。

ナノブリッジFPGAについては、製造したチップの低温での動作確認を行います。

また、このSFQ信号分配回路を、ナノブリッジFPGAを用いて制御する低温エレクトロニクス協調動作デモに取り組みます。