成果概要

超伝導量子回路の集積化技術の開発[2] 量子ビット集積ハードウエアシステムの研究開発

2024年度までの進捗状況

1. 概要

現在の超伝導量子ビット回路の典型的なセットアップでは、極低温に置かれた量子ビットチップと室温で動作するマイクロ波エレクトロニクスが、量子ビット一つ当たり1本以上の同軸ケーブルにより配線されています。しかし冷凍機のスペースや冷却能力の限界から、この方法では量子ビット数万個以上のスケールアップに対応できません。本研究開発テーマでは、この問題を解決するために、大容量、高冷却能力の希釈冷凍機や、コネクタレスの高密度配線といった量子チップ周辺ハードウェア技術を開発し、集積化に向けたボトルネックを打破することを目指しています。

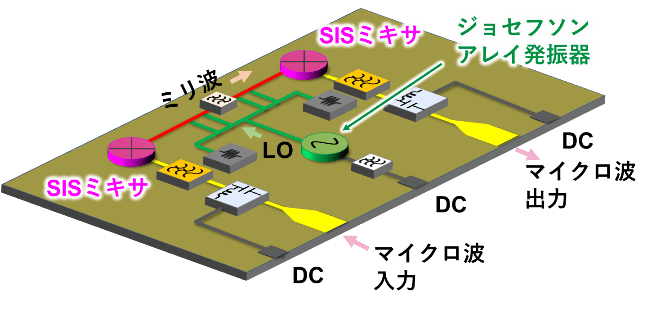

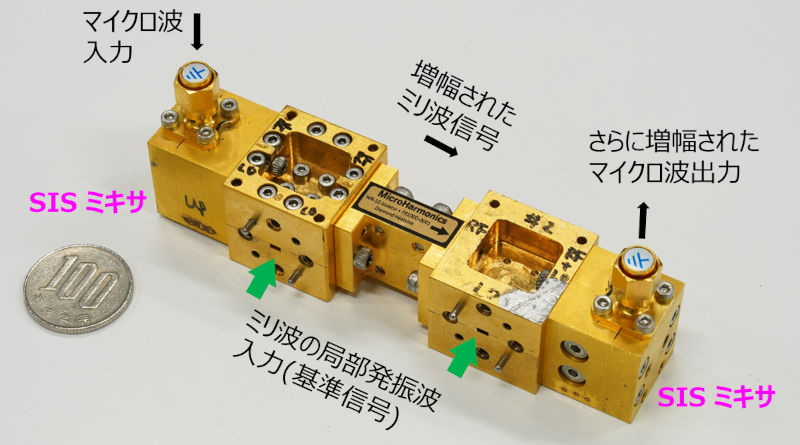

この開発では、如何にして量子ビット近傍で制御・信号処理を行い、異なる温度ステージ間の配線を削減出来るかが鍵になります。そのために、量子ビットの制御・読出しを行う信号処理回路と量子ビットチップがハイブリッド集積された“縦方向の集積化”量子ビットモジュールの開発を行っています。希釈冷凍機については、冷却システムを含めた純国産量子コンピュータの実証と、プロジェクト内での各要素技術のテストベッドとを目的にした、テストベッド希釈冷凍機を完成させました。

2. これまでの主な成果

①透過型実装構造の開発

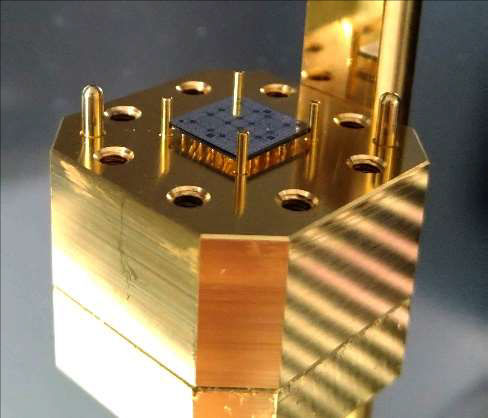

縦方向に積み重ねた構造の電気接続として垂直透過型実装モジュール実装構造の実現を目指し、設計・試作と評価実験を進めています。具体的には、基板貫通電極(TSV)を用いた基板内同軸構造の作成技術、基板間接続用微小インジウム半田バンプ作成技術、超伝導電極作成技術を進めています。まず、積層の評価用チップとこれを3枚6層(量子ビット基板、読出し基板、上部配線基板を想定)積層するフリップチップ実装技術を開発しました。さらに、積層チップによる垂直透過型実装モジュールを収納する磁気遮蔽の製作、極低温電気特性を評価するための冷凍機と電気特性計測装置環境を構築しました。この極低温測定システムを用いて、2枚4層の積層されたテスト積層チップにおいて、1ギガヘルツから10ギガヘルツの間において1dB以下の十分に低い挿入損失の伝送実験に成功しました。

②テストベッド希釈冷凍機の開発

100 mKでの冷凍能力400 μWをテストベッド希釈冷凍機の性能目標とし、設計、組立、試験をアルバック社内で実施しました。社内試験にて運転パラメータの最適化と、外部から侵入する熱への対策を完了させることで、最終的に690 μWと、目標性能を十分にクリアすることが確認できました※1。冷凍性能を達成後、純国産量子コンピュータとしての最終組立を担当する大阪大学への移設を年度内に完了させ、マイルストーンに掲げた目標を達成しました。

※1移設完了後2025年4月の試験では780 μWの冷凍能力を確認できました。

3. 今後の展開

透過型実装構造については、垂直透過型実装モジュールの高周波電気特性の評価環境を引き続き整えるとともに、量子ビット基板・読出し回路基板を積層した3基板6層の回路構造を設計、試作し評価実験に進む予定です。

テストベッド希釈冷凍機については、純国産量子コンピュータとして大阪・関西万博でクラウド公開します。また、この運用を通し、長期間の安定稼働が必要な量子コンピュータ用希釈冷凍機としての信頼性を確立させます。