成果概要

誤り耐性型大規模汎用光量子コンピュータの研究開発[3] 導波路光パラメトリック増幅器および光量子導波路回路に関する研究開発

2024年度までの進捗状況

1. 概要

2024年度は、前年度の成果を踏まえて、導波路型光パラメトリック増幅器(Optical Parametric Amplifier: OPA)と光導波路技術を中核としたスクイーズド光源の高性能化を目指した取り組みを実施しました。広帯域かつ高スクイージングレベルの光源の開発を軸に、OPAの評価や、さらには空間モード最適化に至る一連の実験を通じて、次世代量子光デバイスとしての基盤確立を進めました。一方、将来的な光量子情報処理系の集積化に向けた検討として、石英系平面光波回路(Planar Lightwave Circuit: PLC)を活用した量子もつれ光子対生成回路のモジュール化や特性評価も展開し、将来に集積化に向けて課題の抽出を行いました。

2. これまでの主な成果

(1)導波路光パラメトリック増幅器による広帯域・高レベルスクイーズド光源の検討

この課題では、導波路型OPAによるスクイーズド光の生成と性能向上に向け、以下の2点に取り組みました。

- a. 短尺化した導波路光パラメトリック増幅器による広帯域・高レベルスクイーズド光生成の検討

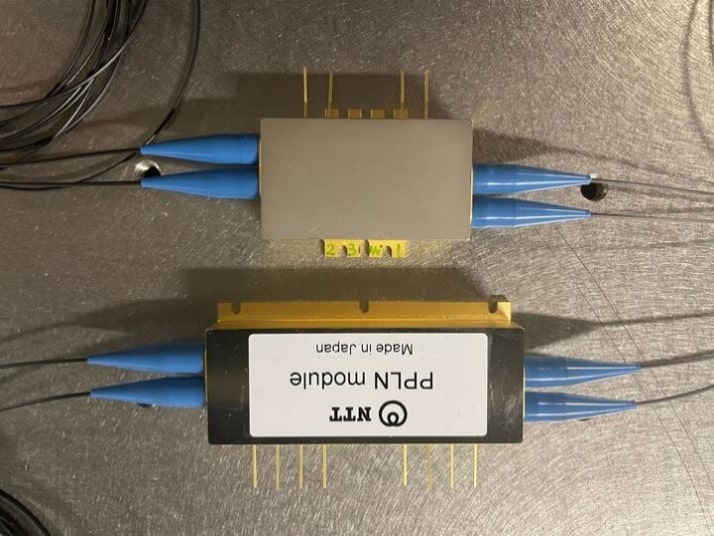

- OPAと光スペクトルアナライザを組み合わせた全光型測定法を適用しました(図2)。さらに、OPAの利得が有限である場合の利得依存性を反映した理論モデルを構築し、シミュレーションによって理論値と測定値の差異を解析しました(図3)。加えて、OPAを2段直列に接続して利得を制御し、光強度比を測定した結果、理論モデルとの良好な一致が得られ、測定手法の妥当性を確認しました。

(a)計算値、(b)実測値

- b. 実機のための空間モード向上検討

- 理化学研究所で構築された光量子コンピュータ実機への応用に向けて、OPA出射光の空間モード特性を評価しました。専用の測定系を構築し、設計パラメータとモード形状との関係を分析した結果、XY対称性99%以上のモード特性を有するOPAを再現可能とする設計指針を確立しました。

- この指針に基づいて製作した15台すべてにおいて高い空間モード対称性が得られ、実機実装に向けた信頼性の高いデバイス設計の基盤が整いました。

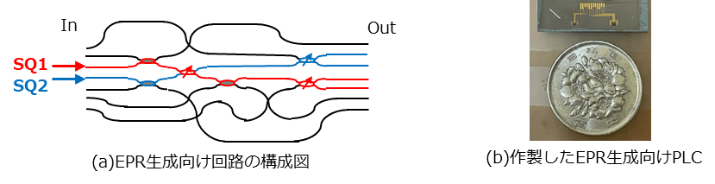

(2)石英系平面光波回路によるEPRペア生成回路のモジュール評価の検討

将来的な光量子情報処理の集積化に向けて基本要素である量子もつれ光子対生成回路として石英系平面光波回路(PLC)を作製しました。作製したチップに入出力用のファイバアレイ(FA)を接続してモジュール化を行い、回路チップとしては損失が0.2 dBの十分良好な特性が得られているものの、モジュール化により過剰損失1dBが発生していることを確認しました。要因分析により組み立て時の誤差であることを明らかにし、今後、損失低減が可能であることを確認しました。

3. 今後の展開

今後は以下の方向性に基づき、量子デバイス技術のさらなる高度化と社会実装を見据えた応用展開を進めます。

- 空間モード最適化設計の高度化等と併せて作製技術を高めていきます。

- 光接続損失のさらなる低減を図ります。

- 光量子コンピュータ実機への信頼性の高いデバイス供給体制を整備し、プロジェクト全体の実装の加速に貢献します。