不揮発性SRAM

~エッジコンピューティングの革新的低消費電力技術~

菅原 聡(東京工業大学)

発明のポイント

不揮発記憶を利用して待機時電力を削減する不揮発性SRAM(NV-SRAM)技術

ロジックシステムの無駄な動作時/待機時電力を削減できる超低電圧リテンションSRAM(ULVR-SRAM)技術

発明の概要

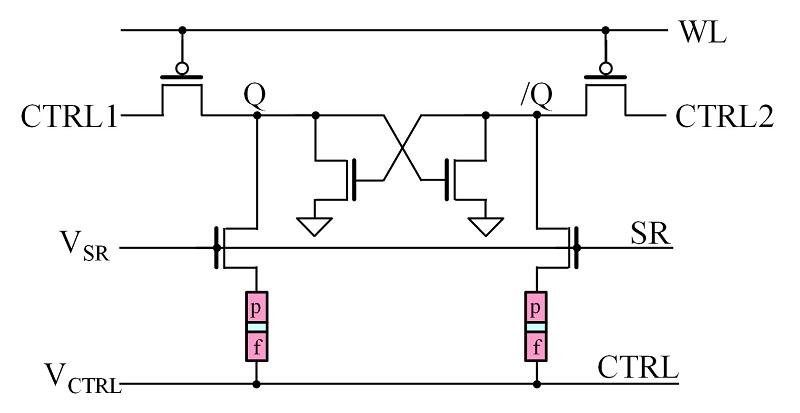

・強磁性トンネル接合(MTJ)の電気的分離

- SRAM動作

- MTJ電気的分離(6Tセル同等性能)

- 電源遮断

- MTJ書込み

- 電源復帰

- MTJから双安定回路へ自動データ復帰

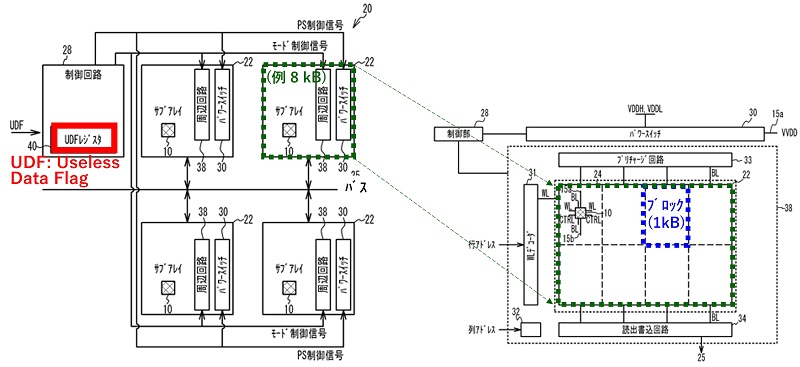

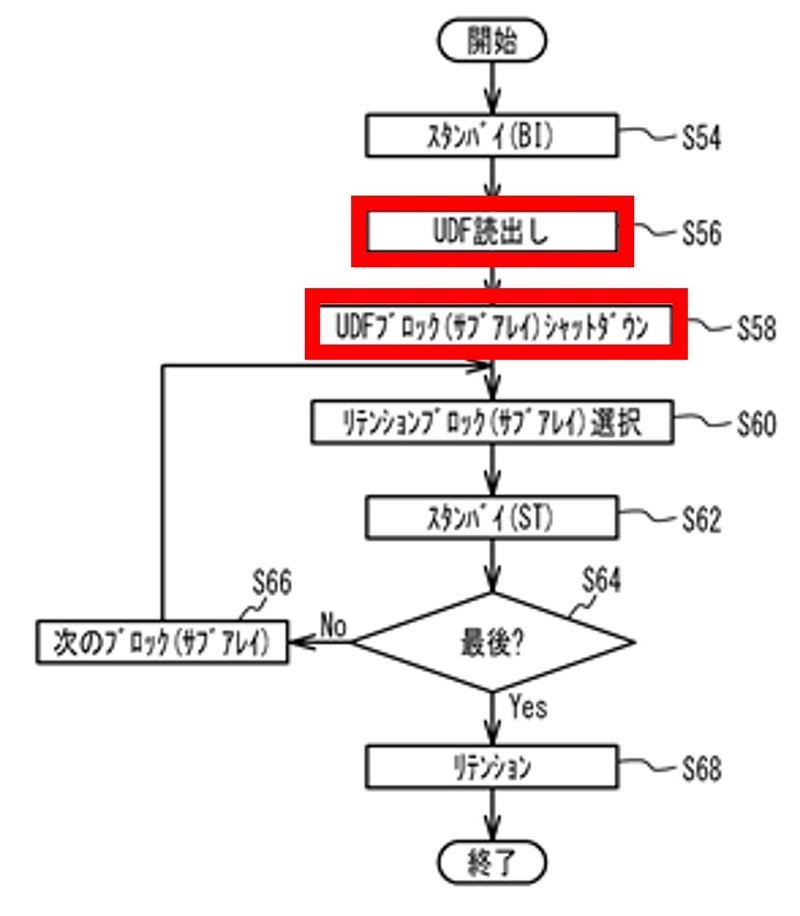

・NV-SRAMのブロック毎シャットダウン

Useless Data (長期間使われなかったデータ・使用頻度の少ないデータ等)のみのブロックに対して立てたフラグを、サブアレイ外の制御回路に格納

- →該ブロックをシャットダウン後、該ブロック以外のブロックを低電圧保持

- →低電力化

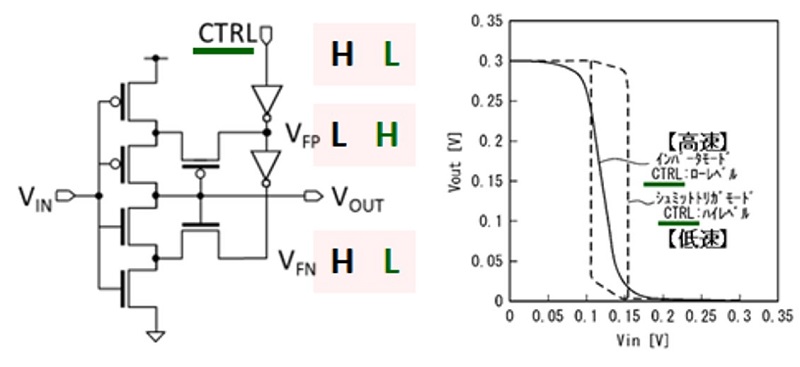

・電源電圧VVDDによる動作モードの切替え

- 1 V

- 6T-SRAM 同等動作

- 0.4 V

- 消費エネルギー極小電圧(Vmin)動作

- 0.15 V

- 超低電圧リテンション(Power Gating)

従来技術との比較・優位性

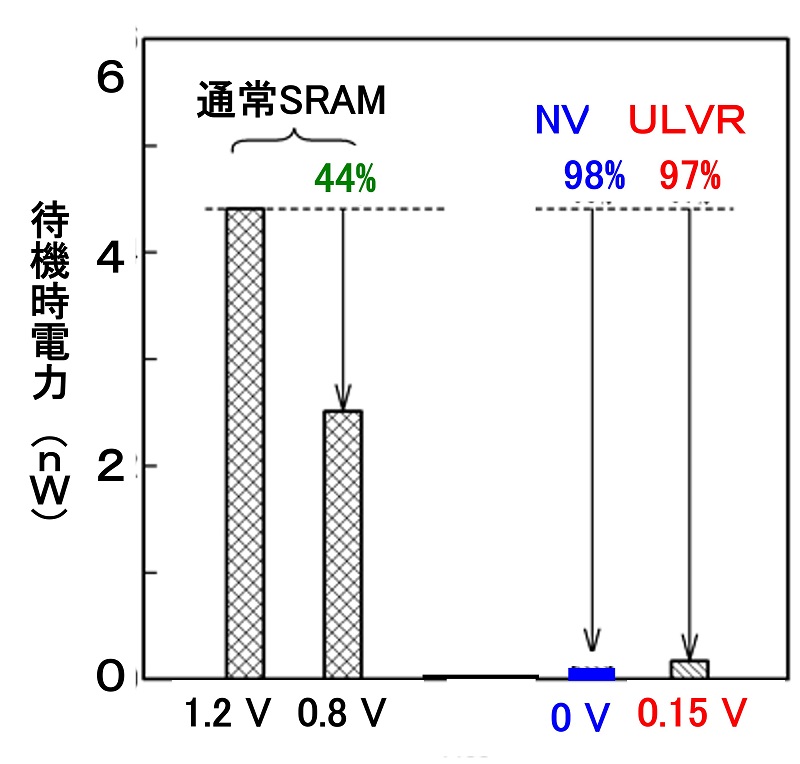

【通常SRAMに比較して 待機時電力を徹大幅に削減】

- 通常SRAM

- 電圧を0.8 Vまで下げても待機時電力を44%しか減らせない。

- NV-SRAM

- 電源遮断により待機時電力は通常SRAM動作時から98%減。

- ULVR-SRAM

- 電源電圧を0.15 Vまで下げることにより、待機時電力は通常SRAM動作時から97%減。CPUスリープ時 電池寿命が十数倍に増。

想定される用途

- ◎ 医療、介護、ヘルスケア他向けAIマイクロプロセッサ/コントローラ、 システムオンチップ

ライセンス可能な特許

- 1. 発明の名称:電子回路

登録番号:特許第6830681号(504KB) - 2. 発明の名称:電子回路

登録番号:特許第6993681号(335KB) - 3. 発明の名称:電子回路

国際公開番号:WO2016/158691

登録番号:特許第6553713号(524KB)、米国10355676(2.03MB) - 4. 発明の名称:記憶回路

国際公開番号:WO2016/024527

登録番号:特許第6230204号(906KB)、米国10049740(2.97MB) - 5. 発明の名称:電子回路

国際公開番号:WO2020/241000

登録番号:特許第7430407号(915KB)、米国12165697(5.33MB) - 6. 発明の名称:双安定回路および電子回路

国際公開番号:WO2021/161808

登録番号:特許第7430425号(681KB)、米国12183392(5.17MB)