(19)日本国特許庁(JP)

# (12) 特 許 公 報(B2)

(11)特許番号

特許第7430407号 (P7430407)

(45)発行日 令和6年2月13日(2024.2.13)

(24)登録日 令和6年2月2日(2024.2.2)

(51) Int. C1. F I

G11C 11/417 (2006.01) G11C 11/417 100 H03K 3/356 (2006.01) H03K 3/356 B G11C 14/00 (2006.01) G11C 14/00 230

請求項の数 14 (全 70 頁)

(21)出願番号 特願2021-522653(P2021-522653) (86)(22)出願日 令和2年3月18日(2020, 3, 18)

(86)国際出願番号 PCT/JP2020/012099 (87)国際公開番号 W02020/241000

(32)優先日 令和1年5月30日(2019.5.30)

(33)優先権主張国・地域又は機関 日本国(JP)

(33)優先権主張国・地域又は機関

日本国(JP)

(73)特許権者 503360115

国立研究開発法人科学技術振興機構 埼玉県川口市本町四丁目1番8号

(74)代理人 100087480

弁理士 片山 修平

(72)発明者 菅原 聡

東京都目黒区大岡山2-12-1 国立大

学法人東京工業大学内

(72)発明者 北形 大樹

東京都目黒区大岡山2-12-1 国立大

学法人東京工業大学内

(72)発明者 山本 修一郎

東京都目黒区大岡山2-12-1 国立大

学法人東京工業大学内

最終頁に続く

### (54) 【発明の名称】電子回路

# (57) 【特許請求の範囲】

# 【請求項1】

各々のメモリセルが、伝達特性にヒステリシスを実質的に有さない第1モードと伝達特性にヒステリシスを有する第2モードとが切り替わる第1インバータ回路および第2インバータ回路を各々備え、前記第1インバータ回路の出力ノードおよび入力ノードは前記第2インバータ回路のそれぞれ入力ノードおよび出力ノードに接続された双安定回路を備える複数のメモリセルを有するセルアレイと、

前記複数のメモリセルのうち保持しなくてもよいデータを記憶する1または複数の第1 メモリセルを電源遮断した後、前記複数のメモリセルのうち残りの1または複数の第2メ モリセル内の双安定回路を前記第2モードとし、前記第2モードを維持した状態で前記1 または複数の第2メモリセル内の双安定回路に、データをリードおよび/またはライトするときに双安定回路に供給される第1電源電圧より低く前記第2モードの双安定回路がデータを保持できる第2電源電圧を供給する制御回路と、

を備える電子回路。

### 【請求項2】

前記セルアレイは、各々のブロックが少なくとも2つのメモリセルを含む複数のブロックに分割され、

前記制御回路は、前記複数のブロックから保持しなくてもよいデータを記憶する1または複数の第1ブロックを抽出し、前記1または複数の第1ブロックを電源遮断した後、前記複数のブロックのうち残りの1または複数の第2ブロック内の双安定回路を前記第2モ

ードとし、前記第2モードを維持した状態で前記1または複数の第2プロック内の双安定 回路に前記第2電源電圧を供給する請求項1に記載の電子回路。

#### 【請求項3】

前記制御回路は、前記1または複数の第2プロック内の双安定回路を前記第2モードと する前に、前記1または複数の第2ブロックに、前記第1電源電圧より低くかつ前記第2 電源電圧より高く前記第1モードの双安定回路がデータを保持できる第3電源電圧を供給 する請求項2に記載の電子回路。

# 【請求項4】

前記制御回路は、前記1または複数の第2ブロック内の双安定回路に前記第3電源電圧 を供給した状態で前記1または複数の第2ブロック内の双安定回路を前記第2モードとす る請求項3に記載の電子回路。

# 【請求項5】

前記1または複数の第2ブロックは複数の第2ブロックであり、

前記制御回路は、前記複数の第2ブロックのうち1または複数の第3ブロックの双安定 回路に前記第3電源電圧を供給した状態で前記1または複数の第3ブロック内の双安定回 路を前記第2モードとし、前記1または複数の第3ブロック内の双安定回路を前記第2モ ードとした状態で前記第2電源電圧を供給し、その後、前記複数の第2ブロックのうち前 記1または複数の第3ブロックとは別の1または複数の第4ブロックの双安定回路に前記 第3電源電圧を供給した状態で前記1または複数の第4ブロック内の双安定回路を前記第 2 モードとし、前記 1 または複数の第 4 ブロック内の双安定回路を前記第 2 モードとした 状態で前記第2電源電圧を供給する請求項3に記載の電子回路。

### 【請求項6】

前記1または複数の第2ブロックは複数の第2ブロックであり、

前記制御回路は、前記複数の第2ブロック内の双安定回路に前記第3電源電圧を供給し た状態で前記複数の第2ブロック内の双安定回路を前記第2モードとした後、前記複数の 第2ブロック内の双安定回路を前記第2モードとした状態で前記第2電源電圧を供給する 請求項3に記載の電子回路。

# 【請求項7】

前記セルアレイの外に設けられ、外部回路から受信した前記保持しなくてもよいデータ を記憶するブロックを示す情報を記憶する記憶回路を備え、前記制御回路は、前記情報に 基づき、前記保持しなくてもよいデータを記憶する前記1または複数の第1ブロックを抽 出する請求項2から6のいずれか一項に記載の電子回路。

# 【請求項8】

前記第1インバータ回路および前記第2インバータ回路は、

ソースが第1電源線に接続され、ドレインが出力ノードに接続され、ゲートが入力ノー ドに接続された第1導電型のチャネルの第1FETと、

ソースが前記第1電源線との間に電源電圧が供給される第2電源線に接続され、ドレイ ンが中間ノードに接続され、ゲートが前記入力ノードに接続された前記第1導電型と反対 の第2導電型のチャネルの第2FETと、

ソースが前記中間ノードに接続され、ドレインが前記出力ノードに接続され、ゲートが 前記入力ノードに接続された前記第2導電型のチャネルの第3FETと、

ソースおよびドレインの一方が前記中間ノードに接続され、前記ソースおよび前記ドレ インの他方が制御ノードに接続された第4FETと、

### を各々備え、

前記第1インバータ回路の第4FETのゲートは、前記第1インバータ回路の入力ノー ド、出力ノード、前記第2インバータ回路の入力ノードおよび出力ノードのいずれか1つ のノードに接続され、

前記第2インバータ回路の第4FETのゲートは、前記第2インバータ回路の入力ノー ド、出力ノード、前記第1インバータ回路の入力ノードおよび出力ノードのいずれか1つ のノードに接続され、

10

20

30

40

前記第1インバータ回路の第4FETは、ゲートが前記第1インバータ回路の出力ノードまたは前記第2インバータ回路の入力ノードに接続されているとき前記第2導電型のチャネルのFETであり、ゲートが前記第1インバータ回路の入力ノードまたは前記第2インバータ回路の出力ノードに接続されているとき前記第1導電型のチャネルのFETであり、

前記第2インバータ回路の第4FETは、ゲートが前記第2インバータ回路の出力ノードまたは前記第1インバータ回路の入力ノードに接続されているとき前記第2導電型のチャネルのFETであり、ゲートが前記第2インバータ回路の入力ノードまたは前記第1インバータ回路の出力ノードに接続されているとき前記第1導電型のチャネルのFETである請求項1から7のいずれか一項に記載の電子回路。

#### 【請求項9】

前記第1インバータ回路および前記第2インバータ回路の制御ノードには定バイアスが印加され、前記第1インバータ回路および前記第2インバータ回路は、前記第1電源電圧が供給されるとき前記第1モードとなり、前記第2電源電圧が供給されるとき前記第2モードとなる請求項8に記載の電子回路。

#### 【請求項10】

各々のメモリセルが、データを揮発的に記憶する双安定回路と、前記双安定回路に記憶されたデータを不揮発的にストアし、不揮発的にストアされたデータを前記双安定回路にリストアする不揮発性素子と、を備える複数のメモリセルを有するセルアレイと、

前記セルアレイを電源遮断するときに、前記複数のメモリセルのうち揮発的に書き換えられているかいないかにかわらず不揮発的にストアしなくてもよいデータを揮発的に記憶する1または複数の第1メモリセルを電源遮断し、前記1または複数の第1メモリセルを電源遮断した後前記複数のメモリセルのうち残りの1または複数の第2メモリセルにおいて双安定回路に揮発的に記憶されたデータを前記不揮発性素子にストアするストア動作を行い、その後前記1または複数の第2メモリセルを電源遮断する制御回路と、を備える電子回路。

# 【請求項11】

前記セルアレイは、各々のブロックが少なくとも 2 つのメモリセルを含む複数のブロックに分割され、

前記制御回路は、前記セルアレイを電源遮断するときに、前記複数のブロックからブロック内のメモリセルが揮発的に書き換えられているかいないかにかわらず不揮発的にストアしなくてもよいデータを揮発的に記憶する1または複数の第1ブロックを抽出し、前記1または複数の第1ブロックを電源遮断し、前記1または複数の第1ブロックを電源遮断した後前記複数のブロックのうち残りの1または複数の第2ブロック内のメモリセルにおいてストア動作を行い、ストア動作の終了した第2ブロックを電源遮断する請求項10に記載の電子回路。

#### 【請求項12】

前記制御回路は、前記1または複数の第1ブロックを全て電源遮断した後、前記1または複数の第2ブロック内のメモリセルにおいてストア動作を行う請求項<u>11</u>に記載の電子回路。

#### 【請求項13】

前記セルアレイの外に設けられ、外部回路から受信した前記1または複数の第1ブロックを示す情報を記憶する記憶回路を備え、

前記制御回路は、前記情報に基づき、前記1または複数の第1ブロックを抽出する請求項11または12に記載の電子回路。

#### 【請求項14】

前記制御回路は、前記複数のブロックから、ブロック内のメモリセルが揮発的に書き換えられているかいないかにかわらず不揮発的にストアしなくてもよいデータを揮発的に記憶するブロックと、ブロック内のいずれのメモリセルも揮発的に書き換えられていないブロックと、を前記1または複数の第1ブロックとして抽出し、前記1または複数の第1ブ

10

20

30

40

ロックを電源遮断し、前記1または複数の第1ブロックを電源遮断した後前記複数のブロックのうち残りの1または複数の第2ブロック内のメモリセルにおいてストア動作を行い、ストア動作の終了した第2ブロックを電源遮断する請求項<u>11</u>から<u>13</u>のいずれか一項に記載の電子回路。

【発明の詳細な説明】

#### 【技術分野】

# [0001]

本発明は、<u>電子回路</u>に関し、例え<u>ば双安定回路</u>を有する複数のメモリセルを備えた電子 回路に関する。

#### 【背景技術】

[0002]

不揮発性素子を用いず、CMOS(Complementary Metal Oxide Semiconductor)のみから構成されたインバータを用い、擬似不揮発性SRAM(VNR-SRAM)を構成できることが知られている(例えば特許文献 1)。VNR-SRAMでは、超低電圧(ULV)リテンションが可能なシュミットトリガ(ST)モードと通常の電圧でSRAMと同等の回路性能を実現できるブーステッドインバータ(BI)モードとを切り替え可能なデュアルモードインバータを用いる。このULVリテンションをパワーゲーティング(PG)に用いることができる。

# [0003]

双安定回路と不揮発性素子を有するメモリセル(NV-SRAM)を用いた記憶回路が知られている(例えば特許文献2)。NV-SRAMでは双安定回路のデータを不揮発性素子にストアし、不揮発性素子のデータを双安定回路にリストアする。

# [0004]

NV-SRAMにおいて、通常のSRAMのように双安定回路にデータをライト(書き込み)およびリード(読み出し)するSRAM(Static Random Access Memory)動作、電源電圧を低くしてデータを保持するスリープ動作、双安定回路のデータを不揮発性素子にストアするストア動作、メモリセルの電源を遮断するシャットダウン動作および不揮発記憶素子にストアされたデータを双安定回路に書き戻すリストア動作を行なう記憶回路が知られている(例えば特許文献3)。ストア、シャットダウンおよびリストア動作を用いることでセルの記憶内容を失うことなく、電源遮断によるパワーゲーティング(PG)が可能になる。

#### [0005]

双安定回路に記憶されているデータと、不揮発性素子にストアされているデータが一致する場合、ストアをスキップする制御(ストアフリー動作)を行なう記憶回路が知られている(例えば特許文献 4)。セルアレイを複数のブロックに分割し、ストア動作が終了したブロックの電源を遮断することが知られている(例えば特許文献 5)。

#### 【先行技術文献】

# 【特許文献】

### [0006]

【特許文献1】国際公開第2016/158691号

【特許文献2】国際公開第2009/028298号

【特許文献3】国際公開第2013/172066号

【特許文献4】国際公開第2013/172065号

【特許文献 5 】国際公開第 2 0 1 6 / 0 2 4 5 2 7 号

# 【発明の概要】

【発明が解決しようとする課題】

# [0007]

特許文献1のVNR-SRAMでは、ULVリテンションすることで、セルの記憶内容を失うことなく、待機時電力を削減することができる。これにより、消費電力を抑制できる。しかし、VNR-SRAMでは、PG後に不要なデータについてもULVリテンショ

10

20

30

40

20

30

40

50

ンするため、PG時のリーク電流によるエネルギー消費の削減率が制約される。また、PG時にすべてのセルについてSTモードとBIモードの切り替えを行う。このため、モード切り替えのための時間(レイテンシ)やエネルギーオーバーヘッドが生じる。これらリーク電流、モード切り替えのためのエネルギー消費は損益分岐時間(BET: Break eventime)の増大を招く。

### [0008]

また、特許文献4および5のNV-SRAMでは、ストアフリー動作を行うことで,ストア不要なデータのストアを回避できる。しかし、セルアレイの記憶容量が大きくなると、ストア動作を待機するブロックに生じるリーク電流による消費電力によって、ストアフリーの効果は抑制される。また、ストアフリー動作では、PGに不要なデータであっても通常動作時に書き換えのあったデータに対してはストア動作を行ってしまう。このため、不要なエネルギーオーバーヘッドやストアに要するレイテンシのオーバヘッドを生じてしまう。

### [0009]

本発明は、上記課題に鑑みなされたものであり、消費電力および消費エネルギーを抑制することを目的とする。

## 【課題を解決するための手段】

### [0010]

本発明は、各々のメモリセルが、伝達特性にヒステリシスを実質的に有さない第1モードと伝達特性にヒステリシスを有する第2モードとが切り替わる第1インバータ回路および第2インバータ回路を各々備え、前記第1インバータ回路の出力ノードおよび入力ノードは前記第2インバータ回路のそれぞれ入力ノードおよび出力ノードに接続された双安定回路を備える複数のメモリセルを有するセルアレイと、前記複数のメモリセルのうち保持しなくてもよいデータを記憶する1または複数の第1メモリセルを電源遮断した後、前記複数のメモリセルのうち残りの1または複数の第2メモリセル内の双安定回路を前記第2モードとし、前記第2モードを維持した状態で前記1または複数の第2メモリセル内の双安定回路に、データをリードおよび/またはライトするときに双安定回路に供給される第1電源電圧より低く前記第2モードの双安定回路がデータを保持できる第2電源電圧を供給する制御回路と、を備える電子回路である。

### [0011]

上記構成において、前記セルアレイは、各々のブロックが少なくとも2つのメモリセルを含む複数のブロックに分割され、前記制御回路は、前記複数のブロックから<u>保持しなくてもよいデータを記憶する</u>1または複数の第1ブロックを抽出し、前記1または複数の第1ブロックを電源遮断した後、前記複数のブロックのうち残りの1または複数の第2ブロック内の双安定回路を前記第2モードとし、前記第2モードを維持した状態で前記1または複数の第2ブロック内の双安定回路に前記第2電源電圧を供給する構成とすることができる。

# [0012]

上記構成において、前記制御回路は、前記1または複数の第2ブロック内の双安定回路を前記第2モードとする前に、前記1または複数の第2ブロックに、前記第1電源電圧より低くかつ前記第2電源電圧より高く前記第1モードの双安定回路がデータを保持できる第3電源電圧を供給する構成とすることができる。

# [0013]

上記構成において、前記制御回路は、前記1または複数の第2ブロック内の双安定回路に前記第3電源電圧を供給した状態で前記1または複数の第2ブロック内の双安定回路を前記第2モードとする構成とすることができる。

# [0014]

上記構成において、前記1または複数の第2ブロックは複数の第2ブロックであり、前記制御回路は、前記複数の第2ブロックのうち1または複数の第3ブロックの双安定回路に前記第3電源電圧を供給した状態で前記1または複数の第3ブロック内の双安定回路を

20

30

40

50

前記第2モードとし、前記1または複数の第3ブロック内の双安定回路を前記第2モードとした状態で前記第2電源電圧を供給し、その後、前記複数の第2ブロックのうち前記1または複数の第3ブロックとは別の1または複数の第4ブロックの双安定回路に前記第3電源電圧を供給した状態で前記1または複数の第4ブロック内の双安定回路を前記第2モードとした状態で前記第2電源電圧を供給する構成とすることができる。

#### [0015]

上記構成において、前記1または複数の第2ブロックは複数の第2ブロックであり、前記制御回路は、前記複数の第2ブロック内の双安定回路に前記第3電源電圧を供給した状態で前記複数の第2ブロック内の双安定回路を前記第2モードとした後、前記複数の第2ブロック内の双安定回路を前記第2モードとした状態で前記第2電源電圧を供給する構成とすることができる。

### [0016]

上記構成において、前記セルアレイの外に設けられ、外部回路から受信した前記<u>保持しなくてもよいデータを記憶する</u>ブロックを示す情報を記憶する記憶回路を備え、前記制御回路は、前記情報に基づき、前記<u>保持しなくてもよいデータを記憶する</u>前記1または複数の第1プロックを抽出する構成とすることができる。

#### [0017]

上記構成において、前記第1インバータ回路および前記第2インバータ回路は、ソース が第1電源線に接続され、ドレインが出力ノードに接続され、ゲートが入力ノードに接続 された第1導電型のチャネルの第1FETと、ソースが前記第1電源線との間に電源電圧 が供給される第2電源線に接続され、ドレインが中間ノードに接続され、ゲートが前記入 カノードに接続された前記第1導電型と反対の第2導電型のチャネルの第2FETと、ソ ースが前記中間ノードに接続され、ドレインが前記出力ノードに接続され、ゲートが前記 入力ノードに接続された前記第2導電型のチャネルの第3FETと、ソースおよびドレイ ンの一方が前記中間ノードに接続され、前記ソースおよび前記ドレインの他方が制御ノー ドに接続された第4FETと、を各々備え、前記第1インバータ回路の第4FETのゲー トは、前記第1インバータ回路の入力ノード、出力ノード、前記第2インバータ回路の入 カノードおよび出力ノードのいずれか1つのノードに接続され、前記第2インバータ回路 の第4FETのゲートは、前記第2インバータ回路の入力ノード、出力ノード、前記第1 インバータ回路の入力ノードおよび出力ノードのいずれか1つのノードに接続され、前記 第1インバータ回路の第4FETは、ゲートが前記第1インバータ回路の出力ノードまた は前記第2インバータ回路の入力ノードに接続されているとき前記第2導電型のチャネル のFETであり、ゲートが前記第1インバータ回路の入力ノードまたは前記第2インバー 夕回路の出力ノードに接続されているとき前記第1導電型のチャネルのFETであり、前 記第2インバータ回路の第4FETは、ゲートが前記第2インバータ回路の出力ノードま たは前記第1インバータ回路の入力ノードに接続されているとき前記第2導電型のチャネ ルのFETであり、ゲートが前記第2インバータ回路の入力ノードまたは前記第1インバ ータ回路の出力ノードに接続されているとき前記第1導電型のチャネルのFETである構 成とすることができる。

#### [0018]

上記構成において、前記第1インバータ回路および前記第2インバータ回路の制御ノードには定バイアスが印加され、前記第1インバータ回路および前記第2インバータ回路は、前記第1電源電圧が供給されるとき前記第1モードとなり、前記第2電源電圧が供給されるとき前記第2モードとなる構成とすることができる。

#### [0019]

本発明は、ソースが第1電源線に接続され、ドレインが出力ノードに接続され、ゲートが入力ノードに接続された第1導電型のチャネルの第1FETと、ソースが前記第1電源線との間に電源電圧が供給される第2電源線に接続され、ドレインが中間ノードに接続され、ゲートが前記入力ノードに接続された前記第1導電型と反対の第2導電型のチャネル

20

30

40

50

の第2FETと、ソースが前記中間ノードに接続され、ドレインが前記出力ノードに接続され、ゲートが前記入力ノードに接続された前記第2導電型のチャネルの第3FETと、ソースおよびドレインの一方が前記中間ノードに接続され、前記ソースおよび前記ドレインの他方が制御ノードに接続された前記第1導電型のチャネルの第4FETと、を各々備える第1インバータ回路および第2インバータ回路と、前記第1インバータ回路の出力ノードが接続された第1記憶ノードと、前記第1インバータ回路の入力ノードが接続された第1記憶ノードが接続された第2記憶ノードと、を備え、前記第1インバータ回路のカフノードが表に前記第2インバータ回路のカフノードに接続され、前記第2インバータ回路のカフノードまたは前記第2インバータ回路のカフノードまたは前記第2インバータ回路のカフノードまたは前記第2インバータ回路のカフノードまたは前記第1インバータ回路の出力ノードに接続された双安定回路である。

# [0020]

本発明は、上記双安定回路と、前記電源電圧を、前記双安定回路がデータをライトおよびリード可能な第1電圧と、前記第1電圧より低く前記双安定回路がデータを保持可能な第2電圧と、に切り替えて供給する電源回路と、を備える電子回路である。

#### [0021]

上記構成において、前記電源回路が前記双安定回路に前記第1電圧および前記第2電圧のいずれを供給するときにも、前記制御ノードには定バイアスが供給される構成とすることができる。

# [0022]

上記構成において、前記定バイアスは、前記第1電圧が供給されるときの前記第1電源線の電圧と前記第2電源線の電圧との間のバイアスである構成とすることができる。

# [0023]

上記構成において、前記定バイアスは、前記第1電圧が供給されるときの前記第1電源線の電圧と前記第2電源線の電圧との中間より前記第2電源線の電圧に近い構成とすることができる。

# [0024]

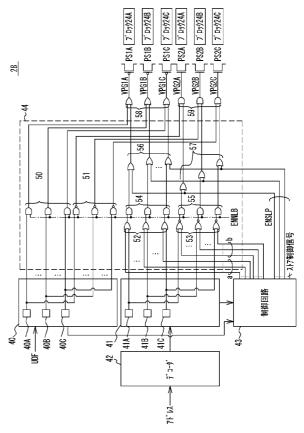

上記構成において、前記第4FETがPチャネルFETのとき、前記電源回路が前記第 1 電圧および前記第 2 電圧を供給するとき前記制御ノードにそれぞれローレベルおよび前記ローレベルより高いハイレベルを供給し、前記第4FETがNチャネルFETのとき、前記電源回路が前記第 1 電圧および前記第 2 電圧を供給するとき前記制御ノードにそれぞれハイレベルおよび前記ハイレベルより低いローレベルを供給する制御回路を備える構成とすることができる。

# [0025]

本発明は、ソースが第1電源線に接続され、ドレインが出力ノードに接続され、ゲート が入力ノードに接続された第1導電型のチャネルの第1FETと、ソースが前記第1電源 線との間に電源電圧が供給される第2電源線に接続され、ドレインが中間ノードに接続さ れ、ゲートが前記入力ノードに接続された前記第1導電型と反対の第2導電型のチャネル の第2FETと、ソースが前記中間ノードに接続され、ドレインが前記出力ノードに接続 され、ゲートが前記入力ノードに接続された前記第2導電型のチャネルの第3FETと、 ソースおよびドレインの一方が前記中間ノードに接続され、前記ソースおよび前記ドレイ ンの他方が制御ノードに接続された第4FETと、を各々備える第1インバータ回路およ び第2インバータ回路と、前記第1インバータ回路の出力ノードおよび前記第2インバー 夕回路の入力ノードが接続された第1記憶ノードと、前記第1インバータ回路の入力ノー ドおよび前記第2インバータ回路の出力ノードが接続された第2記憶ノードと、を備え、 前記第1インバータ回路の第4FETのゲートは、前記第1インバータ回路の入力ノード 、出力ノード、前記第2インバータ回路の入力ノードおよび出力ノードのいずれか1つの ノードに接続され、前記第2インバータ回路の第4FETのゲートは、前記第2インバー 夕回路の入力ノード、出力ノード、前記第1インバータ回路の入力ノードおよび出力ノー ドのいずれか1つのノードに接続された双安定回路と、前記電源電圧を、前記双安定回路 がデータをライトおよびリード可能な第1電圧と、前記第1電圧より低く前記双安定回路がデータを保持可能な第2電圧と、に切り替えて供給する電源回路と、を備え、前記電源回路が前記双安定回路に前記第1電圧および前記第2電圧のいずれを供給するときにも、前記制御ノードには定バイアスが供給される電子回路である。

### [0026]

上記構成において、前記電源回路は、前記電源電圧を前記第1電圧と前記第2電圧とに切り替えるときに、前記第2電源線には一定の第3電圧を供給し、前記第1電源線に供給する電圧をそれぞれ第4電圧と第5電圧とに切り替える構成とすることができる。

#### [0027]

上記構成において、前記定バイアスは、前記第3電圧と前記第4電圧との間のバイアスである構成とすることができる。

# [0028]

上記構成において、前記第1インバータ回路の第4FETは、ゲートが前記第1インバータ回路の出力ノードまたは前記第2インバータ回路の入力ノードに接続されているとき前記第2導電型のチャネルのFETであり、ゲートが前記第1インバータ回路の入力ノードまたは前記第2インバータ回路の出力ノードに接続されているとき前記第1導電型のチャネルのFETであり、前記第2インバータ回路の第4FETは、ゲートが前記第2インバータ回路の出力ノードに接続されているとき前記第1インバータ回路の入力ノードに接続されているとき前記第1インバータ回路の入力ノードまたは前記第1インバータ回路の出力ノードに接続されているとき前記第1インバータ回路の出力ノードに接続されているとき前記第1インバータ回路の出力ノードに接続されているとき前記第1導電型のチャネルのFETである構成とすることができる。

#### [0029]

本発明は、各々のメモリセルが、データを揮発的に記憶する双安定回路と、前記双安定回路に記憶されたデータを不揮発的にストアし、不揮発的にストアされたデータを前記双安定回路にリストアする不揮発性素子と、を備える複数のメモリセルを有するセルアレイと、前記セルアレイを電源遮断するときに、前記複数のメモリセルのうち揮発的に書き換えられているかいないかにかわらず不揮発的にストアしなくてもよいデータを揮発的に記憶する1または複数の第1メモリセルを電源遮断し、前記1または複数の第1メモリセルを電源遮断した後前記複数のメモリセルのうち残りの1または複数の第2メモリセルにおいて双安定回路に揮発的に記憶されたデータを前記不揮発性素子にストアするストア動作を行い、その後前記1または複数の第2メモリセルを電源遮断する制御回路と、を備える電子回路である。

# [0030]

上記構成において、前記セルアレイは、各々のブロックが少なくとも2つのメモリセルを含む複数のブロックに分割され、前記制御回路は、前記セルアレイを電源遮断するときに、前記複数のブロックからブロック内のメモリセルが揮発的に書き換えられているかいないかにかわらず不揮発的にストアしなくてもよいデータを揮発的に記憶する1または複数の第1ブロックを抽出し、前記1または複数の第1ブロックを電源遮断し、前記1または複数の第1ブロックを電源遮断した後前記複数のブロックのうち残りの1または複数の第2ブロック内のメモリセルにおいてストア動作を行い、ストア動作の終了した第2ブロックを電源遮断する構成とすることができる。

# [0031]

上記構成において、前記制御回路は、前記1または複数の第1ブロックを全て電源遮断した後、前記1または複数の第2ブロック内のメモリセルにおいてストア動作を行う構成とすることができる。

#### [0032]

上記構成において、前記セルアレイの外に設けられ、外部回路から受信した前記1または複数の第1ブロックを示す情報を記憶する記憶回路を備え、前記制御回路は、前記情報に基づき、前記1または複数の第1ブロックを抽出する構成とすることができる。

# [0033]

50

40

10

20

上記構成において、前記制御回路は、前記複数のブロックから、ブロック内のメモリセルが揮発的に書き換えられているかいないかにかわらず不揮発的にストアしなくてもよいデータを揮発的に記憶するブロックと、ブロック内のいずれのメモリセルも揮発的に書き換えられていないブロックと、を前記1または複数の第1ブロックとして抽出し、前記1または複数の第1ブロックを電源遮断した後前記複数のブロックのうち残りの1または複数の第2ブロック内のメモリセルにおいてストア動作を行い、ストア動作の終了した第2ブロックを電源遮断する構成とすることができる。

#### 【発明の効果】

[0034]

本発明によれば、消費電力および消費エネルギーを抑制することができる。

【図面の簡単な説明】

[0035]

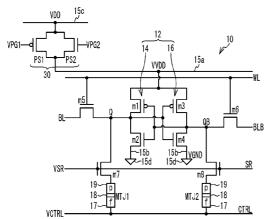

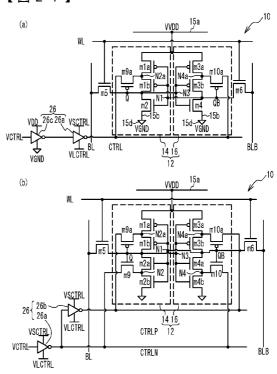

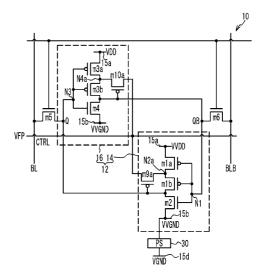

【図1】図1は、実施例1におけるメモリセルの回路図である。

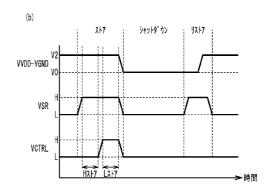

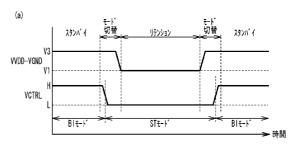

【図2】図2(a)および図2(b)は、実施例1における各状態に印加される電圧を示す図である。

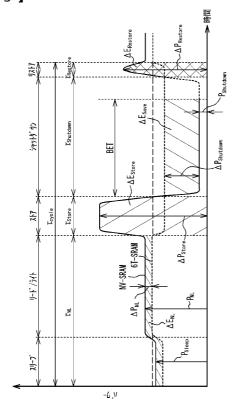

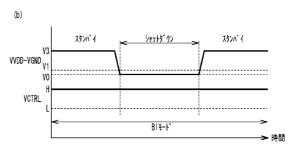

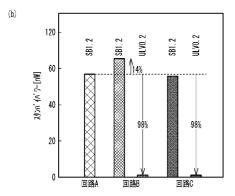

- 【図3】図3は、実施例1における各期間の消費電力を示す図である。

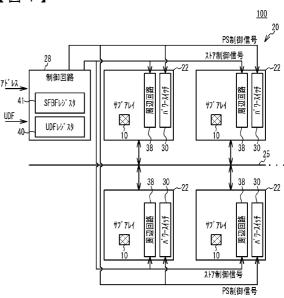

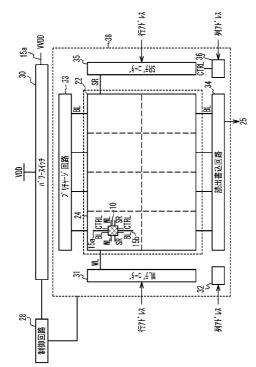

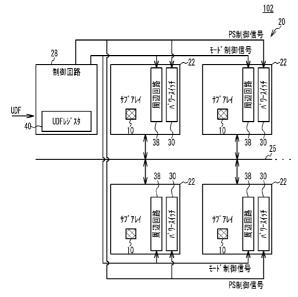

- 【図4】図4は、実施例1における電子回路を示すブロック図である。

- 【図5】図5は、実施例1におけるサブアレイのブロック図である。

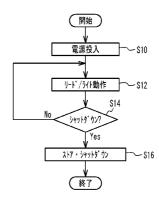

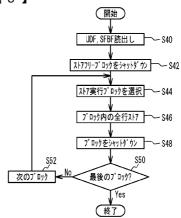

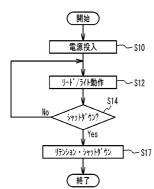

- 【図6】図6は、実施例1における動作を示すフローチャートである。

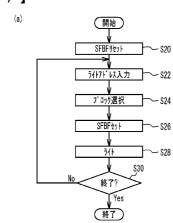

- 【図 7 】図 7 ( a )は、実施例 1 におけるリード / ライト動作を示すフローチャート、図 7 ( b )は、実施例 1 における U D F の設定を示すフローチャートである。

- 【図8】図8は、実施例1におけるストア動作を示すフローチャートである。

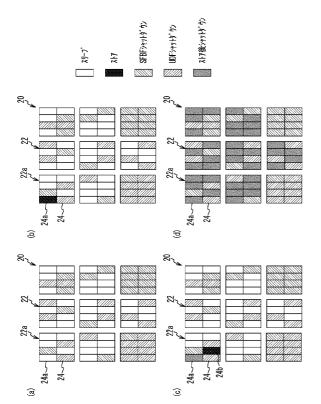

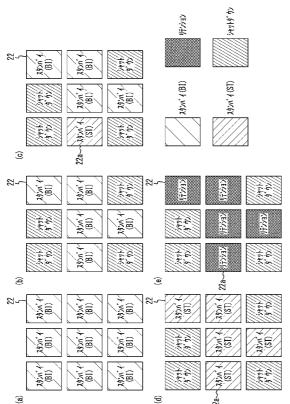

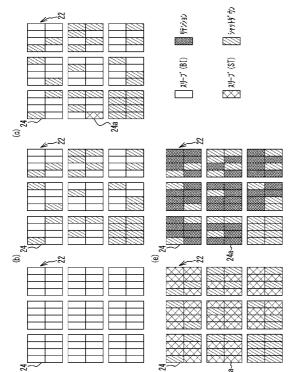

- 【図9】図9(a)から図9(d)は、実施例1におけるセルアレイおよびブロックを示す模式図である。

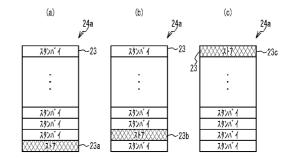

- 【図10】図10(a)から図10(c)は、実施例1におけるブロックを示す模式図である。

- 【図11】図11(a)および図11(b)は、実施例1におけるそれぞれセルアレイのサイズおよびワードアドレスの例を示す図である。

- 【図12】図12は、実施例1における制御回路の例を示すブロック図である。

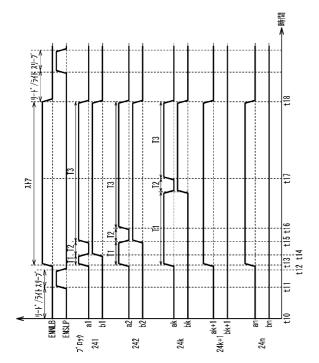

- 【図13】図13(a)から図13(e)は、実施例1における各信号<u>のレベル</u>とパワースイッチの動作を示す図である。

- 【図14】図14は、実施例1における制御信号のタイミングチャートである。

- 【 図 1 5 】図 1 5 は、実施例 1 における制御回路 2 8 の別の例のブロック図である。

- 【図16】図16(a)から図16(c)は、実施例1、比較例1-1および1-2におけるSFBFストアフリー割合に対するBETを示す図、図16(d)から図16(f)は、SFBFストアフリー割合に対するストアレイテンシを示す図である。

- 【図17】図17は、実施例2におけるメモリセルの回路図である。

- 【図18】図18(a)および図18(b)は、実施例2における各状態に印加される電圧を示す図である。

- 【図19】図19(a)および図19(b)は、実施例2におけるリテンションおよびシャットダウンに印加される電圧を示す図である。

- 【図20】図20は、実施例2における各期間の消費電力を示す図である。

- 【図21】図21(a)および図21(b)は、実施例2におけるメモリセルの別の例である。

- 【図22】図22は、実施例2における電子回路を示すブロック図である。

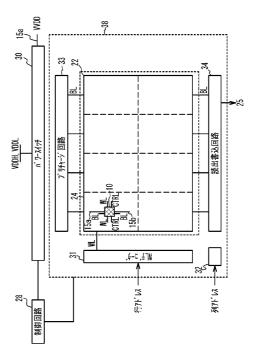

- 【図23】図23は、実施例2におけるサブアレイのブロック図である。

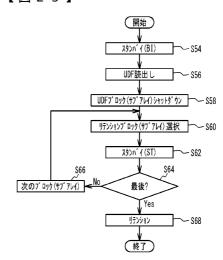

- 【図24】図24は、実施例2における動作を示すフローチャートである。

- 【図 2 5 】図 2 5 は、実施例 2 におけるリテンション動作のタイプ A を示すフローチャートである。

10

20

30

40

- 【図 2 6 】図 2 6 (a) から図 2 6 (e) は、実施例 2 におけるリテンション動作のタイプ A におけるセルアレイを示す模式図である。

- 【図27】図27(a)から図27(e)は、実施例2におけるリテンション動作のタイプAにおけるセルアレイおよびブロックを示す模式図である。

- 【図28】図28は、実施例2におけるリテンション動作のタイプBを示すフローチャートである。

- 【図29】図29(a)から図29(e)は、実施例2におけるリテンション動作のタイプBにおけるセルアレイを示す模式図である。

- 【図30】図30(a)から図30(e)は、実施例2におけるリテンション動作のタイプBにおけるセルアレイおよびブロックを示す模式図である。

- 【図31】図31は、実施例2におけるリテンション動作のタイプCを示すフローチャートである。

- 【図32】図32(a)から図32(e)は、リテンション動作のタイプ C におけるセルアレイを示す模式図である。

- 【図33】図33(a)から図33(e)は、リテンション動作のタイプ C におけるセルアレイおよびブロックを示す模式図である。

- 【図34】図34は、リテンション動作のタイプBにおける制御回路の例を示すブロック図である。

- 【図35】図35(a)から図35(e)は、リテンション動作のタイプBにおける各信号のレベルとパワースイッチの動作を示す図である。

- 【図36】図36は、リテンション動作のタイプBにおける制御信号のタイミングチャートである。

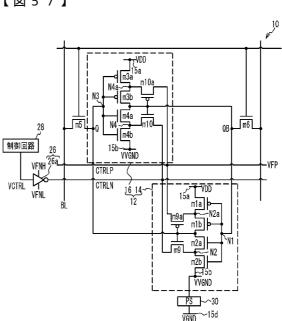

- 【図37】図37は、リテンション動作のタイプCにおける制御回路の例を示すブロック図である。

- 【図38】図38は、リテンション動作のタイプCにおける制御信号のタイミングチャートである。

- 【図39】図39(a)から図39(c)は、タイプAからCおよび比較例2におけるUD割合に対するBETを示す図、図39(d)から図39(f)は、UD割合に対するレイテンシを示す図である。

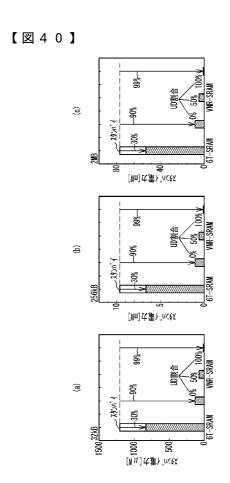

- 【図40】図40(a)から図40(c)は、タイプC、比較例2-1および2-2におけるUD割合に対するスタンバイパワーを示す図である。

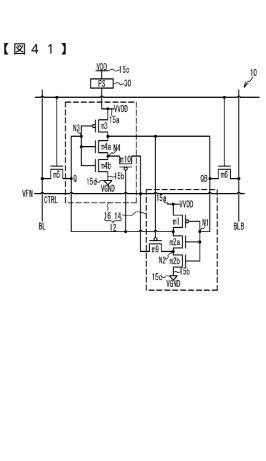

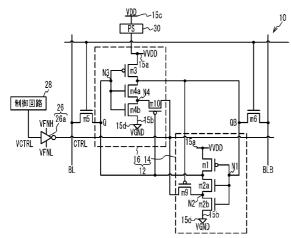

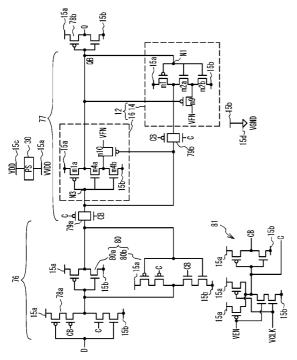

- 【図41】図41は、実施例3におけるヘッダPS・PDFB・タイプ1のメモリセルの 回路図である。

- 【図42】図42は、実施例3におけるヘッダPS・PDFB・タイプ2のメモリセルの 回路図である。

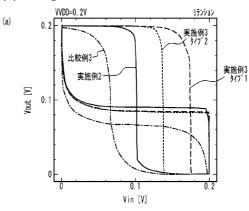

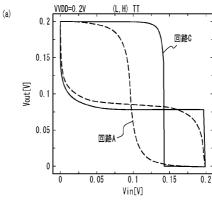

- 【 図 4 3 】 図 4 3 ( a ) は、リテンション状態におけるインバータ回路の伝達特性を示す図、図 4 3 ( b ) は、B I モードにおける S N M を示す図である。

- 【図44】図44(a)は、リテンション状態のSNMを示す図、図44(b)は、BIモードのリーク電力を示す図、図44(c)および図44(d)は、STモードのリーク電力を示す図である。

- 【図45】図45は、実施例3におけるフッタPS・PDFB・タイプ2のメモリセルの 回路図である。

- 【 図 4 6 】 図 4 6 は、実施例 3 におけるフッタ P S ・ P U F B ・ タイプ 1 のメモリセルの 回路図である。

- 【図47】図47は、実施例3におけるヘッダPS・PUFB・タイプ2のメモリセルの 回路図である。

- 【図48】図48は、実施例3におけるヘッダPS・PUPDFBのメモリセルの回路図である。

- 【 図 4 9 】 図 4 9 は、実施例 3 におけるフッタ P S ・ P U P D F B のメモリセルの回路図である。

20

30

40

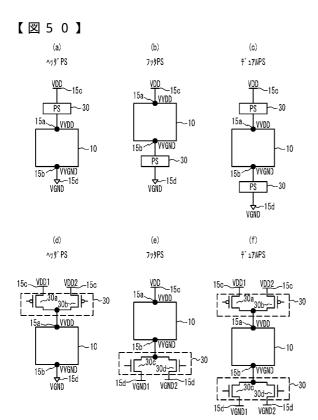

【図 5 0 】図 5 0 ( a ) から図 5 0 ( f ) は、セルに接続されるパワースイッチの配置を示す図である。

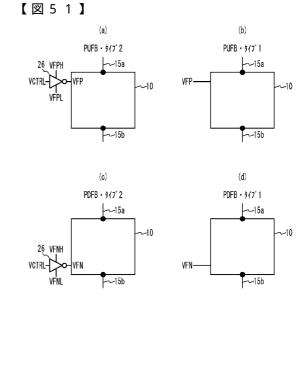

- 【図51】図51(a)から図51(d)は、セルに接続されるドライバの配置を示す図である。

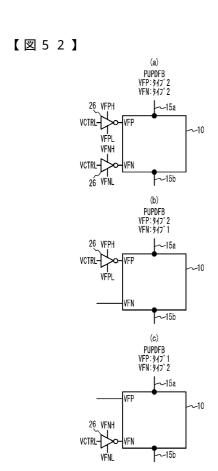

- 【図 5 2 】図 5 2 ( a ) から図 5 2 ( c ) は、セルに接続されるドライバの配置を示す図である。

- 【図53】図53(a)および図53(b)は、それぞれヘッダPS・PDFB・タイプ 1型およびフッタPS・PUFB・タイプ1型の各電圧を示す図である。

- 【図 5 4 】図 5 4 は、実施例 4 におけるヘッダ P S ・ P D F B ・ タイプ 1 型のメモリセルの回路図である。

- 【図 5 5 】図 5 5 は、実施例 4 におけるフッタ P S ・ P U F B ・ タイプ1型のメモリセルの回路図である。

- 【図56】図56は、実施例4におけるヘッダPS・PUPDFB・PD側タイプ1型の メモリセルの回路図である。

- 【図57】図57は、実施例4におけるフッタPS・PUPDFB・PU側タイプ1型のメモリセルの回路図である。

- 【図58】図58は、実施例4の変形例1に係る電子回路の回路図である。

- 【図 5 9 】図 5 9 ( a ) および図 5 9 ( b ) は、フリップフロップ回路のバタフライカーブを示す図である。

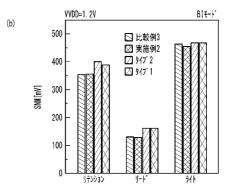

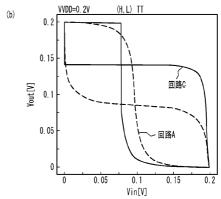

- 【 図 6 0 】 図 6 0 ( a ) は、 S N M を示す図、図 6 0 ( b ) は、スタンバイパワーを示す図である。

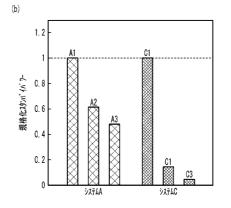

- 【図 6 1 】図 6 1 (a)は、シミュレーションしたロジックシステムの概念図、図 6 1 (b)は、システム A および C の規格化スタンバイパワーを示す図である。

【発明を実施するための形態】

[0036]

以下、図面を参照し実施例について説明する。

【実施例1】

[0037]

特許文献3のように、通常のSRAM動作(すなわちリード/ライト動作)のときに書き換えられたメモリセルのみにストア動作を行う。この方法では、セルアレイのサイズが大きくなると、ストア動作を待機するメモリセルにおけるリーク電流に起因する消費電力が大きくなる。そこで、書き換えられていないメモリセルをはじめにシャットダウンし、その後、書き換えられたメモリセルにストア動作を行うことが考えられる。しかし、書き換えられたメモリセルのデータがリストア後に不要なデータであってもストア動作を行ってしまう。これにより、消費電力およびレイテンシが増大する。

[0038]

実施例1は、消費電力および消費エネルギーを抑制することを目的とする。具体的には、PG(パワーゲーティング)時(電源遮断時)、PGへの移行およびPGからの復帰における消費電力および消費エネルギーを削減すること、およびPGに関するBETを削減することを目的とする。

[0039]

実施例1では、書き換えられているかいないかにかかわらずストアしなくてもよいデータのメモリセルをはじめにシャットダウンし、その後、残りのメモリセルにストア動作を行う。これにより、消費電力およびレイテンシを抑制できる。

[0040]

より具体的に、セルアレイを複数のブロックに分割する。記憶階層より上位の階層においてブロック毎のストアフリーを判断する。このとき、通常のSRAM動作において書き換えがあっても不要なデータであれば、ストアフリーブロックとする。上位の階層はリストア後に不要なデータの存在するブロックを指定するUDF(Useless Data Flag)を生成する。記憶階層ではUDFに基づき、ブロック毎にシャットダウンおよびストア動作を

10

20

30

40

20

30

40

50

行う。これにより、効率的に消費電力を抑制できる。

### [0041]

以下、実施例1の詳細な例について説明する。

#### 「メモリセルの説明]

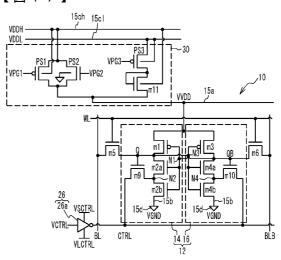

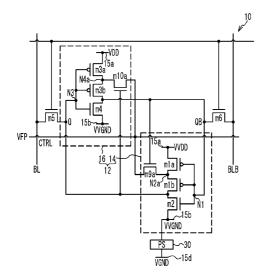

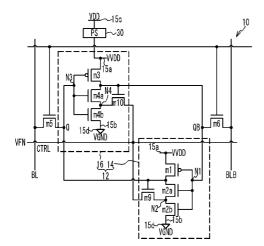

図1は、実施例1におけるメモリセルの回路図である。図1に示すように、メモリセル10は、インバータ回路14および16、スピントランスファートルク磁気トンネル接合素子(STTMTJ:以下では単に強磁性トンネル接合素子と呼ぶ)MTJ1およびMTJ2を主に備えている。

#### [0042]

インバータ回路14および16はループ状に接続され双安定回路12を構成している。インバータ回路14は、FET(Field Effect Transistor)m1およびm2を備えている。インバータ回路16はFETm3およびm4を備えている。FETm1およびm3はPチャネルMOSFETであり、FETm2およびm4はNチャネルMOSFETである。FETm1およびm3のソースは仮想電源電圧VVDDが印加された電源線15aに接続され、FETm2およびm4のソースはグランド電圧VGNDが印加されたグランド線15bに接続されている。これにより、双安定回路12には電源電圧(VVDD・VGND)が供給される。

### [0043]

インバータ回路14と16が接続されたノードがそれぞれノードQ、QBである。ノードQとノードQBとは互いに相補ノードである。双安定回路12は、ノードQおよびノードQBがそれぞれハイレベルおよびローレベル、または、ノードQおよびノードQBがそれぞれローレベルおよびハイレベルとなることにより安定状態となる。双安定回路12は、安定状態となることにより、データを記憶することができる。

# [0044]

ノードQおよびQBは、それぞれNチャネルFETm5およびm6を介しビット線BLおよびBLBに接続されている。FETm5およびm6のゲートはワード線WLに接続されている。FETm1からm6により6トランジスタ(FET)型のSRAMが形成される。

# [0045]

ノードQと制御線CTRLとの間にFETm7と強磁性トンネル接合素子MTJ1とが接続され、ノードQBと制御線CTRLとの間にFETm8と強磁性トンネル接合素子MTJ2とが接続されている。FETm7およびm8のソースおよびドレインの一方は、ノードQおよびQBに、ソースおよびドレインの他方は強磁性トンネル接合素子MTJ1およびMTJ2にそれぞれ接続されている。FETm7およびm8のゲートはスイッチ線SRに接続されている。なお、FETm7およびm8は、それぞれ、強磁性トンネル接合素子MTJ1およびMTJ2と制御線CTRLとの間に接続されていてもよい。また、FETm7およびm8は、設けられていなくてもよい。

# [0046]

強磁性トンネル接合素子MTJ1およびMTJ2は、それぞれフリー層17、トンネル 絶縁膜18およびピン層19を有している。フリー層17およびピン層19は強磁性体からなる。フリー層17とピン層19との磁化方向が平行な状態(平行状態)では、MTJ1およびMTJ2の抵抗値が低くなる。フリー層17とピン層19との磁化方向が反平行な状態(反平行状態)では、MTJ1およびMTJ2の抵抗値が平行状態より高くなる。MTJ1およびMTJ2は、MTJ1およびMTJ2の抵抗値によりデータをストアする。後述する仮想電源方式では、フリー層17が制御線CTRLに接続され、仮想接地方式では、ピン層19が制御線CTRLに接続される。仮想電源方式では、FETm7およびm8はPチャネルFETである。

# [0047]

電源線15aと電源15cとの間にパワースイッチ30が接続されている。パワースイ

# [0048]

# [ 各状態の説明]

図 2 (a) および図 2 (b) は、実施例 1 における各状態に印加される電圧を示す図である。図 2 (a) のように、リード / ライト状態では V P G 1 および V P G 2 はローレベル L である。パワースイッチ P S 1 および P S 2 はそれぞれオンおよびオフとなる。これにより、電源線 1 5 a とグランド線 1 5 b との間に供給される電源電圧 V V D D - V G N D は電圧 V 2 となる。電圧 V 2 は例えば 1 . 2 V である。

### [0049]

### [0050]

シャットダウン状態では V P G 1 および V P G 2 はそれぞれハイレベル H およびローレベル L である。パワースイッチ P S 1 および P S 2 はオフとなる。電源線 1 5 a に電源電圧が印加されない。これにより、電源電圧 V V D D - V G N D は電圧 V 1 より低い電圧 V 0 となる。電圧 V 0 は例えばほぼ 0 V である。

# [0051]

リード/ライト状態の期間は、通常のSRAMとして双安定回路12のデータを書き換え、揮発的にデータを保持する(これを、「データを揮発的に書き換える」という)期間である。双安定回路12へのデータの書き込みおよび読み出しがSRAMと同じように行われる。すなわち、ワード線WLをハイレベルとしFETm5およびm6を導通状態とすることにより、双安定回路12にビット線BLおよびBLBのデータが書き込まれる。また、ビット線BLおよびBLBを等電位の浮遊状態としワード線WLをハイレベルとしFETm5およびm6を導通状態とすることにより、双安定回路12のデータをビット線BLおよびBLBに読み出すことができる。電源電圧VVDD・VGNDは、双安定回路12がデータの書き換えが可能でかつデータが保持できる電圧V2である。

#### [ 0 0 5 2 ]

スリープ状態の期間は、メモリセル 1 0 がスリープモードの期間である。スリープ状態では、双安定回路 1 2 はデータを保持するのみであり、データの書き換えを行なわない。電源電圧 V V D D - V G N D は、双安定回路 1 2 がデータの書き換えはできないがデータが保持できる電圧 V 1 である。電圧 V 1 は電圧 V 2 より低いため、消費電力を抑制できる

# [0053]

リード / ライト状態およびスリープ状態では、制御線CTRLおよびスイッチ線SRにおける制御信号VCTRLおよびVSRはローレベルであり、FETm7およびm8はオフしている。FETm5およびm6をオフとすることにより、双安定回路12のデータが保持される。なお、双安定回路12へのデータの書き込み、読み出し、および保持のとき、スイッチ線SRをローレベルとし、FETm7およびm8をオフとすることが好ましい。これにより、ノードQおよびQBと制御線CTRL間の電流をほぼ遮断し、安定動作を実現し、さらに、消費電力の増大を抑制することができる。

# [0054]

10

20

30

40

20

30

40

50

図 2 ( b ) に示すように、ストア期間は、ストア動作が行なわれる期間であり、双安定回路 1 2 に記憶されたデータを強磁性トンネル接合素子MTJ 1 およびMTJ 2 にストアし、これを不揮発的に保持する(これを、「不揮発的にストアする」という)期間である。ストア期間では電源電圧VVDD・VGNDはリード/ストア状態と同じ電圧V 2 である。制御信号VSRをハイレベルとする。

### [0055]

Hストア期間において、制御信号VCTRLをローレベルとする。これにより、ノード Q および Q B のうちハイレベルのノードに対応する M T J が高抵抗となる。Lストア期間 において、制御信号VCTRLをハイレベルとする。これにより、ノード Q および Q B のうちローレベルのノードに対応する M T J 1 および M T J 2 が低抵抗となる。Hストア期間とLストア期間の順番は逆でもよい。このように、双安定回路 1 2 のデータが強磁性トンネル接合素子 M T J 1 および M T J 2 にストアされる。

# [0056]

シャットダウン状態の期間は、メモリセル10をシャットダウンとする期間である。シャットダウン状態においては、電源電圧VVDD・VGNDをほぼ0Vである電圧V0とする。このとき、メモリセル10にほとんど電流が流れないため、消費電力を抑制することができる。

### [0057]

リストア期間においては、制御信号VCTRLをローレベルとし制御信号VSRをハイレベルとした状態で電源電圧VVDD・VGNDを電圧V0から電圧V2に立ち上げることにより行なわれる。高抵抗の強磁性トンネル接合素子MTJ1およびMTJ2に対応するノードQおよびQBがハイレベルとなる。低抵抗のMTJ1およびMTJ2に対応するノードQおよびQBがローレベルとなる。このように、強磁性トンネル接合素子MTJ1およびMTJ2にストアされ不揮発的に保持されたデータ(これを、「不揮発的にストアされたデータ」という)が双安定回路12にリストアされる。

# [0058]

制御信号 V C T R L および V S R のハイレベルは例えば V D D または V V D D 、ローレベルは例えば V G N D である。制御信号 V C T R L におけるハイレベルはローレベルより高く、制御信号 V S R におけるハイレベルはローレベルより高い電圧であればよい。

### [0059]

図3は、実施例1における各期間の消費電力を示す図である。実線は図1に示したメモリセル10(NV-SRAM)を有する記憶回路の消費電力(パワー)を示す。実線の消費電力は、リーク電流に起因する電力とストアおよびリストアに用いる電力を含み、リード/ライト期間におけるリードおよびライトの電力は含んでいない。点線は、FETm7、FETm8、MTJ1およびMTJ2を設けない6トランジスタSRAM(6T-SRAM)セルを用いた記憶回路の消費電力を示している。破線は、6T-SRAMセルを用いた記憶回路のリード/ライト期間の消費電力を示している。破線および点線の消費電力は、リーク電流に起因する電力を含み、リード/ライト期間におけるリードおよびライトの電力は含んでいない。

# [0060]

図3に示すように、メモリセル10の動作期間には、スリープ期間(スリープ状態の期間)、リード/ライト期間(リード/ライト状態の期間)、ストア期間、シャットダウン期間(シャットダウン状態の期間)およびリストア期間がある。スリープ期間およびリード/ライト期間の長さを NLとする。ストア期間、シャットダウン期間およびリストア期間の長さをそれぞれ Store、 Shutdownおよび Restoreとする

#### [0.061]

NV-SRAMのスリープ期間およびリード/ライト期間の消費電力はそれぞれPs1eepおよびPNLである。NV-SRAMのPs1eepおよびPNLは6T-SRAMのスリープ期間およびリード/ライト期間の消費電力より PNL大きい。これは、N

V-SRAMではFETm7およびm8にリーク電流が流れるためである。

# [0062]

NV-SRAMでは、ストア期間にストアのための電力 Pstoreが生じる。シャットダウン期間に消費電力Pshutdownが生じる。消費電力Pshutdownはリーク電流に起因する。リストア期間にリストアのための電力 Prestoreが生じる。6T-SRAMでは、NV-SRAMにおけるストア期間、シャットダウン期間およびリストア期間に相当する期間を、スリープ期間とする。よって、これらの期間の6T-SRAMの消費電力はPsleep- Pnlとなる。シャットダウン期間のNV-SRAMと6T-SRAMの消費電力の差は Pshutdownである。

#### [0063]

NV-SRAMセルの6T-SRAMセルに対するエネルギーの増加は、スリープ期間およびリード/ライト期間における  $P_{NL}$ によるエネルギー増加  $E_{NL}$ 、ストア期間の  $P_{Re}$  storeによるエネルギー増加  $E_{Store}$ の合計である。NV-SRAMセルがシャットダウンにより節約できるエネルギーは、シャットダウン期間における  $P_{Sh}$  utdownによるエネルギー減少  $E_{Save}$ である。  $E_{NL}$  ttdown ttdown

### [0064]

# [電子回路の説明]

図4は、実施例1における電子回路を示すプロック図である。図4に示すように、電子回路100は、セルアレイ20、制御回路28を備えている。セルアレイ20は、複数のサブアレイ22に分割されている。サブアレイ22の記憶容量は例えば8kバイトである。サブアレイ22には複数のメモリセル10がマトリックス状に設けられている。サブアレイ22はバス25に接続されている。サブアレイ22の個数は適宜設計可能である。

#### [0065]

サブアレイ 2 2 にはパワースイッチ 3 0 および周辺回路 3 8 が設けられている。パワースイッチ 3 0 はサブアレイ 2 2 毎に電源電圧を設定する。周辺回路 3 8 はサブアレイ 2 2 毎にストアフリー制御を行う。

#### [0066]

制御回路28はSFBF(Store Free Block Flag)レジスタ41およびUDF(Usele ss Data Flag)レジスタ40を備えている。制御回路28はアドレスに基づきプロックごとにSFBFを生成しレジスタ41に格納する。制御回路28が外部回路から受信したブロック毎のUDFをレジスタ40に格納する。制御回路28は、PS制御信号を用い各サプアレイ22のパワースイッチ30を制御することでサブアレイ22毎にパワーを制御する。このように制御回路28はパワーマネージメントユニットとして機能する。また、制御回路28は、ストア制御信号を用い各サブアレイ22の周辺回路38を制御することでサブアレイ22毎にストアフリー動作を制御する。このように制御回路28はストアフリーマネージメントユニットとして機能する。さらに、制御回路28はバス25を介しサプアレイ22へのデータの入出力を行う。制御回路28の少なくとも一部の機能は外部のCPU(Central Processing Unit)等のプロセッサ回路がソフトウエアと協働で行ってもよい。

# [0067]

### 「サブアレイの説明)

図 5 は、実施例 1 におけるサブアレイのブロック図である。図 5 に示すように、サブアレイ 2 2 は、メモリセル 1 0 を有する複数のブロック 2 4 (例えば 8 個)に分割されている。ブロック 2 4 の記憶容量は例えば 1 k バイトである。ブロック 2 4 の個数は適宜設計可能である。サブアレイ 2 2 内には複数のメモリセル 1 0 がマトリックス状に配置されて

10

20

30

40

いる。サブアレイ22内には、行方向にワード線WLおよびスイッチ線SRが延伸し、列方向にビット線BL(図1のビット線BLおよびBLBに相当する)および制御線CTRLが延伸している。各メモリセル10には、ワード線WL、スイッチ線SR、ビット線BL、制御線CTRL、電源線15aおよびグランド線15bが接続されている。

# [0068]

各サブアレイ22に対応し、パワースイッチ30および周辺回路38が設けられている。制御回路28は、パワースイッチ30および周辺回路38を制御する。パワースイッチ30は、ブロック24毎に電源電圧VVDD-VGNDを電圧V2、V1およびV0にできる。周辺回路38は、WLデコーダ31、列デコーダ32、36、プリチャージ回路33、読出書込回路34およびSRデコーダ35を備えている。

# [0069]

リード / ライト期間において、W L デコーダ 3 1 は行アドレスに基づきワード線W L を選択する。列デコーダ 3 2 は列アドレスに基づきビット線 B L を選択する。プリチャージ 回路 3 3 はビット線 B L をプリチャージする。読出書込回路 3 4 は、W L デコーダ 3 1 および列デコーダ 3 2 に選択されたメモリセル 1 0 の双安定回路 1 2 にデータを書き込みまたは双安定回路 1 2 からデータを読み出しバス 2 5 に出力する。

### [0070]

ストア期間において、SRデコーダ35は行アドレスに基づきスイッチ線SRを選択する。列デコーダ36は列アドレスに基づき制御線CTRLを選択する。WLデコーダ31および列デコーダ32に選択されたメモリセル10において双安定回路12のデータが強磁性トンネル接合素子MTJ1およびMTJ2に不揮発的にストアされる。

### [0071]

# [動作の説明]

図6は、実施例1における動作を示すフローチャートである。図6に示すように、制御回路28は、外部回路からの指令によりセルアレイ20の電源を投入する(ステップS10)。例えば、制御回路28は全てのブロック24において、制御信号VSRをハイレベルとすることでFETm7およびm8をオンし、かつパワースイッチPS1をオンしPS2をオフする。これにより、セルアレイ20内の各メモリセル10において、強磁性トンネル接合素子MTJ1およびMTJ2内のデータが双安定回路12にリストアされる。

### [0072]

制御回路28は、リードおよびライト動作を行う(ステップS12)。制御回路28は、外部回路からセルアレイ20をシャットダウンする指示を受けたか否か判定する(ステップS14)。NoのときステップS12に戻る。Yesのとき、制御回路28は、ストア動作およびシャットダウンを行う(ステップS16)。その後終了しステップS10に戻る。

# [0073]

### 「リード/ライト動作の説明]

図6のステップS12における動作について説明する。図7(a)は、実施例1におけるリード/ライト動作を示すフローチャートである。図7(a)に示すように、制御回路28はレジスタ41の全てのプロック24に対応するSFBFをリセットする(ステップS20)。例えば制御回路28は全てのブロック24に対応するSFBFをハイレベルHとする。制御回路28にライトアドレスが入力される(ステップS22)。制御回路28は、ライトを行うブロック24(すなわち書き込みを行うメモリセル10を含むブロック24)を選択する(ステップS24)。制御回路28は、WLデコーダ31および列デコーダ32を用い選択されたブロック24に対応するレジスタ41にSFBFをセットする(ステップS26)。例えば制御回路28は対応するSFBFをローレベルLとする。制御回路28は、読出書込回路34を用い選択されたブロック24内のメモリセル10にデータを書き込む(ステップS28)。制御回路28は、動作を終了するか判定する(ステップS30)。NoのときステップS22に戻る。Yesのとき終了する。

# [0074]

50

40

10

20

### [UDF設定の説明]

UDFを設定する動作について説明する。UDFは、ブロック24のデータがストアしなくてもよいデータ(すなわち、シャットダウン後にリストアされなくてもよいデータ)であることを示す情報である。図7(b)は、実施例1におけるUDFの設定を示すフローチャートである。図7(b)に示すように、制御回路28はレジスタ40の全てのブロック24に対応するUDFをリセットする(ステップS32)。例えば制御回路28は全てのブロックに対応するUDFをローレベルLとする。制御回路28に外部回路からUDFが入力される(ステップS34)。UDFは、例えばブロック24にデータをライトするときに入力される。または、データのリードまたはライトに関係なく、定期的または不定期に入力される。制御回路28はUDFが指定するブロック24に対応するUDFをハイレベルHとする。制御回路28は、動作を終了するか判定する(ステップS38)。NoのときステップS34に戻る。Yesのとき終了する。

### [0075]

UDFは、例えば、外部回路のCPUにおけるOS (Operating System)またはプログラム等のソフトウエアにより生成される。また、UDFの生成の一部は専用のハードウェア回路が行ってもよい。UDFを生成するアルゴリズムをコンパイラ上に実装しておき、コンパイラによりUDFを自動的に生成してもよい。ユーザがUDFとなるデータをプログラム上で指定してもよい。UDFとなるデータを機械学習等により学習させて、UDFを生成してもよい。これらのUDFの生成の方法を複数組み合わせてもよい。電子回路10がキャッシュメモリのとき、ストアしなくてもよいデータとは、例えば長期間使われなかったデータ、使用頻度の少ないデータ、またはライト時期が古いデータなどである。

# 「ストア動作の説明]

図6のステップS16の動作について説明する。図8は、実施例1におけるストア動作を示すフローチャートである。

# [0077]

[0076]

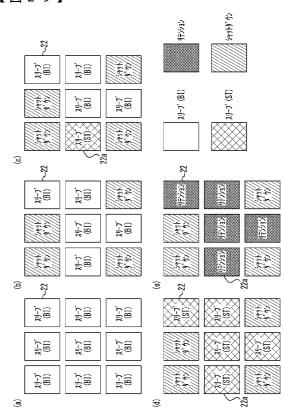

図 9 ( a ) から図 9 ( d ) は、実施例 1 におけるセルアレイおよびブロックを示す模式図である。図 9 ( a ) から図 9 ( d ) において、セルアレイ 2 0 内のサブアレイ 2 2 を 3  $\times$  3 の 9 個、 1 つのサブアレイ 2 2 内のブロック 2 4 を 4  $\times$  2 の 8 個として説明する。「スリープ」はスリープ状態(すなわちブロック 2 4 内の全てのメモリセル 1 0 がスリープモードの状態)のブロック 2 4 を示す。「ストア」はストア動作中のブロック 2 4 を示す。「SFBFシャットダウン」はSFBFによるシャットダウン状態(すなわち全てのメモリセル 1 0 がシャットダウン状態)のブロック 2 4 を示し、「UDFシャットダウン」はUDFによるシャットダウン状態のブロック 2 4 を示す。

#### [0078]

図 1 0 ( a ) から図 1 0 ( c ) は、実施例 1 におけるブロックを示す模式図である。図 1 0 ( a ) から図 1 0 ( c ) において、ブロック 2 4 a 内には複数の行 2 3 が設けられている。「スタンバイ」はストアを待機している状態の行 2 3 である。「ストア」はストア動作中の行 2 3 を示す。行 2 3 a から 2 3 c は複数の行 2 3 のうちの特定の行を示す。

# [0079]

図8に示すように、図6のステップS16において制御回路28がストア動作を開始すると、制御回路28は、各ブロック24に対応するUDFおよびSFBFをレジスタ40および41からそれぞれ読み出す(ステップS40)。制御回路28は、UDFおよびSFBFの少なくとも一方がセットされた(例えばハイレベルH)ブロック24をストアフリーブロックとして抽出する。ストアフリーブロックを一括してシャットダウンする(ステップS42)。例えば制御回路28は、パワースイッチ30にストアフリーブロックの電源電圧VVDD-VGNDをV0とさせる。

### [0800]

50

20

30

20

30

40

50

図 9 ( a ) に示すように、制御回路 2 8 は 9 個のサブアレイ 2 2 の各 8 個のブロック 2 4 である 9  $\times$  8 = 7 2 個のうち、 S F B F がセットされている 1 7 個のブロック 2 4 と、 U D F がセットされている 1 9 個のブロック 2 4 と、 の合計が 3 6 個のブロック 2 4 を一括してシャットダウンする。残りの 3 6 個のブロック 2 4 をスリープ状態とする。

### [0081]

制御回路28は、ストア動作を実行する最初のブロック24aを選択する(ステップS44)。図9(b)に示すように、制御回路28はサブアレイ22aのブロック24aを選択し、ストア動作を開始する。

# [0082]

選択されたブロック24aのストア動作として、制御回路28は、選択されたブロック 24a内を行ごとにストア動作する(ステップS46)。

# [0083]

図10(a)に示すように、制御回路28は最初の行23aをストア<u>動作</u>する。他の行23をスタンバイとする。例えば、制御回路28は行23aのFETm7およびm8をオンし、スタンバイ状態の行23のFETm7およびm8をオフする。制御回路28は、列方向に延伸する制御線CTRLにストア<u>動作</u>のための電圧を印加する。これにより、FETm7およびm8がオンかつ制御線CTRLに電圧を印加したメモリセル10において、双安定回路12のデータが強磁性トンネル接合素子MTJ1およびMTJ2に不揮発的にストアされる。制御線CTRLには、1列ずつ電圧を印加してもよいし複数列同時に電圧を印加してもよい。行23a内の全てのメモリセル10のストア<u>動作</u>が終了すると行23aのストア動作が終了する。

#### [0084]

図10(b)に示すように、制御回路28は次の行23bをストア<u>動作</u>する。図10(c)に示すように、制御回路28は、順に行23をストア<u>動作</u>し、最後の行23cをストア<u>動作</u>する。全ての行23のストア<u>動作</u>が終了すると、プロック24aのストア動作が終了する。

# [0085]

制御回路 2 8 は、ブロック 2 4 a をシャットダウンする(ステップ S 4 8 )。制御回路 2 8 は、選択されたサブアレイ 2 2 内の最後のブロックのストア動作が終了したか判断する(ステップ S 5 0 )。 N o のとき、次のブロック 2 4 b に進み(ステップ S 5 2 )、ステップ S 4 4 に戻る。

#### [0086]

図9(c)に示すように、ステップS44において制御回路28はブロック24bを選択し、ステップS46においてブロック24bのストア動作を行なう。ステップS48において制御回路28はブロック24bをシャットダウンする。その後、順次ステップS44からS52を繰り返す。

#### [0087]

図9 (d)に示すように、最後のブロック24のストア動作が終了し、全てのブロック24がシャットダウン状態となる。制御回路28はステップS50においてYesと判定し、ストア動作を終了する。

#### [0088]

# 「制御回路の例]

図 1 1 (a) および図 1 1 (b) は、実施例 1 におけるそれぞれセルアレイのサイズおよびワードアドレスの例を示す図である。図 1 1 (a) に示すように、セルアレイ 2 0 のサイズとして、例えば 3 2 k バイト、 2 5 6 k バイトおよび 2 m バイトとする。 1 個のブロック 2 4 のサイズを 1 k バイトとし、 1 個のサブアレイ 2 2 内のブロック 2 4 の個数 N b 1 o c k を 8 とすると、サブアレイ 2 2 の個数 N S A はそれぞれ 4 個、 3 2 個、 2 5 6 個となる。サブアレイ 2 2 のアドレスのビット数 X はそれぞれ 2 ビット、 5 ビットおよび 8 ビットとなる。ブロック 2 4 のアドレスのビット数 Y は 3 ビットである。

### [0089]

20

30

40

50

図 1 1 ( b ) に示すように、ワードアドレスは、上位からサブアレイアドレス X ビット、ブロックアドレス Y ビットおよび、ブロック内の行アドレス ( 例えば 1 k バイトのとき 7 ビット ) である。

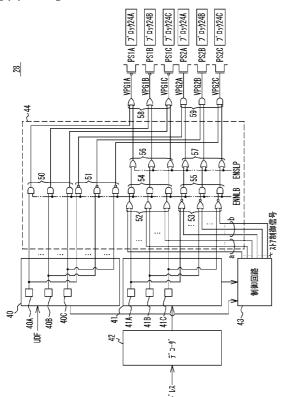

#### [0090]

図12は、実施例1における制御回路の例を示すブロック図である。制御回路28は、デコーダ42、レジスタ40、41、制御回路43およびPS制御回路44を備えている。レジスタ40および41のビット数は各々ブロック24の個数のNSA×Nblock以上である。NSA×Nblock個のブロック24のうちブロック24Aから24Cについて説明する。

# [0091]

UDF記憶部40Aから40Cはそれぞれブロック24Aから24Cに対応する1ビットのラッチ回路である。図7(b)のステップS32において、全ての記憶部40Aから40CがローレベルLにリセットされる。ステップS34において制御回路28にUDFが入力すると、ステップS36において、対応するブロック24Aから24Cの記憶部40Aから40CがハイレベルHにセットされる。

#### [0092]

SFBF記憶部41Aから41Cはそれぞれブロック 2 4 A から 2 4 C に対応する1ビットのラッチ回路である。図7(a)のステップS20において、全ての記憶部41Aから41CがハイレベルHにリセットされる。ステップS22においてデコーダ42にライトのアドレス信号が入力する。ステップS24においてサブアレイアドレスXおよびブロックアドレスYから対応するブロック24が選択される。ステップS26において、対応するブロック24Aから 2 4 C の記憶部40Aから40CがローレベルLにセットされる

# [0093]

制御回路43は、ストア制御信号a、b<u>を</u>出力する。PS制御回路44は、レジスタ40および41に保持されたUDFおよびSFBFに基づき各ブロック24Aから24CのパワースイッチPS1AからPS1CおよびPS2AからPS2Cを制御する。

# [0094]

P S 制御回路 4 4 は、各々ブロック 2 4 A から 2 4 C の個数の A N D 回路 5 0、 N A N D 回路 5 1、 O R 回路 5 2、 N O R 回路 5 3、 A N D 回路 5 4、 A N D 回路 5 5、 O R 回路 5 6、 O R 回路 5 7、 O R 回路 5 8 および A N D 回路 5 9 を備えている。

#### [0095]

PS制御回路44に入力する制御信号a、b、ENNLBおよびENSLPは、各々ブロック24Aから24Cに共通の制御信号であり、制御信号VCTRLおよびVSRは、各々ブロック24Aから24Cごとに独立する信号である。

## [0096]

AND回路50には、UDF記憶部40Aから40Cの出力信号と制御信号ENNLBが入力する。NAND回路51にはUDF記憶部40Aから40Cの出力信号と制御信号ENNLBが入力する。

# [0097]

OR回路52にはSFBF記憶部41Aから41Cの出力信号と制御信号aが入力する。NOR回路53にはSFBF記憶部41Aから41Cの出力信号と制御信号bが入力する。AND回路54にはOR回路52の出力信号と制御信号ENNLBが入力する。AND回路55にはNOR回路53の出力信号と制御信号ENNLBが入力する。OR回路56にはAND回路54の出力信号と制御信号ENSLPが入力する。OR回路57にはAND回路55の出力信号と制御信号ENSLPが入力する。

# [0098]

OR回路58にはAND回路50の出力信号とOR回路56の出力信号が入力する。OR回路58からPS制御信号VPG1AからVPG1Cが出力される。PS制御信号VPG1AからVPG1Cが出力される。PS制御信号VPG1AからVPG1Cはそれぞれブロック24Aから24CのパワースイッチPS1Aか

20

30

40

50

ら P S 1 C のゲートに入力する。

# [0099]

A N D 回路 5 9 には N A N D 回路 5 1 の出力信号と O R 回路 5 7 の出力信号が入力する。 A N D 回路 5 9 から P S 制御信号 V P G 2 A から V P G 2 C が出力される。 P S 制御信号 V P G 2 A から V P G 2 C はそれぞれブロック 2 4 A から 2 4 C のパワースイッチ P S 2 A から P S 2 C のゲートに入力する。

### [0100]

図13(a)から図13(e)は、実施例1における各信号 $\underline{o}$  レベル とパワースイッチの動作を示す図である。図13(a)に示すように、リード / ライト期間には、制御信号a、b、ENNLBおよびENSLPは全てLである。ブロック24Aから24CのUDFをそれぞれL、LおよびHであるとする。ブロック24Aから24CのSFBFをそれぞれL、HおよびLであるとする。このとき、VPG1AからVPG1CはLでありパワースイッチPS1AからPS1Cはオンである。VPG2AからVPG2CはLでありパワースイッチPS2AからPS2Cはオフである。このように、リード / ライト期間では、UDFおよびSFBFによらず、パワースイッチPS1AからPS1CがオンでありパワースイッチPS2AからPS2Cがオフである。よって、全ブロック24Aから24Cには電源電圧VVDD・VGNDとしてリード / ライト用の電圧V2が印加される。

### [0101]

図13(b)に示すように、スリープ期間には、制御信号ENSLPがHであり、制御信号a、bおよびENNLBはLである。VPG1AからVPG1CはHでありパワースイッチPS1AからPS1Cはオフである。VPG2AからVPG2CはHでありパワースイッチPS2AからPS2Cはオンである。このように、スリープ期間では、UDFおよびSFBFによらず、パワースイッチPS1AからPS1CがオフでありパワースイッチPS2AからPS2Cがオンである。よって、全ブロック24Aから24Cには電源電圧VVDD・VGNDとしてスリープ用の電圧V1が印加される。

# [0102]

図8のステップS42において、リード / ライト状態からストアフリーブロック24 B および24 C を一括してシャットダウン状態とする。図13(c)に示すように、図13(a)と比べ、制御信号 a および E N N L B は L から H となる。制御信号 b および E N S L P は L を維持する。 V P G 1 A から V P G 1 C は L から H となりパワースイッチ P S 1 A から P S 1 C はオンからオフとなる。 V P G 2 A は L から H となり、 V P G 2 B および V P G 2 C は L を維持する。パワースイッチ P S 2 A はオフからオンし、パワースイッチ P S 2 B および P S 2 C はオフを維持する。これにより、 U D F および S F B F の少なくとも一方が H のプロック 2 4 B および 2 4 C の電源電圧 V V D D - V G N D は V 0 となり、プロック 2 4 B および 2 4 C はシャットダウン状態となる。 U D F および S F B F の両方が L のプロック 2 4 A の電源電圧 V V D D - V G N D は V 1 となり、プロック 2 4 A はスリープ状態となる。

# [0103]

図8のステップS42の状態(この期間をT1とする)から、ステップS46において、選択されたブロック24Aがストア動作する。図13(d)に示すようにステップS42からS46において、制御信号aはHからLとなり、制御信号bはLからHとなる。制御信号ENNLBおよびENSLPはそれぞれHおよびLを維持する。VPG1AはHからLとなり、PS1AはHからLとなり、PS1AはHからLとなり、PS1Aはオフからオンとなる。VPG2AはHからLとなり、PS2Aはオンからオフとなる。PS1B、PS1C、PS2BおよびPS2Cはオフを維持する。ブロック24Aの電源電圧VVDD・VGNDはスタンバイ用の電圧V2となり、ブロック24Bおよび24Cの電源電圧VVDD・VGNDはV0となる。これにより、ブロック24Aはストア動作のスタンバイ状態となり、ブロック24BおよびCはシャットダウン状態を維持する。ブロック24Aには制御回路43から出力されるストア制御信号に応じて制御信号VCTRLおよびVSRが印加される。これにより、図10(a)から図10(c)のように、対象となるブロック24Aのストア動作が実行される。この期間をT

2とする。

# [0104]

図8のステップS48において、ブロック24Aのストア動作が終了すると、制御信号 a は L から H となる。制御信号 b 、 E N N L B および E N S L P はそれぞれ H 、 H および L を維持する。 V P G 1 A は L から H となり、 P S 1 A はオンからオフとなる。これにより、ブロック24Aの電源電圧 V V D D ・ V G N D は電圧 V 2 から電圧 V 0 となり、ブロック24A はシャットダウン状態となる。この期間を T 3 とする。図8のステップS44からS52のループを行うことにより、ストア動作対象のブロック24について、制御信号(a、b)を順次(H、L) (L、H) (H、H)とする。これにより、ストア動作対象のブロック24が順次ストア動作される。

[0105]

図13(e)に示すように、シャットダウン状態においては、制御信号 a、 b、 E N N E N E N S E N S E N S E N S E N S E N S E N S E N S E N S E N S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E S E

[0106]

図 1 4 は、実施例 1 における制御信号のタイミングチャートである。制御信号 a 1 ~ a n は各ブロック 2 4 1 から 2 4 n に対応する制御信号 a であり、制御信号 b 1 ~ b n は各プロック 2 4 1 から 2 4 n に対応する制御信号 b である。ブロック 2 4 1 ~ 2 4 k はストア動作対象のブロックであり、ブロック 2 4 k + 1 ~ ブロック 2 4 n はストアフリーブロックである。

[0107]

図 1 4 に示すように、時刻 t 1 0 と t 1 1 との間はリード / ライト期間であり、制御信号 a 1 ~ a n 、 b 1 ~ b n 、 E N N L B および E N S L P は L である。時刻 t 1 1 と t 1 2 との間はスリープ期間であり、制御信号 E N S L P は H であり、他の制御信号は L である。

[0108]

ストア動作が開始されると、時刻 t 1 3 (図 8 のステップ S 4 2 ) において、制御信号 E N N L B および a 1 ~ a n が H となる。これにより、ストア動作対象のブロック 2 4 1 ~ 2 4 k は期間 T 1 のスリープ状態となり、ストアフリーブロック 2 4 k + 1 ~ 2 4 n は シャットダウン状態となる。この状態は期間 T 1 である。

[0109]

時刻 t 1 4 において、ストア動作対象のブロック 2 4 1 に対応する制御信号 a 1 および b 1 はそれぞれ L および H となる。時刻 t 1 4 と t 1 5 との間の期間はブロック 2 4 1 の 期間 T 2 であり、ブロック 2 4 1 はストア動作されている。時刻 t 1 5 において、制御信号 a 1 は H となり b 1 は H を維持する。時刻 t 1 5 以降の期間はブロック 2 4 1 の期間 T 3 であり、ブロック 2 4 1 はシャットダウン状態である。時刻 t 1 5 において、ブロック 2 4 2 に対応する制御信号 a 2 および b 2 はそれぞれ L および H となる。時刻 t 1 5 と t 1 6 との間の期間はブロック 2 4 2 の期間 T 2 であり、ブロック 2 4 2 はストア動作されている。時刻 t 1 6 において制御信号 a 2 は H となり b 2 は H を維持する。時刻 t 1 6 以降の期間はブロック 2 4 2 の期間 T 3 であり、ブロック 2 4 2 はシャットダウン状態である。

[0110]

[0111]

10

20

30

40

20

30

40

50

このように、時刻 t 1 3 においてブロック 2 4 1 から 2 4 k は一括してスリープ状態 (期間 T 1 ) となり、ブロック 2 4 k + 1 から 2 4 n は一括してシャットダウン状態となる。その後、ブロック 2 4 1 から 2 4 k は順次ストア<u>動作</u> (期間 T 2 ) <u>が行われる</u>。ストア<u>動作</u>の終了したブロックは順次シャットダウン状態(期間 T 3 ) となる。

# [0112]

図15は、実施例1における制御回路28の別の例のブロック図である。図15に示すように、制御信号ENSLPをブロック24Aから24C毎の信号とすることで、ブロック24Aから24Cごとにスリープ状態とすることが可能である。その他の構成は図12と同じであり説明を省略する。

#### [0113]

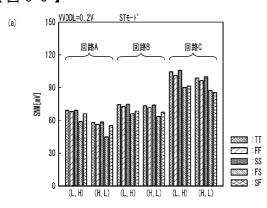

### 「シミュレーション 1

実施例1に係る電子回路についてBETおよびストア動作のレイテンシをシミュレーションした。比較例1-1および比較例1-2についてもシミュレーションした。比較例1-1では、サブアレイ22およびブロック24の一括遮断を行なわず、SFBFがセットされているブロック24のストア動作を順次スキップする。比較例1-2では、UDFによる一括遮断を行わずSFBFによる一括遮断のみを行なう。

### [0114]

シミュレーション条件は以下である。リード/ライト期間、ストア期間およびリストア期間における電源電圧VVDD・VGNDである電圧V2を1.2Vとした。スリープ期間における電源電圧VVDD・VGNDである電圧V1および制御線CTRLの電圧をそれぞれ0.8Vおよび0Vとした。ストア期間におけるスイッチ線SRの電圧を0.75Vとした。ストア期間における制御線CTRLのハイレベルおよびローレベルの電圧をそれぞれ0.45Vおよび0Vとした。サブアレイ22およびブロック24の記憶容量をそれぞれ8kバイトおよび1kバイトとした。

#### [0115]

セルアレイ 2 0 内の全メモリセルの個数に対する S F B F によるストアフリーメモリセルの個数の比を S F B F ストアフリー割合 (proportion)とした。セルアレイ 2 0 内の全メモリセルの個数に対する U D F によるストアフリーメモリセルの個数の比を U D 割合 (proportion)とした。セルアレイ 2 0 内に揮発的に書き込まれるメモリセル 1 0 は特定のサブアレイ 2 2 およびブロック 2 4 に集中することを考慮し、ストア動作にかかる時間をストアレイテンシとした。セルアレイ 2 0 の記憶容量が 3 2 k バイト、2 5 6 k バイトおよび 2 M バイトについてシミュレーションした。

# [0116]

図16(a)から図16(c)は、実施例1、比較例1-1および1-2におけるSFBFストアフリー割合に対するBETを示す図、図16(d)から図16(f)は、SFBFストアフリー割合に対するストアレイテンシを示す図である。図16(a)に示すように、比較例1-1では、32kバイトのときストアフリー割合が大きくなるとBETが短くなる。

### [0117]

図16(b)および図16(c)のように、256kバイトおよび2Mバイトと記憶容量が大きくなると、SFBFストアフリー割合が大きくなってもBETは小さくならない。これは以下の理由のためである。すなわち、記憶容量が大きくなると、ストア動作を待機するブロック24<u>の数</u>が大きくなる。ストア動作の待機中にもメモリセル10にはリーク電流が流れる。このため、セルアレイ20全体でのリーク電流が大きく、ストアフリー割合が大きくなってもBETは小さくならない。

#### [0118]

図 1 6 ( d ) から図 1 6 ( f ) に示すように、比較例 1  $\underline{\phantom{a}}$  ではストアレイテンシはストアフリー割合によらず一定である。

# [0119]

図16(a)から図16(c)のように、比較例1-2では記憶容量によらずストアフ

20

30

40

50

リー割合が大きくなるとBETが小さくなる。図16(d)から図16(f)のように、比較例1-<u>2</u>では記憶容量によらずストアフリー割合が大きくなるとストアレイテンシが短くなる。これらは、比較例1-2では、ストアフリーのプロック24を最初にシャットダウンするためである。

# [0120]

図 1 6 ( a ) から図 1 6 ( c ) のように、実施例 1 では、比較例 1 -  $\underline{2}$  に比べ U D 割合が大きくなると B E T が短くなる。図 1 6 ( d ) から図 1 6 ( f ) のように、実施例 1 では、比較例 1 -  $\underline{2}$  に比べ U D 割合が大きくなるとストアレイテンシが短くなる。

# [0121]

実施例1によれば、図1のように、各々のメモリセル10は、データを揮発的に記憶する双安定回路12と、双安定回路12に記憶されたデータを不揮発的にストアし、不揮発的にストアされたデータを双安定回路12にリストアする不揮発性素子と、を有する。図8のステップS42のように、制御回路28は、セルアレイ20をシャットダウン(電源遮断)するときに、複数のメモリセル10のうち揮発的に書き換えられているかいないかにかわらず不揮発的にストアしなくてもよいデータを揮発的に記憶する1または複数の第1メモリセルをシャットダウンする。ステップS44およびS46のように、第1メモリセルをシャットダウンした後、複数のメモリセルのうち残りの1または複数の第2メモリセルにおいて双安定回路12に揮発的に記憶されたデータを不揮発性素子にストアするストア動作を行う。ステップS48のように、その後制御回路28は第2メモリセルをシャットダウンする。

# [0122]

これにより、揮発的に書き換えられているかいないかにかわらず不揮発的にストアしなくてもよい<u>データを揮発的に記憶する</u>第1メモリセルをシャットダウンした後、残りの第2メモリセルをストア動作するための消費電力を抑制できる。また、ストアレイテンシを削減できる。

# [0123]

図4および図5のように、セルアレイ20は、各々のブロック24が少なくとも2つのメモリセル10を含む複数のブロック24に分割されている。図8のステップS40のように、制御回路28は、セルアレイ20をシャットダウン(電源遮断)するときに、複数のブロック24からブロック24内のメモリセル10が揮発的に書き換えられているかいないかにかわらず、不揮発的にストアしなくてもよいデータを揮発的に記憶する1または複数の第1ブロック(すなわちUDFがセットされたブロック)を抽出する。図8のステップS42および図9(a)のように、制御回路28は、第1ブロックをシャットダウンする。図8のステップS46および図9(b)のように、制御回路28は、第1ブロックをシャットダウンした後,複数のブロック24のうち残りの1または複数の第2ブロック内のメモリセル10において双安定回路12に記憶されたデータを不揮発性素子にストアするストア動作を行う。図8のステップS48および図9(c)のように、制御回路28は、ストア動作の終了した第2ブロックをシャットダウンする。

### [0124]

このように、ブロック24毎に、UDFがセットされた第1ブロックをシャットダウンするため、第1ブロックをストア動作するための消費電力を抑制できる。また、ストアレイテンシを削減できる。また、UDFがセットされた第1ブロックを最初にシャットダウンするため、ストア動作を待機するときのリーク電流に起因する消費電力を削減できる。

# [0125]

図9(a)のように、制御回路28は、抽出された第1ブロックを全てシャットダウンした後、図9(b)から図9(d)のように、残りの第2ブロック内のメモリセル10においてストア動作を行う。これにより、UDFがセットされた第1ブロックがシャットダウンを待機するときの消費電力を削減できる。

# [0126]

レジスタ40(記憶回路)は、セルアレイ20の外に設けられ、外部回路から受信した

20

30

40

50

UDF(不揮発的にストアしなくてもよい<u>データを揮発的に記憶する</u>第1ブロックを示す情報)を記憶する。制御回路28は、UDFに基づき、第1プロックを抽出する。これにより、UDFを記憶する記憶回路を各サブアレイ22またはブロック24に設ける方法に比べ、UDFをバス25等を介し制御回路28に転送しなくてもよく、制御が簡単になる

# [0127]

図8のステップS40のように、制御回路28は、複数のブロック24から、UDFがセットされたブロックと、SFBFがセットされたブロック24(すなわちブロック24 内のいずれのメモリセル10も揮発的に書き換えられていないブロック)と、を第1ブロックとして抽出する。これにより、UDFがセットされたブロックとSFBFがセットされたブロックを最初にシャットダウンするため、ストア動作を待機するときのリーク電流に起因する消費電力を削減できる。また、ストアレイテンシを低減できる。

# [0128]

レジスタ41(記憶回路)は、セルアレイ20の外に設けられている。これにより、SFBFを各サプアレイ22またはブロック24に記憶する方法に比べ、SFBFをバス25等を介し制御回路28に転送しなくてもよく、制御が簡単になる。

#### [0129]

実施例 1 において、MTJ 1 およびMTJ 2 がノードQおよびQBにそれぞれ接続される例を説明したが、ノードQまたはQBにMTJ 1 およびMTJ 2 のいずれか一方が接続されていればよい。メモリセルは、双安定回路 1 2 と不揮発性素子を有していればよい。不揮発性素子としてMTJを例に説明したが、不揮発性素子としては巨大磁気抵抗(GMR)素子、ReRAM(Resistance Random Access Memory)に用いられるような可変抵抗素子、または、PRAM(Phase change RAM)に用いられる相変化素子を用いることができる。

### 【実施例2】

# [0130]

特許文献 5 <u>の技術</u>をセルアレイに適用する場合、 V N R - S R A MのU L V リテンションは B I (ブーステッドインバータ) モードから S T (シュミットトリガ) モードにモードを切り替えた後に電源電圧を低下させることにより行う。 セルアレイのサイズが大きくなると、モード切り替えを待機するメモリセルにおけるリーク電流に起因する消費電力が大きくなる。また、待機期間によりレイテンシが増加する。また、メモリセルのデータが不要なデータであってもリテンションを行ってしまう。これにより、消費電力およびレイテンシが増大する。

# [0131]

実施例 2 は、消費電力および消費エネルギーを抑制することを目的とする。具体的には、PG時(リテンション時)、PGへの移行およびPGからの復帰における消費電力および消費エネルギーを削減すること、およびPGに関するBETを削減することを目的とする。

### [0132]

実施例2では、セルアレイにデータを書き込むとき、またはデータを処理するときに電源復帰後に不要となるデータの存在するメモリセルをシャットダウンし、残りのメモリセルをリテンションする。これにより、リテンション不要なデータを記憶するメモリセルのモード切り替えが不要なため消費電力およびレイテンシを抑制できる。

### [0133]

より具体的に、セルアレイを複数のブロックに分割する。電源復帰後に不要となるデータの存在するメモリセルを有するブロックを指定するUDFを生成する。リテンションのときには、UDFに基づき、リテンション不要な<u>データを記憶する</u>ブロックをシャットダウンする。その後、その他のブロックにおいてリテンションを行う。これにより、リテンション不要な<u>データを記憶する</u>ブロックのモード切り替えが不要なため消費電力およびレイテンシを抑制できる。また、リテンション不要な<u>データを記憶する</u>ブロックをシャット

ダウンするため消費電力をより削減できる。

### [0134]

以下、実施例2の詳細な例について説明する。

#### 「メモリセルの説明]

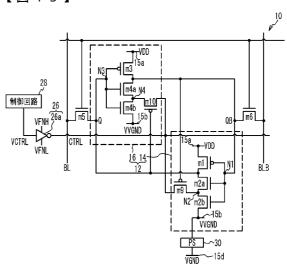

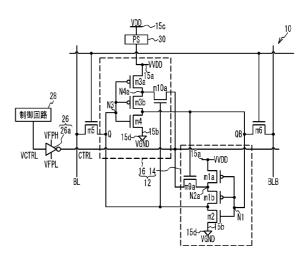

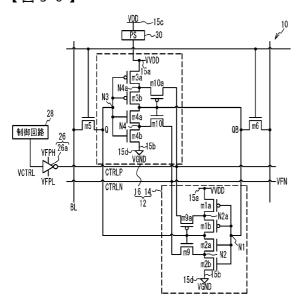

図 1 7 は、実施例 2 におけるメモリセルの回路図である。図 1 7 に示すように、メモリセル 1 0 は、インバータ回路 1 4 および 1 6 を主に備えている。

### [0135]

インバータ回路14および16はループ状に接続され双安定回路12を構成している。インバータ回路14は、FETm1、m2a、m2bおよびm9を備えている。インバータ回路16は、FETm3、m4a、m4bおよびm10を備えている。FETm1およびm3はPチャネルMOSFETであり、FETm2a、m2b、m4a、m4b、m9およびm10はNチャネルMOSFETである。FETm1およびm3のソースは仮想電源電圧VVDDが印加された電源線15aに接続され、ドレインはノードQおよびQBに接続されている。FETm2aおよびm2bはノードQとグランド電圧VGNDが印加されたグランド線15bとの間に直列に接続されている。FETm4aおよびm4bも同様にノードQBとグランド線15bとの間に接続されている。

#### [0136]

インバータ回路 1 4 の入力ノードは F E T m 1、 m 2 a および m 2 b が共通に接続されたノード N 1 であり、インバータ回路 1 4 の出力ノードはノード Q である。インバータ回路 1 6 の入力ノードは F E T m 3、 m 4 a および m 4 b が共通に接続されたノード N 3 であり、インバータ回路 1 6 の出力ノードはノード Q B である。インバータ回路 1 4 の入力ノードおよび出力ノードはそれぞれインバータ回路 1 6 の出力ノードおよび入力ノードに接続されている。

### [0137]

FETm9のソースおよびドレインの一方はFETm2aとm2bとの間のノードN2に接続され、他方は制御線CTRLに接続され、ゲートはノードQに接続されている。FETm10のソースおよびドレインの一方はFETm4aとm4bとの間のノードN4に接続され、他方は制御線CTRLに接続され、ゲートはノードQBに接続されている。

### [0138]

インバータ26aは制御線CTRL用のドライバ26であり、制御信号VCTRLを反転し、ハイレベルの電圧が電圧VSCTRLおよびローレベルの電圧が電圧VLCTRLの制御信号を出力する。制御信号VCTRLがハイレベルのとき制御線CTRLはVLCTRLとなり、インバータ回路14および16はBIモードとなる。制御信号VCTRLがローレベルのとき制御線CTRLはVSCTRLとなり、インバータ回路14および16はSTモードとなる。

### [0139]

ノードQおよびQBは、それぞれMOSFETm5およびm6を介しビット線BLおよびBLBに接続されている。MOSFETm5およびm6のゲートはワード線WLに接続されている。

# [0140]

BIモードは、インバータ回路14および16の伝達特性にヒステリシスを実質的に有さず、かつ高速動作可能なモードである。STモードは、インバータ回路14および16の伝達特性にヒステリシスを有し、かつ動作が遅いモードである。なお、ヒステリシスを実質的に有さないとはSTモードのような意図的なヒステリシスを有さないことであり、意図しないヒステリシスを有することを許容する。

# [0141]

B I モードでは、メモリセル10は、通常のSRAMセルとして機能する。STモードでは、電源電圧(VVDD-VGND)を例えば0.2Vと超低電圧(ULV:Ultralow Voltage)としても双安定回路12のデータを保持する。

10

20

30

40

### [0142]

# [0143]

低電圧の電源15clと電源線15aとの間にパワースイッチPS3およびFETm11が直列に接続されている。パワースイッチPS3およびFETm11はそれぞれPチャネルFETおよびNチャネルFETである。FETm11は負荷として機能する。パワースイッチPS3のゲートにPS制御信号VPG3が印加される。パワースイッチPS3およびFETm11の基板バイアスは例えばそれぞれVDDLおよびVDDHである。実施例1と同様に、パワースイッチ30は、グランド線15bとグランド15dとの間に設けられていてもよい。パワースイッチ30は、電源線15aと電源15chおよび15clの少なくとも一方との間と、グランド線15bとグランド15dとの間の両方に設けられていてもよい。

### [0144]

# 「各状態の説明]

図 1 8 ( a ) および図 1 8 ( b ) は、実施例 2 における各状態に印加される電圧を示す図である。図 1 8 ( a ) のように、スタンバイ状態では V P G 1 、 V P G 2 および V P G 3 はそれぞれローレベル L 、ローレベル L およびハイレベル H である。パワースイッチ P S 1 、 P S 2 および P S 3 はそれぞれオン、オフおよびオフとなる。これにより、電源電圧 V V D D - V G N D は電圧 V 3 となる。電圧 V 3 は例えば 1 . 2 V である。

#### [ 0 1 4 5 ]

スリープ状態では VPG1、 VPG2 および VPG3 はそれぞれ H、 H および H である。  $\mathcal{N}$  クースイッチ PS1、 PS2 および PS3 はそれぞれオフ、オンおよびオフとなる。 これにより、電源電圧 VVDD-VGND は電圧 V3 より低い電圧 V2 となる。 電圧 V2 は例えば V3 の V3 の V4 の V5 の

### [0146]

# [0147]

# [0148]

図18(b)に示すように、スタンバイ状態では、電源電圧VVDD-VGNDは電圧V3である。制御信号VCTRLはLの場合とHの場合があり、VCTRLがHのときメモリセル10はBIモードであり、VCTRLがLのときメモリセル10はSTモードである。スタンバイ(BI)状態は、実施例1のリード/ライト状態と同じであり、通常のSRAMとして双安定回路12のデータを書き換えが可能な状態である。電源電圧VVDD-VGNDは、双安定回路12がデータの書き換えが可能でかつデータが保持できる電圧V3である。

# [0149]

スリープ状態では、電源電圧 V V D D - V G N D は電圧 V 3 より低い電圧 V 2 である。 制御信号 V C T R L は L の場合と H の場合があり、 V C T R L が H のときメモリセル 1 0 10

20

30

40

20

30

40

50

はBIモードであり、VCTRLがLのときメモリセル10はSTモードである。電源電圧VVDD-VGNDは、双安定回路12がデータの書き換えはできないがデータが保持できる電圧V2である。電圧V2は電圧V3より低いため、消費電力を抑制できる。

#### [0150]

リテンション状態では、電源電圧VVDD・VGNDは電圧V2より低い電圧V1である。制御信号VCTRLはLでありメモリセル10はSTモードである。電源電圧VVDD・VGNDは、双安定回路12がBIモードではデータを保持できないが、STモードではデータが保持できる電圧V1である。リテンション状態ではメモリセル10が擬似不揮発性の状態であり、電圧V1を電圧V2より低くできるため、消費電力を非常に抑制できる。

# [0151]

シャットダウン状態では、電源電圧 VVDD-VGNDは電圧 V1 より低い電圧 V1 である。制御信号 VCTRL は VDD-VG は VDC は VDC

#### [0152]

図19(a)および図19(b)は、実施例2におけるリテンションおよびシャットダウンに印加される電圧を示す図である。図19(a)に示すように、スタンバイ状態では、電源電圧VVDD・VGNDは電圧V3、制御信号VCTRLはHであり、BIモードである。モード切り替え期間では、まずVCTRLをLとする。これにより、STモードとなる。その後、電源電圧VVDD・VGNDを電圧V1とする。これにより、リテンション状態となる。その後モード切り替え期間において電源電圧VVDD・VGNDを電圧V3とする。その後、VCTRLをHとする。これによりスタンバイ状態に戻る。このようにリテンション状態とする前後にはモード切り替えを行う。

# [0153]

図19(b)に示すように、スタンバイ状態において、電源電圧VVDD-VGNDを電圧V0とするとシャットダウン状態となる。このとき、VCTRLはHを維持しBIモードを維持する。電源電圧VVDD-VGNDを電圧V3とすると、スタンバイ状態に戻る。

# [0154]

図20は、実施例2における各期間の消費電力を示す図である。実線は図17に示したメモリセル10(VNR-SRAM)を有する記憶回路の消費電力(パワー)を示す。点線は、6トランジスタSRAM(6T-SRAM)セルを用いた記憶回路の消費電力を示している。

# [0155]

図20に示すように、メモリセル10の動作期間には、スタンバイ期間、モード切り替え期間およびリテンション期間がある。スタンバイ期間の長さを NLとする。リテンション期間前のモード切り替え期間の長さを ENTとする。リテンション期間の長さを SDとする。リテンション期間後のモード切り替え期間の長さを ENTとする。

### [0156]

VNR-SRAMのスタンバイ期間の消費電力は6T-SRAMの消費電力よりPLK G大きい。これは、FETm9 およびm10 のリーク電流に起因する。VNR-SRAM では、モード切り替え期間にモード切り替えのための消費電力が必要となる。リテンション期間では、VNR-SRAMの消費電力は $P^*Save$ であり、VNR-SRAMでは 6T-SRAMより消費電力をPSave削減できる。

# [0157]

VNR-SRAMセルの6T-SRAMセルに対するエネルギーの増加は、スタンバイ期間における  $P_{LKG}$ によるエネルギー増加  $E_{LKG}$ 、モード切り替え期間のエネルギー増加  $E_{EXT}$  および  $E_{ENT}$  の合計である。 V NR-SRAMセルがリテンションにより節約できるエネルギーは、リテンション期間における  $P_{Save}$  によるエネルギー減少  $E_{Save}$  である。  $E_{LKG}$  +  $E_{EXT}$  +  $E_{ENT}$  =  $P_{Save}$  × B E T となる。 双安定回

30

40

50

路 1 2 のリード / ライトが行われない待機期間が B E T 以上のときはリテンション状態とし、 B E T 以下のときはスタンバイ状態とする。これにより、極めて高効率にエネルギーを削減できる。

#### [0158]

図 2 1 (a) および図 2 1 (b) は、実施例 2 におけるメモリセルの別の例である。図 2 1 (a) に示すように、インバータ回路 1 4 は、FETm 1 a、m 1 b、m 2 およびm 9 aを備え、インバータ回路 1 6 は、FETm 3 a、m 3 b、m 4 およびm 1 0 aを備える。FETm 1 a、m 1 b、m 3 a、m 3 b、m 9 aおよびm 1 0 aはPチャネルFETであり、FETm 2 およびm 4 はNチャネルFETである。FETm 9 aのソースおよびドレインの一方はFETm 1 aとm 1 bとの間のノードN 2 aに接続され、FETm 1 0 aのソースおよびドレインの一方はFETm 3 aとm 3 bとの間のノードN 4 aに接続されている。

# [0159]

ドライバ26は、インバータ26aの前段にインバータ26cを備えている。VCTRLがLのとき、インバータ26cはVDDを出力し、インバータ26aはCTRLとしてVLCTRLを出力し、インバータ回路14および16はBIモードとなる。VCTRLがHのとき、インバータ26cはVGNDを出力し、インバータ26aはCTRLとしてVSCTRLを出力し、インバータ回路14および16はSTモードとなる。その他の構成は図17と同じであり説明を省略する。インバータ26cの電源電圧および接地電圧をVDDおよびVGNDとしているが、インバータ26aと同様に電源電圧および接地電圧をVSCTRLおよびVLCTRLとしてもよい。ドライバ26は、インバータ26aと

### [0160]

図 2 1 ( b ) に示すように、インバータ回路 1 4 は、FETm 1 a、m 1 b、m 2 a、m 2 b、m 9 およびm 9 aを備え、インバータ回路 1 6 は、FETm 3 a、m 3 b、m 4 a、m 4 b、m 1 0 およびm 1 0 aを備える。FETm 1 a、m 1 b、m 3 a、m 3 b、m 9 a およびm 1 0 a は P チャネルFETであり、FETm 2 a、m 2 b、m 4 a およびm 4 b、m 9 およびm 1 0 は N チャネルFETである。

# [0161]

FETm9 a およびFETm 1 0 a のソースおよびドレインの他方は制御線CTRLPに接続され、FETm9 およびFETm 1 0 のソースおよびドレインの他方は制御線CTRLP RLNに接続されている。ドライバ 2 6 はインバータ 2 6 a および 2 6 b を備えている。インバータ 2 6 a は制御線CTRLNに<u>信号を</u>出力する。インバータ 2 6 b はインバータ 2 6 a の出力を反転し制御線CTRLPに出力する。その他の構成は図 1 7 および図 2 1 (a)と同じであり説明を省略する。

# [0162]

#### [0163]

# 「電子回路の説明]

図22は、実施例2における電子回路を示すブロック図である。図22に示すように、電子回路102は、セルアレイ20、制御回路28を備えている。セルアレイ20は、複数のサブアレイ22に分割されている。サブアレイ22の記憶容量は例えば8kバイトである。サブアレイ22には複数のメモリセル10がマトリックス状に設けられている。サブアレイ22はバス25に接続されている。サブアレイ22の個数は適宜設計可能である

# [0164]

サブアレイ22にはパワースイッチ30および周辺回路38が設けられている。パワー

スイッチ30はサブアレイ22毎に電源電圧を設定する。周辺回路38はモード制御信号に基づき、各メモリセル10のモードを制御する。

#### [0165]

制御回路28はレジスタ40を備えている。制御回路28が外部回路から受信したブロックごとのUDFをレジスタ40に格納する。制御回路28は、PS制御信号を用い各サブアレイ22のパワースイッチ30を制御する。制御回路28はバス25を介しサブアレイ22へのデータの入出力を行う。制御回路28の少なくとも一部の機能は外部のCPU等のプロセッサ回路がソフトウエアと協働で行ってもよい。

# [0166]

#### 「サブアレイの説明 1

図23は、実施例2におけるサブアレイのブロック図である。図23に示すように、サブアレイ22は、メモリセル10を有する複数のブロック24(例えば8個)に分割されている。ブロック24の記憶容量は例えば1kバイトである。ブロック24の個数は適宜設計可能である。サブアレイ22内には複数のメモリセル10がマトリックス状に配置されている。サブアレイ22内には、行方向にワード線WLおよび制御線CTRLが延伸し、列方向にビット線BLが延伸している。各メモリセル10には、ワード線WL、ビット線BL、制御線CTRL、電源線15aおよびグランド線15bが接続されている。

### [0167]

各サブアレイ22に対応し、パワースイッチ30および周辺回路38が設けられている。制御回路28は、パワースイッチ30および周辺回路38を制御する。

### [0168]

パワースイッチ30は、ブロック24毎に電源電圧VVDD-VGNDを電圧V3、V2、V1およびV0にできる。周辺回路38は、WLデコーダ31、列デコーダ32、プリチャージ回路33および読出書込回路34を備えている。

#### [0169]

スタンバイ期間において、WLデコーダ31は行アドレスに基づきワード線WLを選択する。列デコーダ32は列アドレスに基づきビット線BLを選択する。プリチャージ回路33はビット線BLをプリチャージする。読出書込回路34は、WLデコーダ31および列デコーダ32に選択されたメモリセル10の双安定回路12にデータを書き込みまたは双安定回路12からデータを読み出しバス25に出力する。

# [0170]

リテンション期間において、制御回路 2 8 は 1 または複数のメモリセル 1 0 を S T モードとし、 V V D D を電圧 V 1 とする。これにより、メモリセル 1 0 はリテンション状態となる。

# [0171]

# [動作の説明]

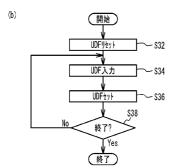

図24は、実施例2における動作を示すフローチャートである。図24に示すように、制御回路28は、外部回路からの指令によりセルアレイ20の電源を投入する(ステップS10)。例えば、制御回路28は、全てのブロック24のメモリセル10をBIモードとし、パワースイッチPS1をオンし、パワースイッチPS3をオフする。これにより、全てのブロック24がスタンバイ状態となる。

# [0172]

制御回路 2 8 は、スタンバイ状態でリードおよびライト動作を行う(ステップS12)。制御回路 2 8 は、外部回路からセルアレイ 2 0 をシャットダウンする指示を受けたか否か判定する(ステップS14)。NoのときステップS12に戻る。Yesのとき、制御回路 2 8 は、リテンション動作およびシャットダウンを行う(ステップS17)。その後終了しステップS10に戻る。

# [0173]

# [UDF設定の説明]

UDFを設定する動作は実施例1の図7(b)と同じであり説明を省略する。

10

20

30

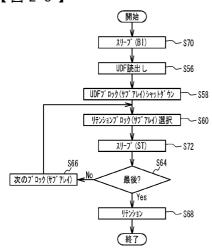

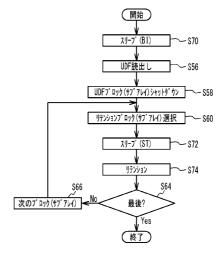

# [0174]

[ リテンション動作のタイプ A の説明 ]

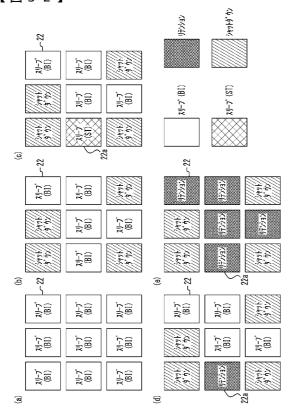

図24のステップS17の動作としてリテンション動作のタイプAについて説明する。図25は、実施例2におけるリテンション動作のタイプAを示すフローチャートである。図26(a)から図26(e)は、実施例2におけるリテンション動作のタイプAにおけるセルアレイを示す模式図である。図27(a)から図27(e)は、実施例2におけるリテンション動作のタイプAにおけるセルアレイおよびブロックを示す模式図である。図26(a)から図26(e)はサプアレイ22毎にリテンション動作を行う例であり、図27(a)から図27(e)はブロック24毎にリテンション動作を行う例である。サプアレイ22毎にリテンション動作を行う場合もブロック24毎にリテンション動作を行う場合も基本的な動作は同じである。リテンション動作のタイプBおよびCでも同様である

# [0175]

図 2 4 のステップ S 1 7 において制御回路 2 8 がリテンション動作を開始する。図 2 5 に示すように、このとき、各ブロック 2 4 (またはサブアレイ 2 2 ) はスタンバイ ( B I ) 状態となっている (ステップ S 5 4 )。例えば制御回路 2 8 は全てのブロック 2 4 (サブアレイ 2 2 ) の電源電圧 V V D D - V G N D を電圧 V 3 とし、制御信号 V C T R L を H とする。図 2 6 ( a ) のように、全てのサブアレイ 2 2 はスタンバイ ( B I ) 状態である。図 2 7 ( a ) のように、全てのプロック 2 4 はスタンバイ ( B I ) 状態である。

### [0176]

制御回路28はブロック24(またはサブアレイ22)に対応するUDFをレジスタ40からそれぞれ読み出す(ステップS56)。制御回路28は、UDFがセットされた(例えばハイレベルHの)ブロック24(サブアレイ22)を抽出し、一括してシャットダウンする(ステップS58)。例えば制御回路28は、対応するブロック24(サブアレイ22)の電源電圧VVDD-VGNDを電圧V0とする。図26(b)に示すように、制御回路28は9個のサブアレイ22のうち、4個のサブアレイ22を一括してシャットダウン状態とする。図27(b)に示すように、制御回路28は72個のブロック24のうち、28個のブロック24を一括してシャットダウン状態とする。

# [0177]

制御回路28は、UDFがセットされていない(すなわちリテンション対象の)最初のブロック24a(サブアレイ22a)を選択する(ステップS60)。制御回路28は最初のブロック24a(サブアレイ22a)をスタンバイ(ST)<u>状態</u>とする(ステップS62)。例えば制御回路28はブロック24a(サブアレイ22a)の電源電圧VVDD-VGNDを電圧V3とした状態で、制御信号VCTRLをLとする。図26(c)に示すように、サブアレイ22aはスタンバイ(ST)状態となる。図27(c)に示すように、ブロック24aはスタンバイ(ST)状態となる。

#### [0178]

制御回路28は最後のブロック24(サブアレイ22)か判定する(ステップS64)。Noのとき、次のブロック24(サブアレイ22)に進み(ステップS66)、ステップS60に戻る。順次、リテンション対象のブロック24(サブアレイ22)をスタンバイ(ST)状態とする。図26(d)のように、全てのリテンション対象のサブアレイ22がスタンバイ(ST)状態となる。図27(d)のように、全てのリテンション対象のブロック24がスタンバイ(ST)状態となる。

### [0179]

ステップS64においてYesと判定されると、制御回路28は全てのリテンション対象のブロック24(サブアレイ22)を一括あるいは複数のブロック24(サブアレイ22)毎にリテンション状態とする(ステップS68)。図26(e)のように、全てのリテンション対象のサブアレイ22がリテンション状態となる。図27(e)のように、全てのリテンション対象のブロック24がリテンション状態となる。その後終了する。

# [0180]

10

20

30

40

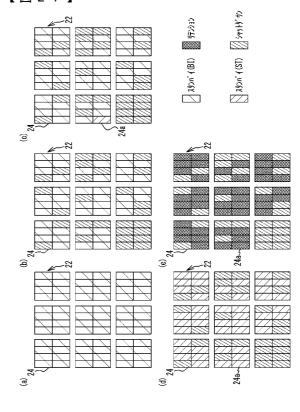

# [リテンション動作のタイプBの説明]

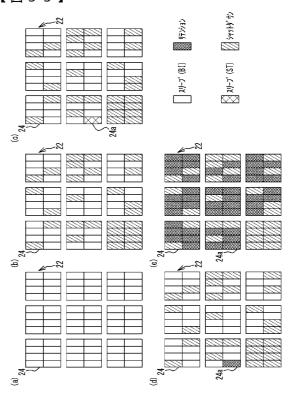

リテンション動作のタイプBについて説明する。図28は、実施例2におけるリテンション動作のタイプBを示すフローチャートである。図29(a)から図29(e)は、実施例2におけるリテンション動作のタイプBにおけるセルアレイを示す模式図である。図30(a)から図30(e)は、実施例2におけるリテンション動作のタイプBにおけるセルアレイおよびブロックを示す模式図である。

# [0181]

図28に示すように、制御回路28は、各ブロック24(またはサブアレイ22)をスリープ(BI)状態とする(ステップS70)。例えば制御回路28は全てのブロック24(サブアレイ22)の電源電圧VVDD-VGNDを電圧V2とし、制御信号VCTRLをHとする。図29(a)のように、全てのサブアレイ22はスリープ(BI)状態である。図30(a)のように、全てのブロック24はスリープ(BI)状態である。

#### [0182]

制御回路28はステップS56において読み出したUDFがセットされた(例えばハイレベルHの)ブロック24(サブアレイ22)を抽出し、一括してシャットダウンする(ステップS58)。図29(b)に示すように、制御回路28は4個のサブアレイ22を一括してシャットダウン状態とする。図30(b)に示すように、制御回路28は28個のブロック24を一括してシャットダウン状態とする。

# [0183]

制御回路28はステップS60において選択された最初のブロック24a(サブアレイ22a)をスリープ(ST)状態とする(ステップS72)。例えば制御回路28はブロック24a(サブアレイ22a)の電源電圧VVDD-VGNDを電圧V2とし、制御信号VCTRLをLとする。図29(c)に示すように、サブアレイ22aはスリープ(ST)状態となる。図30(c)に示すように、ブロック24aはスリープ(ST)状態となる。

# [0184]

ステップS64においてNoと判定されると、次のブロック24(サブアレイ22)についてステップS60およびS72を行う。図29(d)のように、全てのリテンション対象のサブアレイ22がスリープ(ST)状態となる。図30(d)のように、全てのリテンション対象のブロック24がスリープ(ST)状態となる。

# [0185]

ステップS64においてYesと判定されると、制御回路28は全てのリテンション対象のブロック24(サブアレイ22)を一括してリテンション状態とする(ステップS68)。図29(e)のように、全てのリテンション対象のサブアレイ22がリテンション状態となる。図30(e)のように、全てのリテンション対象のブロック24がリテンション状態となる。その後終了する。その他の動作はリテンション動作のタイプAと同じである。

# [0186]

### 「リテンション動作のタイプCの説明 1

リテンション動作のタイプ C について説明する。図31は、実施例2におけるリテンション動作のタイプ C を示すフローチャートである。図32(a)から図32(e)は、リテンション動作のタイプ C におけるセルアレイを示す模式図である。図33(a)から図33(e)は、リテンション動作のタイプ C におけるセルアレイおよびブロックを示す模式図である。

# [0187]

# [0188]

50

40

10

20

ステップ S 7 2 において、制御回路 2 8 は、リテンション対象の最初のブロック 2 4 a (またはサブアレイ 2 2 a)をスリープ (S T)状態とした後、ブロック 2 4 a (またはサブアレイ 2 2 a)をリテンション状態とする (ステップ S 7 4 )。図 3 2 (d)に示すように、サブアレイ 2 2 a はリテンション状態となる。図 3 3 (d)に示すように、ブロック 2 4 a はリテンション状態となる。

### [0189]

その後、リテンション対象のブロック24(サブアレイ22)を順次スリープ(ST)状態とし(ステップS72)、その後リテンション状態とする(ステップS74)。ステップS64においてYesと判定されたとき、図32(e)のように、全てのリテンション対象のサブアレイ22がリテンション状態となる。図33(e)のように、全てのリテンション対象のブロック24がリテンション状態となる。その後終了する。その他の動作はリテンション動作のタイプBと同じである。

# [0190]

「リテンション動作のタイプBの制御回路の例 ]

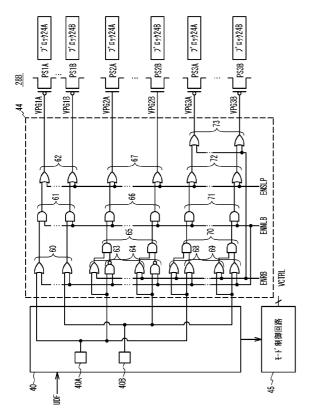

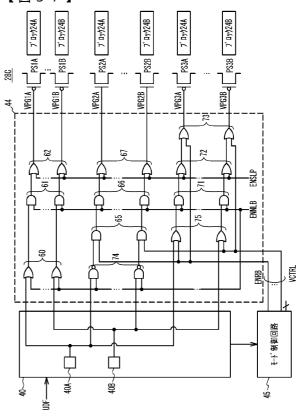

図34は、リテンション動作のタイプBにおける制御回路の例を示すブロック図である。制御回路28Bは、レジスタ40、モード制御回路45およびPS制御回路44を備えている。レジスタ40のビット数は各々ブロック24の個数のNSA×Nblock以上である。NSA×Nblock個のブロック24のうちブロック24Aから24Bについて説明する。

# [0191]

実施例1の図7(b)のステップS32と同様に、全ての記憶部40Aから40BがローレベルLにリセットされる。ステップS34において制御回路28BにUDFが入力すると、ステップS36において、対応するブロック24Aから24Bの記憶部40Aから40BがハイレベルHにセットされる。

#### [0192]

モード制御回路 4 5 は、モード制御信号 V C T R L を出力する。 P S 制御回路 4 4 は、レジスタ 4 0 に保持された U D F に基づき各ブロック 2 4 A から 2 4 B のパワースイッチ P S 1 A から P S 1 B、 P S 2 A から P S 2 B および P S 3 A から P S 3 B を制御する。 【 0 1 9 3 】

P S 制御回路 4 4 は、各々ブロック 2 4 A から 2 4 B の個数の O R 回路 6 0、 A N D 回路 6 1、 O R 回路 6 2、 O R 回路 6 3、 N A N D 回路 6 4、 A N D 回路 6 5、 A N D 回路 6 6、 O R 回路 6 7、 O R 回路 6 8、 O R 回路 6 9、 A N D 回路 7 0、 A N D 回路 7 1、 O R 回路 7 2 および O R 回路 7 3 を備えている。

# [0194]

OR回路60には、UDF記憶部40Aから40Bの出力信号と制御信号ENNLBが入力する。AND回路61にはOR回路60の出力信号と制御信号ENNLBが入力する。OR回路62にはAND回路61の出力信号と制御信号ENSLPが入力する。OR回路62からPS制御信号VPG1AからVPG1Bが出力される。PS制御信号VPG1AからVPG1Bが出力される。PS制御信号VPG1AからPFG1Bのゲートに入力する。

#### [0195]

OR回路63にはUDF記憶部40Aから40Bの出力信号と制御信号ENRBが入力する。NAND回路64にはUDF記憶部40Aから40Bの出力信号と制御信号ENRBが入力する。AND回路65にはOR回路63の出力信号とNAND回路64の出力信号が入力する。AND回路65にはAND回路65の出力信号と制御信号ENNLBが入力する。OR回路67にはAND回路65の出力信号と制御信号ENSLPが入力する。OR回路67からPS制御信号VPG2AからVPG2Bが出力される。PS制御信号VPG2AからVPG2Bが出力される。PS制御信号VPG2AからVPG2Bのゲートに入力する。

# [0196]

10

20

30

20

30

40

50

OR回路68にはUDF記憶部40Aから40Bの出力信号と制御信号ENRBが入力する。OR回路69にはUDF記憶部40Aから40Bの出力信号と制御信号ENRBが入力する。AND回路70にはOR回路68の出力信号とOR回路69の出力信号が入力する。AND回路71にはAND回路70の出力信号と制御信号ENNLBが入力する。OR回路72にはAND回路71の出力信号と制御信号ENSLPが入力する。OR回路73からPS制御信号VPG3AからVPG3Bが出力される。PS制御信号VPG3AからVPG3Bはそれぞれブロック24Aから24BのパワースイッチPS3AからPS3Bのゲートに入力する。

#### [0197]

図 3 5 ( a )から図 3 5 ( e )は、リテンション動作のタイプ B における各信号  $\underline{o}$   $\underline{v}$   $\underline{v}$

#### [0198]

図 3 5 ( b ) に示すように、スリープ ( B I ) 状態では、制御信号 E N R B 、 E N N L B 、 E N S L P および V C T R L は、それぞれ H 、 L 、 H および H である。 V P G 1 A から V P G 1 B は H でありパワースイッチ P S 1 A から P S 1 B はオフである。 V P G 2 A から V P G 2 B は H でありパワースイッチ P S 2 A から P S 2 B はオンである。 V P G 3 A から V P G 3 B は H でありパワースイッチ P S 3 A から P S 3 B はオフである。このように、スリープ ( B I ) 状態では、 U D F によらず、パワースイッチ P S 1 A から P S 1 B および P S 3 A から P S 3 B がオフでありパワースイッチ P S 2 A から P S 2 B がオンである。よって全ブロック 2 4 A から 2 4 B の電源電圧 V V D D - V G N D は電圧 V 2 となりスリープ ( B I ) 状態となる。 図 2 8 のステップ S 7 0 では、 図 3 5 ( b ) のように全ブロックがスリープ ( B I ) 状態となる。

# [0199]

図 2 8 のステップS70、S56およびS58においてUDFがHのブロック24をスリープ(BI)状態とし、UDFがLのブロックを一括遮断する。図35(c)に示すように、図35(a)のスタンバイ(BI)の状態から制御信号ENNLBがLからHとなる。VPG1AからVPG1BがLからHとなり、VPG2AがLからHとなる。これにより、パワースイッチPS2Aはオフからオンになる。パワースイッチPS1AおよびPS1Bはオンからオフになる。パワースイッチPS2B、PS3AおよびPS3Bはオフを維持する。よって、リテンション対象のブロック24Aの電源電圧VVDD-VGNDは電圧V3からV2となり、ブロック24Aはスリープ(BI)状態となる。UDFがセットされたブロック24Bの電源電圧VVDD-VGNDは電圧V0となり、ブロック24Bはシャットダウン状態となる。

### [0200]

図 2 8 のステップ S 7 2 においてブロック 2 4 A をスリープ (BI) <u>状態</u>からスリープ (ST) <u>状態</u>に切り替える。図 3 5 (d)に示すように、制御信号 E N R B、E N N L B および E N S L P は図 3 5 (c) の状態を維持する。各パワースイッチの状態は変わらず、ブロック 2 4 A および 2 4 B の電源電圧 V V D D - V G N D はそれぞれ電圧 V 2 および V 0 が維持される。制御信号 V C T R L は H から L となる。これにより、対象となるブロック 2 4 A のモードが B I モードから S T モードに切り替わる。これにより、ブロック 2

4 A はスリープ(ST)状態となる。

### [0201]

図 2 8 のステップ S 6 0 から S 6 6 のループを行うことにより、全てのリテンション対象のブロック 2 4 について、スリープ (BI)状態をスリープ (ST)状態に切り替える

# [0202]

図 2 8 のステップ S 6 8 において、全てのリテンション対象のブロック 2 4 A をスリープ (ST) 状態からリテンション状態とする。図 3 5 (e)に示すように、制御信号 E N N L B、E N S L Pおよび V C T R L は図 3 5 (d)の状態を維持し、制御信号 E N R Bを H から L とする。これにより、V P G 2 A および V P G 3 A が H から L となり、パワースイッチ P S 2 A がオンからオフとなり、パワースイッチ P S 3 A がオフからオンになる。これにより、リテンション対象のブロック 2 4 A の電源電圧 V V D D・V G N D が電圧 V 2 から電圧 V 1 となり、全てのリテンション対象のブロック 2 4 A はリテンション状態となる。ブロック 2 4 B の電源電圧 V V D D・V G N D は電圧 V 0 が維持される。

#### [0203]

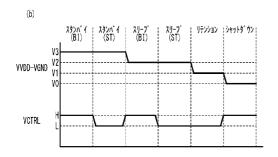

図 3 6 は、リテンション動作のタイプ B における制御信号のタイミングチャートである。制御信号 V C T R L 1 ~ V C T R L n は各プロック 2 4 1 ~ 2 4 n に対応する制御信号 V C T R L である。ブロック 2 4 1 ~ 2 4 k はリテンション対象のプロックであり、ブロック 2 4 k + 1 ~ ブロック 2 4 n はシャットダウン対象のプロックである。

# [0204]

図36に示すように、時刻 t 20 と t 21 との間はスタンバイ(BI)期間であり、制御信号 ENNLBおよび ENSLPはL、ENRBおよび VCTRL1~VCTRLnはHである。時刻 t 21 と t 22 との間はスリープ(BI)期間であり、制御信号 ENSLPはHである。

### [0205]

時刻 t 2 3 (図 2 8 のステップ S 5 8 ) において、制御信号 E N N L B が H となる。これにより、リテンション対象のブロック 2 4 1 ~ 2 4 k はスリープ ( B I ) 状態を維持し、U D F のブロック 2 4 k + 1 ~ 2 4 n はシャットダウン状態となる。この状態は期間 T 1 である。

### [0206]

# [0207]

図 2 8 のステップ S 6 0 から S 6 6 のループを行うことにより、全てのリテンション対象のブロック 2 4 1 ~ 2 4 k について順次ステップ S 6 8を行う。全てのリテンション対象のブロック 2 4 1 ~ 2 4 k について B I モードが S T モードに切り替わる。時刻 t 2 6 (図 2 8 のステップ S 6 8) において、制御信号 E N R B が L となる。これにより、全てのリテンション対象のブロック 2 4 1 ~ 2 4 n がリテンション状態となる。

### [0208]

時刻 t 2 7 において、制御信号 E N R B が H となる。これにより、リテンション対象のプロック 2 4 1 ~ 2 4 k はスリープ (ST) 状態となる。制御信号 V C T R L 1 ~ V C T R L k を順次 H とする。プロック 2 4 1 ~ 2 4 k は順次スリープ (BI) 状態となる。時刻 t 2 8 において、S T モードから B I モードへのモードの切り替えが終了する。

# [0209]

[リテンション動作のタイプ C の制御回路の例]

10

20

30

40

20

30

40

50

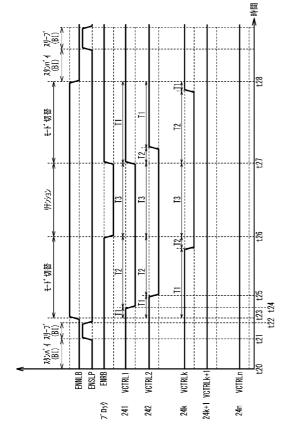

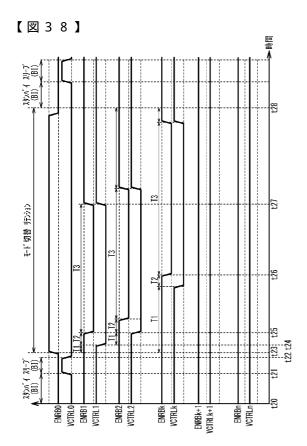

図37は、リテンション動作のタイプ C における制御回路の例を示すブロック図である。制御回路28Cは、図34の制御回路28Bに対し、OR回路63、NAND回路64およびAND回路65がNAND回路74に置き換わり、OR回路68、69およびAND回路70がOR回路75に置き換わっている。モード制御回路45はブロック24Aから24B毎に制御信号ENRBを出力する。

### [0210]

NAND回路74にはUDF記憶部40Aから40Bの出力信号と制御信号ENNLBが入力する。AND回路65にはNAND回路74の出力信号とブロック24Aから24B毎の制御信号ENRBが入力する。OR回路75にはUDF記憶部40Aから40Bの出力信号とブロック24Aから24B毎の制御信号ENRBが入力する。OR回路75の出力信号はAND回路71に入力する。その他の構成は図34の制御回路28Bと同じであり説明を省略する。制御回路28Cではブロック24Aから24B毎にリテンションすることができる。

### [0211]

各信号<u>のレベル</u>とパワースイッチの動作は、図 3 5 ( a ) から図 3 5 ( e ) と同様であり説明を省略する。

### [0212]

図38は、リテンション動作のタイプ C における制御信号のタイミングチャートである。制御信号 E N R B 1 ~ E N R B n は各ブロック 2 4 1 から 2 4 n に対応する制御信号 E N R B である。

### [0213]

図38に示すように、時刻t20からt23の間では、制御信号ENRB1からENRBnはHである。その他は図36と同じである。

#### [0214]

時刻 t 2 4 (図 3 1 のステップ S 7 2 ) において、リテンション対象の最初のブロック 2 4 1 について、制御信号 V C T R L 1 が L となる。これによりブロック 2 4 1 のモードが B I モードから S T モードに切り替わり、ブロック 2 4 1 はスリープ (S T ) 状態となる。時刻 t 2 5 において、ブロック 2 4 1 について、制御信号 E N R B 1 が L となる。これにより、ブロック 2 4 1 はリテンション状態となる。リテンション対象の 2 番目のブロック 2 4 2 について、制御信号 V C T R L 2 が L となる。ブロック 2 4 2 はスリープ (S T ) 状態となる。

#### [0215]

図31のステップS60からS66のループを行うことにより、全てのリテンション対象のブロック241~24kについて順次ステップS72およびS74を行う。全てのリテンション対象のブロック241~24kについてモード切り替えおよびリテンションが終了すると、時刻t26において、全てのリテンション対象のブロック241~24nはリテンション状態となる。

# [0216]

時刻 t 2 7 以降、各ブロック 2 4 1 から 2 4 k 毎に、制御信号 E N R B 1 ~ E N R B k および制御信号 V C T R L 1 ~ V C T R L k が順次 H となる。ブロック 2 4 1 ~ 2 4 k は順次スリープ (BI) <u>状態</u>となる。時刻 t 2 8 において、S T モードから B I モードへのモード切り替えが終了する。

# [0217]

# [シミュレーション]

実施例2に係る電子回路についてBETおよびリテンションのスタンバイ(BI)状態とスタンバイ(ST)状態とのモード切り替えのレイテンシをシミュレーションした。比較例2についてもシミュレーションした。比較例2では、UDFによるサブアレイ22およびプロック24の一括遮断を行なわず、全てのプロックをスタンバイ(BI)状態とし、ブロックごとに順次モード切り替えを行う。最後に全てのブロック24を一括してリテンション状態とする。

20

30

40

50

# [0218]

シミュレーション条件は以下である。 V D D H 、 V D D L 、 V G N D 、 V S C T R L 、 V L C T R L および W L を、それぞれ1.2 V 、 0 . 2 V 、 0 V 、 0 . 3 V 、 0 . 1 V および 0 V とした。 V P G 1 の H および L をそれぞれ1.4 V および 0 V とした。 V P G 2 の H および L をそれぞれ1.2 V および - 0 . 2 V とした。 V P G 3 の H および L をそれぞれ1.4 V および 0 V とした。 V C T R L の H および L をそれぞれ1.2 V および 0 V とした。 ビット線 B L および B L B はスタンバイ状態 およびスリープ 状態 のとき1.2 V とし、リテンション状態 およびシャットダウン状態 のとき 0 V とした。 モード切り替えのときにドライバ 2 6 を充電する時間として1サブアレイ 2 2 毎に15 n s とした。サブアレイ 2 2 および ブロック 2 4 の記憶容量をそれぞれ 8 V K バイトおよび 1 V K バイトとした。

[0219]

セルアレイ 2 0 内の全メモリセルの個数に対するUDFがセットされたメモリセルの個数の比をUD割合とした。セルアレイ 2 0 の記憶容量が 3 2 k バイト、 2 5 6 k バイトおよび 2 M バイトについてシミュレーションした。

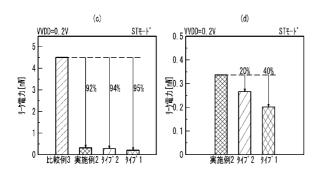

#### [0220]

図39(a)から図39(c)は、タイプAからCおよび比較例2におけるUD割合に対するBETを示す図、図39(d)から図39(f)は、UD割合に対するレイテンシを示す図である。図39(a)から図39(c)に示すように、比較例2では、UD割合によらずBETは一定である。タイプAではUD割合が0%のとき比較例2のBETと同じである。UD割合が大きくなるとBETは短くなる。タイプBではUD割合が0%のとき比較例2のBETと同じである。UD割合が大きくなるとBETは短くなる。タイプBではUD割合が0%のとき比較例2よりBETが小さい。これは、タイプBでは、リテンションの待機中のブロックのリーク電流による消費電力を抑制できるためである。タイプCではUD割合が0%のときタイプBよりBETが小さい。これは、対象となるブロックごとにスリープ(BI)状態からスリープ(ST)状態の切り替えおよびリテンションを順次行うため、スリープ(ST)状態での待機時間を短くでき消費電力を抑制できるためである。

# [0221]

図 3 9 ( d ) から図 3 9 ( f ) に示すように、タイプ A から C では比較例 2 に比べ U D 割合が大きくなるとレイテンシを削減できる。タイプ A から C の間ではレイテンシは同じである。

# [0222]

以上のシミュレーションのように、タイプAではBETは長いもののスリープ状態を設定しなくてもよいため制御が簡単である。タイプBでは、BETはタイプAとCとの間である。タイプBの制御はスリープ状態を設定するためタイプAより複雑であるが、リテンションを一括して行うためタイプCより簡単である。タイプCでは、BETは短いがリテンションを順次行うため制御が複雑である。

#### [0223]

次にUDFによる一括シャットダウンを行わず、リテンションを行うときにスタンバイ(BI)状態で待機する比較例2-1、スリープ(BI)で待機する比較例2-2およびタイプCについて、スタンバイ電力をシミュレーションした。

## [0224]

図40(a)から図40(c)は、実施例2におけるVNR SRAMと6T-SRAMとを比較する図である。6T-SRAMのスタンバイ状態およびスリープ状態のスタンバイ電力と、タイプCのVNR-SRAMのスタンバイ電力と、を比較している。図40(a)から図40(c)に示すように、6T-SRAMにおいて、スタンバイ状態からスリープ状態とするとスタンバイ電力は約30%削減できる。リテンション動作のタイプCの場合、UD割合が0%でもスタンバイ電圧を90%削減できる。UD割合が100%の場合、スタンバイ電力を99%削減できる。

# [0225]

実施例2によれば、図17、図21(a)および図21(b)のように、メモリセル1

20

30

40

50

0は、伝達特性にヒステリシスを実質的に有さないBIモード(第1モード)と伝達特性にヒステリシスを有するSTモード(第2モード)とが切り替わるインバータ回路14(第1インバータ回路)およびインバータ回路16(第2インバータ回路)を各々備える双安定回路12を有する。双安定回路12では、インバータ回路14の出力ノードおよび入力ノードはインバータ回路16のそれぞれ入力ノードおよび出力ノードに接続されている

#### [0226]

図25、図28および図31のステップS56およびS58のように、制御回路28は、複数のメモリセル10のうち保持しなくてもよいデータを記憶する1または複数の第1メモリセルをシャットダウン(電源遮断)する。ステップS62およびS72のように、制御回路28は、複数のメモリセル10のうち残りの1または複数の第2メモリセル内の双安定回路12をSTモードとし、ステップS68およびS74のように、STモードを維持した状態で第2メモリセル内の双安定回路12に電圧V1(第2電源電圧)を供給する。電圧V1は、データをリードおよび/またはライトするときに双安定回路12に供給される電圧V3(第1電源電圧)より低くSTモードの双安定回路12がデータを保持できる電圧である。

#### [0227]

このように、<u>保持しなくてもよいデータを記憶する</u>メモリセルをシャットダウンするため、<u>保持しなくてもよいデータを記憶する</u>メモリセルのモードの切り替えおよびリテンション状態を維持するための消費電力を抑制できる。また、レイテンシを削減できる。

#### [0228]

図22および図23のように、セルアレイ20は各々のブロック24が少なくとも2つのメモリセル10を含む複数のブロック24に分割されている。図25、図28および図31のステップS56のように、制御回路28は、複数のブロック24から保持しなくてもよいデータを記憶する1または複数の第1ブロックを抽出する。ステップS58のように、制御回路28は、第1ブロックをシャットダウン(電源遮断)する。その後、ステップS62およびS72のように制御回路28は、複数のブロック24のうち残りの1または複数の第2ブロック内の双安定回路をSTモードとする。ステップS68およびS74のように制御回路28はSTモードを維持した状態で第2ブロック内の双安定回路12に電圧V1を供給する。

# [0229]

このように、ブロック単位で、UDFがセットされた第1ブロックをシャットダウンするため、第1ブロックのモードの切り替えおよびリテンション状態を維持するための消費電力を抑制できる。また、レイテンシを削減できる。また、UDFがセットされた第1ブロックを最初にシャットダウンするため、モード切り替え動作を待機するときのリーク電流に起因する消費電力を削減できる。

#### [0230]

リテンション動作のタイプBおよびCのように、制御回路28は、リテンション対象のプロックをSTモードとする前に、図28および図31のステップS70のように、リテンション対象の第2プロックに電源電圧として電圧V2(第3電源電圧)を供給する(すなわちスリープ状態とする)。電圧V2は、電圧V3より低くかつ電圧V1より高くBIモードの双安定回路12がデータを保持できる電源電圧である。これにより、シャットダウンおよびリテンションを待機する期間の消費電力を抑制できる。

#### [0231]

ステップS72のように、制御回路28は、第2ブロック内の双安定回路12に電圧V2を供給した状態で第2ブロック内の双安定回路12をSTモードとする。これにより、リテンションを待機する期間の消費電力を抑制できる。

#### [0232]

リテンション動作のタイプ C の図 3 8 のように、制御回路 2 8 は、複数の第 2 ブロック内のうちのブロック 2 4 1 (第 3 ブロック)の双安定回路に電圧 V 2 を供給した状態でブ

20

30

40

50

ロック241内の双安定回路12をSTモードとし(図31のステップS72、期間T2)、ブロック241内の双安定回路12をSTモードとした状態で電圧V1を供給する(ステップS74、期間T3)。その後、制御回路28は、複数の第2ブロック内のうちのブロック241とは別のブロック242(第4ブロック)の双安定回路12に電圧V1を供給した状態でブロック242内の双安定回路12をSTモードとし、ブロック242内の双安定回路12をSTモードとした状態で電圧V1を供給する。これにより、リテンションを待機する期間を短くでき、消費電力を抑制できる。

### [0233]

リテンション動作のタイプBの図36のように、制御回路28は、第2ブロック内の双安定回路12に電圧V2を供給した状態で第2ブロック内の双安定回路12をSTモードとした後、第2ブロック内の双安定回路12をSTモードとした状態で電圧V1を供給する(図28のステップS74、図36の時刻t26)。これにより、タイプCに比べ制御を簡単にできる。制御回路28は、複数の第2ブロック内の双安定回路12をSTモードとした状態で電圧V2を一括して供給してもよい。また、制御回路28は、複数の第2ブロックを各々1または複数の第2ブロックを含む複数のグループに分割し、分割されたグループ毎に電圧V2を順次供給してもよい。

#### [0234]

レジスタ40(記憶回路)は、セルアレイ20の外に設けられ、外部回路から受信した UDF(<u>保持しなくてもよいデータを記憶する</u>ブロックを示す情報)を記憶する。制御回 路28は、UDFに基づき、<u>保持しなくてもよいデータを記憶する</u>ブロックを抽出する( ステップS56)。これにより、UDFを記憶する記憶回路を各サブアレイ22またはブ ロック24に設ける方法に比べ、UDFをバス25等を介し制御回路28に転送しなくて もよく、制御が簡単になる。

#### [0235]

図17のように、インバータ回路14および16は、FETm1およびm3(第1FET)、FETm2bおよびm4b(第2FET)、FETm2aおよびm4a(第3FET)並びにFETm9およびm10(第4FET)を備えている。FETm1およびm3は、Pチャネル(第1導電型のチャネル)FETであり、ソースが電源線15a(第1電源線)に接続され、ドレインが出力ノードQおよびQBに接続され、ゲートが入力ノードN1およびN3に接続されている。FETm2bおよびm4bは、Nチャネル(第1導電型の反対の第2導電型のチャネル)FETであり、ソースがグランド線15b(第2電源線)に接続され、ドレインが中間ノードN2およびN4に接続され、ゲートが入力ノードN1およびN3に接続されている。FETm2aおよびm4aは、NチャネルFETであり、ソースが中間ノードN2およびN4に接続されている。FETm9およびRL(制力ノードN2およびN4に接続されている。FETm9およびm10(第4FET)は、NチャネルFETであり、ソースおよびドレインの一方が中間ノードN2およびN4に接続されている。これによりの(第4FET)は、ドナスおよびドレインの他方が制御線CTRL(制御線CTRLの電圧によりBIモードとSTモードを切り替えることができる。

## [0236]

図 2 1 ( a ) のように、第 1 F E T は F E T m 2 および m 4 であり、第 2 F E T は F E T m 1 a および m 3 a であり、第 3 F E T は F E T m 1 b および m 3 b であり、第 4 F E T は F E T m 9 a および m 1 0 a でもよい。このとき第 1 導電型のチャネルは N チャネル、第 2 導電型のチャネルは P チャネルである。

# [0237]

図 2 1 ( b ) のように、第 1 F E T は電源線 1 5 a と出力ノード Q および Q B との間の 直列に接続された F E T m 1 a および m 1 b と m 3 a および m 3 b を設けてもよい。

#### 【実施例3】

# [0238]

実施例2の図17、図21(a)および図21(b)のメモリセル10では、プルダウ

20

30

40

50

ン側のフィードバックトランジスタFBT r であるFETm 9 および m 1 0 は N チャネル FETである。プルアップ側のフィードバックトランジスタFBT r であるFETm 9 a および m 1 0 a は P チャネルFETである。

#### [0239]

FETm9およびm10を設けたタイプをプルダウン型フィードバックPDFBと呼ぶ。FETm9aおよびm10aを設けたタイプをプルアップ型フィードバックPUFBと呼ぶ。FETm9a km10aを設けたタイプをプルアッププルダウン型フィードバックPUPDFBと呼ぶ。電源線15aと電源15cとの間にパワースイッチ30を設けたタイプをヘッダPSと呼ぶ。グランド線15bとグランド15dとの間にパワースイッチ30を設けたタイプをフッタPSと呼ぶ。図17のメモリセルはヘッダPS・PDFBである。図21(a)のメモリセルはヘッダPS・PUFBである。図21(b)のメモリセルはヘッダPS・PUFBである。

## [0240]

以下、ヘッダPS・PDFBを例に実施例2の課題を説明する。図17において、スタンバイ状態およびリテンション状態のVVDDおよびCTRLの電圧は以下である。

スタンバイ状態(BIモード): VVDD = VVDDH、CTRLの電圧VFNLリテンション状態(STモード): VVDD = VVDDL、CTRLの電圧VFNH【0241】

各電圧は例えば以下の関係である。

V F N L < V F N H = V V D D L < V V D D H

VFNL < V V D D L < V F N H < V V D D H 、 または

V F N L < V F N H < V V D D L < V V D D H

V V D D L 、 V V D D H 、 V G N D 、 V F N L および V F N H は 例えばそれぞれ 0 . 2V 、 1 . 2 V 、 0 . 0 V 、 0 . 0 V および 0 . 2 V である。

#### [0242]

例えばノードQがハイレベルのとき、FETm9がオンし、ノードN2は電圧がVFNHである制御線CTRLから充電される。しかし、FETm9がNチャネルであり、FETm9の閾値電圧Vthは正のため、制御線CTRLから充電電位は、実質的にはVFNH・Vthとなる。これにより、FBTrであるFETm9のフィードバック効果が低下し、リテンション状態における双安定回路の動作安定性(例えばノイズマージン)が低下する場合がある。

### [0243]

## 「ヘッダPS・PDFB]

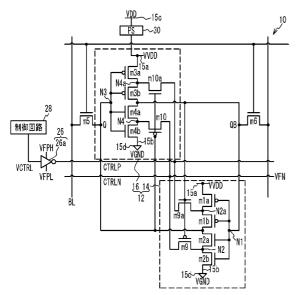

実施例 2 におけるメモリセルの上記課題を解決する実施例 3 について説明する。図 4 1 は、実施例 3 におけるヘッダ P S ・ P D F B ・ タイプ 1 のメモリセルの回路図、図 4 2 は、実施例 3 におけるヘッダ P S ・ P D F B ・ タイプ 2 のメモリセルの回路図である。 タイプ 1 はドライバ 2 6 を設けないタイプであり、タイプ 2 はドライバ 2 6 を設けるタイプである。図 4 1 および図 4 2 に示すように、F B T r である F E T m 9 および m 1 0 は P チャネル F E T である。 F E T m 9 および m 1 0 のゲートはそれぞれ ノード Q B および Q に接続されている。パワースイッチ 3 0 は電源線 1 5 a に仮想電源電圧 V V D D を印加する

### [0244]

図41のタイプ1では、ドライバ26が設けられておらず、制御線CTRLには定電圧VFNが印加されている。図42のタイプ2では、ドライバ26が設けられている。ドライバ26はインバータ26aであり、制御信号VCTRLがハイレベルのとき、制御線CTRLに電圧VFNLを供給し、制御信号VCTRLがローレベルのとき、制御線CTRLに電圧VFNHを供給する。その他の構成は実施例2の図17と同じであり説明を省略する。

# [0245]

図41に示すヘッダPS・PDFB・タイプ1におけるスタンバイ状態およびリテンシ

ョン状態のVVDDおよびCTRLの電圧は以下である。

スタンバイ状態(BIモード): VVDD = VVDDH、CTRLの電圧VFNリテンション状態(STモード): VVDD = VVDDL、CTRLの電圧VFN

#### [0246]

各電圧は例えば以下の関係である。

V F N = V V D D L < V V D D H

V V D D L < V F N < V V D D H 、 または

VFN < V V D D L < V V D D H (この関係ではノードN 3 およびN 4 が制御線C T R L から充電しにくいため好ましくない)

VVDDL、VVDDH、VGNDおよびVFNは例えばそれぞれ0.2V、1.2V、0.0Vおよび0.2Vである。

# [0247]

図42に示すヘッダPS・PDFB・タイプ2におけるスタンバイ状態およびリテンション状態のVVDDおよびCTRLの電圧は図17で例示した電圧と同じである。

#### [0248]

図41および図42の実施例3のメモリセルでは、例えばノードQがハイレベルのとき、ノードQBがローレベルとなるためFETm9がオンし、ノードN2は電圧がVFN(図41)またはVFNH(図42)である制御線CTRLから充電される。FETm9がPチャネル<u>FET</u>であり、FETm9のゲートにはソースおよびドレインに対し十分低い電圧が加わるため、ノードN2<u>の電圧</u>をVFN(図41)またはVFNH(図42)にプルアップできる。これにより、FETm9のフィードバック効果が十分に生じる。よって、リテンション状態における双安定回路の動作安定性を向上させることができる。

# [0249]

図41に示すタイプ1では、VVDDHに対しVFNを十分小さくすることで、VFNを定電圧としてもSTモードとBIモードの切り替えが可能となる。例えばノードQがハイレベルのとき、FETm9がオンしてもノードN2の電圧はVVDDHに対し十分低い。このため、双安定回路12はBIモードとして機能する。これにより、図17における制御線CTRL用のドライバ26が不要となり、チップ面積を削減できる。さらに、VFNをVVDDHより十分低くすることで、スタンバイ状態およびリテンション状態におけるリーク電流を抑制できる。

# [0250]

タイプ1では、VVDDHがVFNに近い場合には、BIモードへの遷移が不十分となる場合がある。図42に示すように、タイプ2では、STモードのときCTRLの電圧をVFNHとし、BIモードのときCTRLの電圧をVFNLとする。これにより、十分なBIモードに遷移可能である。

## [0251]

#### 「シミュレーション 1

6 T - S R A M のメモリセル(比較例 3 )、図 1 7 に示す実施例 2 のメモリセル、図 4 1 に示す実施例 3 のヘッダ P S ・ P D F B ・ タイプ 1 のメモリセルおよび図 4 2 に示す実施例 3 のヘッダ P S ・ P D F B ・ タイプ 2 のメモリセルについてシミュレーションを行った。

### [0252]

各FETのチャネル幅W/長さLは以下である。

FETm1、m3:100nm/60nm

FETm2a, m2b, m4a, m4b: 150nm/60nm

FETm5、m6:100nm/120nm

FETm9、m10:150nm/60nm

PS1:300nm/60nm

PS3:150nm/60nm

インバータ26aのFET:100nm/60nm

30

10

20

50

各電圧は以下である。

V V D D H = 1 . 2 V

V V D D L = 0 . 2 V

V G N D = 0 V

V F N H = 0 . 2 V

V F N L = 0 V

V F N = 0 . 2 V

#### [0253]

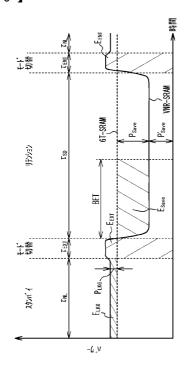

図43(a)は、リテンション状態におけるインバータ回路の伝達特性を示す図である。比較例3は6T-SRAMの通常の状態の特性を示す。図43(a)に示すように、実施例2では比較例3に比べ、バタフライ特性の開口が大きくなりノイズマージンが大きくなる。実施例3のタイプ1および2では実施例2よりノイズマージンが大きくなる。

#### [0254]

図 4 3 ( b ) は、スタンバイ状態における S N M ( Static Noise Margin ) を示す図である。 V V D D = 1 . 2 V であり、 B I モードである。リテンションは、 U L V リテンション状態ではなく、 F E T m 5 および m 6 をオフし、データを保持している状態を示す。リードは、 F E T m 5 および m 6 をオンし、ビット線 B L および B L B を 1 . 2 V とした状態を示す。 ライトは F E T m 5 および m 6 をオンし、ビット線 B L および B L B の一方を 1 . 2 V とし他方を 0 V とした状態を示す。

### [0255]

図43(b)に示すように、実施例3では比較例3および実施例2に比べSNMがやや大きい。これは、実施例3では、FETm9およびm10がPチャネル<u>FET</u>のため、ノードN3およびN4の電位が実施例2より少し高くなる。このため、BIモードにおいてFETm9およびm10によるフィードバックが少しかかる。これにより、SNMが少し増加するためである。

## [0256]

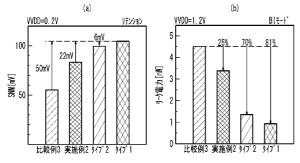

図44(a)は、リテンション状態のSNMを示す図である。図44(a)に示すように、比較例3ではSNMは約50mVであるのに対し、実施例2ではSNMを約80mVと大きくできる。実施例3ではSNMは約100mVであり、実施例2よりSNMを約20mV、比較例3よりSNMを約50mV大きくできる。実施例3のタイプ1とタイプ2ではSNMはほぼ同程度である。実施例3では、比較例2よりSNMをほぼ2倍にできる。このように、実施例3では実施例2よりリテンション状態のSNMを大きくでき、動作安定性が向上する。実施例2の同程度のSNM(例えば80mV)を確保する場合、実施例2よりVVDDLを低くできる。これにより消費電力を抑制できる。

### [0257]

実施例 3 のタイプ 1 はタイプ 2 より 5 N M が約 6 m V 大きい。これは、タイプ 1 ではドライバ 2 6 が設けられていないため、制御線 C T R L に効果的にバイアスが加わるためである。図示していないが、後述する P U P D F B では、 P U F B および P D F B よりノイズマージンを拡大することができる。

## [0258]

図44(b)は、BIモードのリーク電力を示す図である。図44(b)に示すように、実施例2のスタンバイ状態(BIモード)では、比較例3に比ベリーク電力を25%削減できる。実施例3では比較例3に比べ、タイプ2で70%、タイプ1で81%リーク電力を削減できる。このように、実施例3では、実施例2よりスタンバイ状態におけるリーク電力を抑制できる。

#### [0259]

図44(c)および図44(d)は、STモードのリーク電力を示す図である。図44 (c)の比較例3は6T-SRAMのスタンバイ状態のリーク電力である。図44(c) に示すように、実施例2のリテンション状態(STモード)では比較例3のスタンバイ状態に比べリーク電力を92%削減できる。実施例3のタイプ1および2では比較例3に比 10

20

30

40

べそれぞれ95%および94%リーク電力を削減できる。図44(d)に示すように、実施例3のタイプ1および2では、実施例2に比べリーク電力をそれぞれ40%および20%削減できる。

[0260]

以下、ヘッダPS・PDFB以外の例について説明する。

[フッタPS・PDFB]

図 4 5 は、実施例 3 におけるフッタ P S ・ P D F B ・ タイプ 2 のメモリセルの回路図である。図 4 5 に示すように、電源線 1 5 a には V D D が供給され、グランド線 1 5 b とグランドとの間にパワースイッチ 3 0 が設けられている。グランド線 1 5 b は仮想グランド電圧 V V G N D である。

[0261]

スタンバイ状態およびリテンション状態のVVGNDおよびCTRLの電圧は以下である。

スタンバイ状態(BIモード): VVGND=VVGNDL、CTRLの電圧VFNLリテンション状態(STモード): VVGND=VVGNDH、CTRLの電圧VFNH 各電圧は例えば以下の関係である。

V V G N D L < V V G N D H

VFNL~VVGNDL、および

V F N H ~ V V G N D H

なお、~は近傍を示す。

V V G N D L 、 V V G N D H 、 V D D 、 V F N L および V F N H は 例えばそれぞれ 0 . 0 V 、 1 . 0 V 、 1 . 2 V 、 0 . 0 V および 1 . 2 V である。

[0262]

[PDFB]

PDFBでは、図41のように、ヘッダPSとする場合、VVDDH-VGNDが大きいとき、例えば0.5 V以上であり、例えばVFN-VGND</br>

) / 2 のとき、タイプ1とすることができる。VVDDH-VGNDが小さいとき、例えば0.5 V以下のとき、タイプ1では、BIモードへの遷移が不十分な場合がある。よって、タイプ2とすることで、十分なBIモードに遷移することができる。フッタ<u>PS</u>・PDFBでは、図45のようにタイプ2となる。

[0263]

[ J y P P S · P U F B ]

図46は、実施例3におけるフッタPS・PUFB・タイプ1のメモリセルの回路図である。FETm9aおよびm10aはNチャネルFETである。FETm9aおよびm10aのゲートは、それぞれノードQBおよびQに接続されている。電源線15aにはVDDが供給され、グランド線15bとグランド15dとの間にパワースイッチ30が設けられている。グランド線15bは仮想グランド電圧VVGNDである。制御線CTRLには定電圧VFPが印加される。その他の構成は、実施例2の図21(a)と同じであり、説明を省略する。

[0264]

スタンバイ状態およびリテンション状態のVVGNDおよびCTRLの電圧は以下である。

スタンバイ状態(BIモード): VVGND=VVGNDL、CTRLの電圧VFPリテンション状態(STモード): VVGND=VVGNDH、CTRLの電圧VFP各電圧は例えば以下の関係である。

VVGNDL < VFP = VVGNDH

VVGNDL < VFP < VVGNDH、または

VVGNDL < VVGNDH < VFP (この関係ではノードN2 a およびN4 a が制御線CTRLから放電しにくいため好ましくない)

VVGNDL、VVGNDH、VDD、VFPは例えばそれぞれ0.0V、1.0V、

10

20

30

40

1 . 2 V および 1 . 0 V である。

### [0265]

「ヘッダPS・PUFB]

図47は、実施例3におけるヘッダPS・PUFB・タイプ2のメモリセルの回路図である。図46に対し、ドライバ26が設けられている。ドライバ26は、インバータ26aであり、制御回路28が出力する制御信号VCTRLがローレベルのとき制御線CTRLに電圧VFPHを出力し、VCTRLがハイレベルのとき制御線CTRLに電圧VFPLを出力する。

#### [0266]

スタンバイ状態およびリテンション状態のVVDDおよびCTRLの電圧は以下である

10

20

スタンバイ状態(BIモード): VVDD=VVDDH、CTRLの電圧VFPH リテンション状態(STモード): VVDD=VVDDL、CTRLの電圧VFPL 各電圧は例えば以下の関係である。

VVDDL < VVDDH

VFPL~VGND、および

VFPH~VVDDH

なお、~は近傍を示す。

V V D D L 、 V V D D H 、 V G N D 、 V F N L および V F N H は 例えばそれぞれ 0 . 2 V 、 1 . 2 V 、 0 . 0 V 、 0 . 0 V および 1 . 2 V である。

[0267]

[PUFB]

PUFBでは、図46のように、フッタPSとする場合、VDD-VVGNDLが大きいとき、例えば0.5 V以上であり、例えばVDD-VFP<(VDD-VVGNDL) / 2 のとき、タイプ 1 とすることができる。VDD-VVGNDLが小さいとき、例えば 0.5 V以下のとき、タイプ 1 では、B I モードへの遷移が不十分な場合がある。よって、タイプ 2 とすることで、十分な B I モードに遷移することができる。ヘッダ PS・P U F B では、図47のようにタイプ 2 となる。

[0268]

[ ヘッダ P S ・ P U P D F B ]

30

40

50

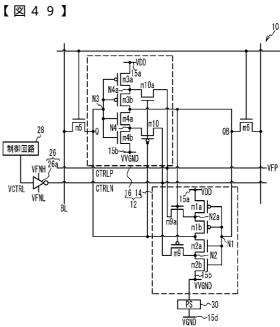

図48は、実施例3におけるヘッダPS・PUPDFBのメモリセルの回路図である。FETm9およびm10はPチャネルFETであり、FETm9aおよびm10aはNチャネルFETである。FETm9およびm9aのゲートは、ノードQBに接続され、FETm10およびm10aのゲートは、ノードQに接続されている。電源線15aと電源15cとの間にパワースイッチ30が設けられ、グランド線15bにグランド電圧VGNDが供給される。FETm9およびm10の制御線CTRLNには定電圧VFNが供給される。FETm9aおよびm10aの制御線CTRLPにはドライバ26から電圧印加される。ドライバ26は、インバータ26aであり、制御回路28が出力する制御信号VCTRLがローレベルのとき制御線CTRLPに電圧VFPHを出力し、VCTRLがハイレベルのとき制御線CTRLPに電圧VFPHを出力し、VCTRLがハイレベルのとき制御線CTRLPに電圧VFPLを出力する。その他の構成は、実施例2の図21(b)と同じであり、説明を省略する。

[0269]

図48に示すヘッダPS・PUPDFBのメモリセルの動作条件は、図41に示すヘッダPS・PDFB・タイプ1のメモリセルの動作条件と、図47に示すヘッダPS・PUFB・タイプ2のメモリセルの動作条件を合わせたものである。

[0270]

[ フッタPS・PUPDFB ]

図49は、実施例3におけるフッタPS・PUPDFBのメモリセルの回路図である。 電源線15aに電源電圧VDDが供給され、グランド線15bとグランド15dとの間に パワースイッチ30が設けられている。FETm9aおよびm10aの制御線CTRLP

20

30

40

50

には定電圧VFPが供給される。FETm9およびm10の制御線CTRLNにはドライバ26から電圧印加される。ドライバ26は、インバータ26aであり、制御回路28が出力する制御信号VCTRLがローレベルのとき制御線CTRLNに電圧VFNHを出力し、VCTRLがハイレベルのとき制御線CTRLNに電圧VFNLを出力する。その他の構成は、図48と同じであり、説明を省略する。

#### [0271]

図49に示すフッタPS<u>・</u>PUPDFBのメモリセルの動作条件は、図45に示すフッタPS・PDFB・タイプ2のメモリセルの動作条件と、図46に示すフッタPS・PUFB・タイプ1のメモリセルの動作条件を合わせたものである。

# [0272]

ヘッダPSでは、スタンバイ状態のVVDDを通常動作状態のVVDDHよりやや低い VVDDHSとしてもよい。フッタPSでは、スタンバイ状態のVVGNDを通常動作状態のVVGNDLよりやや高いVVGNDLSとしてもよい。低電圧動作させるため、ヘッダPSでは、VVDDL<VVDDM<VVDDHとなるVVDDM、フッタPSでは、VVGNDL<VVGNDMを用いてもよい。

#### [0273]

実施例3によれば、PDFBの場合、インバータ回路14(第1インバータ回路)および16(第2インバータ回路)の各々において、PチャネルFETm1およびm3(第1導電型のチャネルの第1FET)では、ソースが電源線15a(第1電源線)に接続され、ドレインがノードQおよびQB(出力ノード)に接続され、ゲートがノードN1およびN3(入力ノード)に接続される。NチャネルFETm2bおよびm4b(第2導電型のチャネルの第2FET)では、ソースが電源線15aとの間に電源電圧VVDD-VGNDが供給されるグランド線15b(第2電源線)に接続され、ドレインがノードN2およびN4(中間ノード)に接続され、ゲートがノードN1およびN3に接続される。NチャネルFETm2aおよびm4a(第2導電型のチャネルの第3FET)では、ソースがノードN2およびN4に接続され、ドレインがノードQおよびQBに接続され、ゲートがノードN1およびN3に接続される。

## [0274]

PチャネルFETm9およびm10(第1導電型のチャネルの第4FET)では、ソースおよびドレインの一方がノードN2およびN4に接続され、ソースおよびドレインの他方が制御線CTRL(制御ノード)に接続され、ゲートがノードN1およびN3に接続される。インバータ回路14の出力ノードおよびインバータ回路16の入力ノードN3はノードQ(第1記憶ノード)に接続され、インバータ回路14の入力ノードN1およびインバータ回路16の出力ノードはノードQB(第2記憶ノード)に接続されている。これにより、電源電圧VVDD-VGNDおよび制御線CTRLの電圧を適宜設定することにより、STモードにおける動作安定性を向上できる。

#### [0275]

インバータ回路 1 4 の F E T m 9 のゲートはインバータ回路 1 6 の出力ノードに接続され、インバータ回路 1 6 の F E T m 1 0 のゲートはインバータ回路 1 4 の出力ノードに接続されていてもよい。

#### [0276]

PUFBの場合、NチャネルFETm2およびm4が第1FETに対応し、PチャネルFETm1aおよびm3aが第2FETに対応し、PチャネルFETm1bおよびm3bが第3FETに対応し、NチャネルFETm9aおよびm10aが第4FETに対応する。グランド線15bおよび電源線15aがそれぞれ第1電源線および第2電源線に対応する。

# [0277]

PDFBの場合、パワースイッチ30(電源回路)は、電源電圧VVDD-VGNDとして、電圧VVDDH-VGND(第1電圧)と電圧VVDDH-VGNDより低く電圧VVDDL-VGND(第2電圧)と、に切り替えて供給する。電圧VVDDH-VGN

20

30

40

50

Dは、双安定回路12がデータをライトおよびリード可能な電圧であり、電圧VVDDL-VGNDは電圧VVDDH-VGNDより低く双安定回路12がデータをライトおよびリードができずデータを保持可能な電圧である。これにより、データを保持するときに、消費電力を抑制できる。

## [0278]

電源回路は、1つの電源からパワースイッチのようなトランジスタを用い第1電圧と第2電圧とを生成し、双安定回路に供給してもよい。また、制御回路は、2つの電源にそれぞれパワースイッチが接続され、パワースイッチを制御することで第1電圧と第2電圧を双安定回路に供給してもよい。

## [0279]

PUFBの場合、電圧VDD - VVGNDLおよびVDD - VVGNDHがそれぞれ第1電圧および第2電圧に対応する。

#### [0280]

タイプ1のように、パワースイッチ30が双安定回路12に第1電圧および第2電圧のいずれを供給するときにも、制御線CTRLには定バイアス(PDFBの場合VFN、PUFBの場合VFP)が供給される。これにより、ドライバ26が不要となり、チップサイズを削減できる。

#### [0281]