Progress Report

Research and Development of Theory and Software for Fault-tolerant Quantum Computers[4] Research and development of distributed fault-tolerant quantum computers

Progress until FY2024

1. Outline of the project

This project aims to explore the possibility of distributed architecture of fault-tolerant quantum computers. In particular, the goal is to open up possibilities of quantum computation with physical systems that cannot be scaled up without having a distributed structure and of further scaling up by connecting quantum computers that are developed in a monolithic form. Our research will present new guidelines for the design of a fault-tolerant quantum computer to be developed in 2050, i.e., the goal of the Moonshot Goal 6.

Toward the goal, we consider design of a basic module to connect distant qubits with quantum communication and functionally distributed design, as well as the exploration of quantum error-correcting codes and fault-tolerant quantum computing schemes which fit distributed architecture.

2. Outcome so far

1) Optimal supplier of entanglement via coherent-state transmission [Azuma et al., PRA 105, 062432 (2022)]

The basis of distributed quantum computation is to apply a high-fidelity controlled-not gate to distant qubits, which is achieved by supplying them with high-fidelity entanglement. Here we derive an upper bound on achievable rates of protocols that supply single-error type entanglement via coherent-state transmission over lossy channels. This bound coincides with the performance of an existing protocol based on a remote nondestructive parity measurement. The use of such an efficient entanglement generation does not necessitate entanglement distillation, in contrast to what is required in existing proposals.

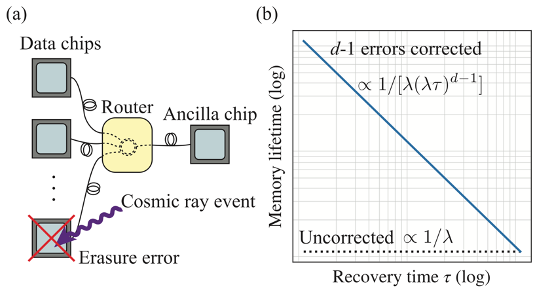

2) Distributed quantum error correction for chip-level catastrophic [Xu et al., PRL 129, 240502 (2022)]

Cosmic ray events could cause chip-level catastrophic errors in a quantum computer. We propose implementing quantum error correction across separate chips in a distributed setup. Even if arbitrary data in a chip are destroyed, by connecting data and ancilla chips, the data as a whole can be retrieved with an erasure quantum error correcting code. Our scheme can suppress the rate of such catastrophic errors from 1 per 10 s to less than 1 per month.

(b) Recovery time vs memory lifetime

3) Load-store architecture for fault-tolerant quantum computing [Kobori et al., HPCA pp.304-320, (2025)]

In conventional quantum computers, all quantum data are typically stored in registers with computational capabilities. While this design is simple, it suffers from limited scalability. In this work, we address this issue by distributing the functions of a quantum computer into a processor, which performs computation, and memory, which stores data. Our design reduces the number of required qubits by 40%. Although transferring data between the processor and memory introduces overhead, the execution time penalty can be limited to around 3% by leveraging data-access locality through a cache-like structure.

3. Future plans

We would develop a blueprint of a distributed fault-tolerant quantum computer, by building found basic modules into distributed architecture of quantum computing.