- JST トップ

- /

- 戦略的創造研究推進事業

- /

ACCEL

ACCEL- /

- 研究開発課題/

- 終了課題/

- 縦型BC-MOSFET による三次元集積工学と応用展開

縦型BC-MOSFET による三次元集積工学と応用展開

研究開発課題の概要

|

|

| パンフレットPDF |

研究紹介動画 (約1分30秒) |

研究代表者

遠藤 哲郎

(東北大学 国際集積エレクトロニクス研究開発センター センター長、大学院工学研究科 教授)

1987年 東京大学理学部物理学科卒業

1987年 株式会社東芝入社

1995年 工学博士取得

1995年 東北大学電気通信研究所 講師

1997年 東北大学電気通信研究所 助教授 (2007年准教授)

2008年 東北大学電気通信研究所 教授

2008年 東北大学学際科学国際高等研究センター 教授

2012年~現在 東北大学大学院工学研究科 教授

2009年~現在 東北大学省エネルギー・スピントロニクス集積化システムセンター 副センター長・教授

2012年~現在 東北大学国際集積エレクトロニクス研究開発センター センター長・教授

研究室ホームページhttp://www.ecei.tohoku.ac.jp/endohlab/

http://www.cies.tohoku.ac.jp/

プログラムマネージャー

政岡 徹

(科学技術振興機構 ACCELプログラムマネージャー)

1974年 慶應義塾大学大学院工学研究科 修士課程 修了

1974年 株式会社東芝 入社

2001年 岩手東芝エレクトロニクス株式会社 取締役社長

2003年 株式会社東芝 システムLSI事業部 事業部長

2006年 東芝セラミックス株式会社 代表取締役専務

2011年 コバレントシリコン(現グローバルウェーハズ・ジャパン)株式会社 代表取締役社長

2015年 グローバルウェーハズ・ジャパン株式会社 顧問

2015年 ACCELプログラムマネージャー

研究開発期間

2014年4月~2019年3月

研究開発概要

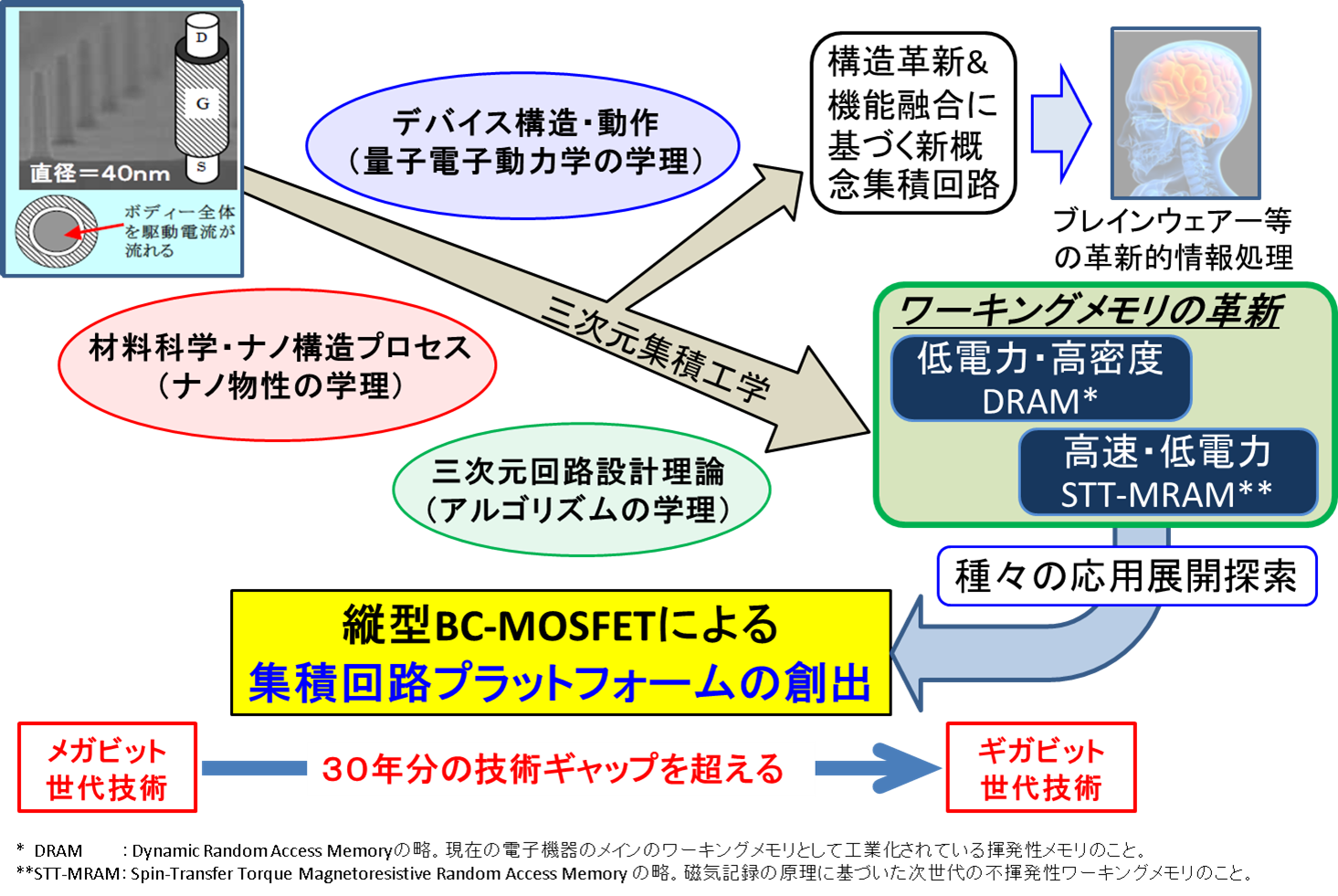

CRESTでの基礎研究の成果である縦型ボディチャネル(BC-)MOSFET注1)(以下、縦型トランジスター)は、トランジスターを縦型構造にすることで、チップサイズの縮小、リーク電流の低減、放熱性の向上など、既存のトランジスター技術に対する優位性を持つことが示されており、1メガビットメモリーとして動作することも実証されています。

ACCELでは、縦型トランジスターが持つ特徴を最大限生かし、ワーキングメモリー注2)を中心にさまざまな集積回路への応用に向けた研究開発を行います。

具体的には、以下の研究開発を推進します。

1)縦型トランジスターの優位性を生かし、大容量、高速、低消費電力のワーキングメモリーの実現を目指します。

2)縦型トランジスターがワーキングメモリーのみならずロジックLSIやアナログLSIなどさまざまな応用展開にもつながるよう、基盤となる共通技術を戦略的に構築していくことを目指します。

以上を推進することで、半導体集積回路の新しい技術プラットフォームを創出し、革新的省電力集積回路を先導することにより、情報化社会・省エネルギー社会・ユビキタス社会への貢献を目指します。

注1)MOSFET

Metal―Oxide―Semiconductor Field Effect Transistorの略。電圧を加えることで電流の流れを制御するスイッチング素子のこと。

注2)ワーキングメモリー

コンピューターが処理するデータを一時的に保存するための記憶装置のこと。

<目指すビジョンの図>