事業成果

スピントロニクス省電力半導体技術の展開

低消費電力かつ高速動作の縦型BC-MOSFETの量産化へ2025年度更新

- 遠藤 哲郎(東北大学 国際集積エレクトロニクス研究開発センター センター長)

- CREST

- 「次世代エレクトロニクスデバイスの創出に資する革新材料・プロセス研究」領域・「縦型ボディーチャネルMOSFETとその集積プロセスの開発」研究代表者(2008-2013)

- ACCEL

- 「縦型BC-MOSFETによる三次元集積工学と応用展開」研究代表者(2014-2018)

縦型BCトランジスタ+MRAMで飛躍的な低消費電力と高速動作を実現

東北大学国際集積エレクトロニクス研究開発センターの遠藤哲郎センター長らの研究グループは、現在3nm以降のCMOS世代で活発に開発されているGAA型MOSFETの源流にあたる低消費電力・低ノイズの革新的トランジスタ「縦型BC(ボディーチャネル)-MOSFET※1」を世界で初めて開発している。この縦型BC-MOSFETをメモリーセルの周辺回路に配した1ギガビット(ギガ:10億)級の大規模DRAM※2を大口径300mmウエハーにて試作し、従来のDRAMに比べて大幅に低電圧化した条件下でも良好に動作することを実証している。この縦型BC-MOSFET(縦型GAA-MOSFET)は、半導体技術に関する国際デバイスシステムロードマップ(IRDS)にも3nm以降の標準技術として記載されている。

さらに、研究グループは、縦型BC-MOSFETをスピントロニクス半導体である磁気記録式メモリー(MRAM)に適用するための基盤技術に取り組み、128メガビット(メガ:100万)のSTT-MRAM※3を試作して世界最高性能の書き込み速度の実証にも成功している。

このような成果を社会実装していくために、2018年に東北大学発のスタートアップであるパワースピン株式会社が設立された。パワースピン社の代表取締役&COO(最高執行責任者)を兼ねる遠藤センター長は、半導体メーカーとの連携により、STT-MRAMをはじめスピントロニクス省電力半導体※4の実用化・量産化に向けた研究開発を進めている。2018年には、台湾の世界的な半導体ファウンドリーである台湾セミコンダクター・マニュファクチャリング・カンパニー(TSMC)などから、MRAMの量産が開始されている。

※1 MOSFET

金属酸化膜半導体電界効果トランジスタ。集積回路の中で最も一般的な構造。

※2 DRAM

ダイナミック・ランダムアクセス・メモリー。情報を読み書きする記録デバイス。

※3 STT-MRAM

スピン注入型磁気抵抗型メモリー。磁化の方向で情報を記憶する不揮発性メモリー。高速磁化反転により高速動作が可能で、原子移動が無いために書き換え耐性も高い。

※4 スピントロニクス省電力半導体

スピントロニクスとは、スピンとエレクトロニクスの合成語。これまでの半導体は電荷の有無を「0」「1」の情報として扱うが、スピントロニクス半導体では電子の自転で生じる磁気(電子スピン)の向きの違いを利用して情報を扱う。従来の半導体は電源を切ると情報が消えてしまうが、磁気は電源を落としても失われないので大幅な低消費電力化が期待できる。

待機電力とリーク電力の削減が低電力化の決め手

スマートフォンやタブレット端末の高機能化にともない、バッテリー使用持続時間が短くなるのが大きな課題となってきた。

要因の1つが半導体デバイスの待機電力である。現行のCPU(中央演算処理装置)やDRAMなどは電源を切るとデータが失われるため、動作しないときも通電する待機電力が発生する。これを解消する手段として開発が進められているのがスピントロニクス半導体だ。スピントロニクス半導体は電子スピン(回転)により生じる磁気の向きで情報を記録する。磁気は電源を切っても保存されるので待機電力を必要とせず、理論的には消費電力が約100分の1になる。スピントロニクス半導体の研究は東北大学が世界をリードしており、すでに世界の半導体メーカーでMRAMが量産されている。

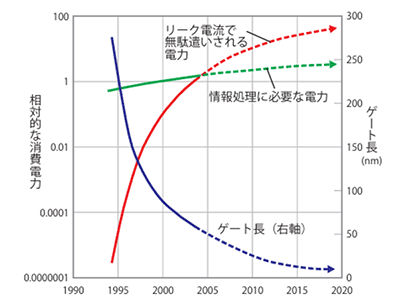

もうひとつの要因が集積回路の基本素子であるMOSFET自身のリーク電流である。半導体素子(トランジスタ)はゲートにて電流を流したり遮断したりして情報の出し入れをする。ナノサイズにまで素子の微細化が進むとゲート長も短くなることで外部に漏れる電流が無視できなくなり、消費電力に影響をもたらしていた(図1)。これを解消するために、遠藤センター長らが研究してきたのが「縦型BCトランジスタ」である。この縦型BC-MOSFET(縦型GAA-MOSFET)は、国際デバイスシステムロードマップ(IRDS)にも3nm以降の標準技術として記載されている。

図1 半導体集積回路におけるリーク電流

半導体集積回路ではゲート長の短縮に伴い、リーク電力が急増する。

(IEEE Computer,36(12):68-75,2003より作成(点線は当時の予測))

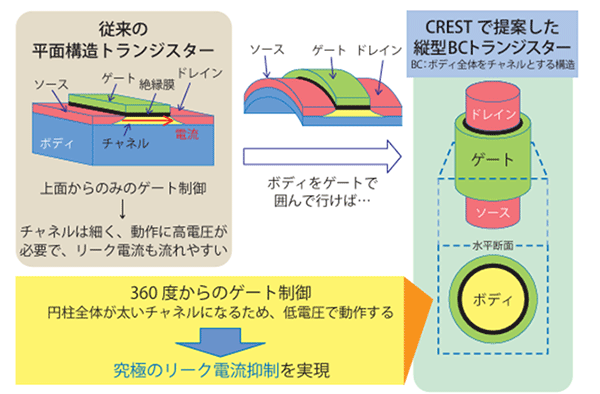

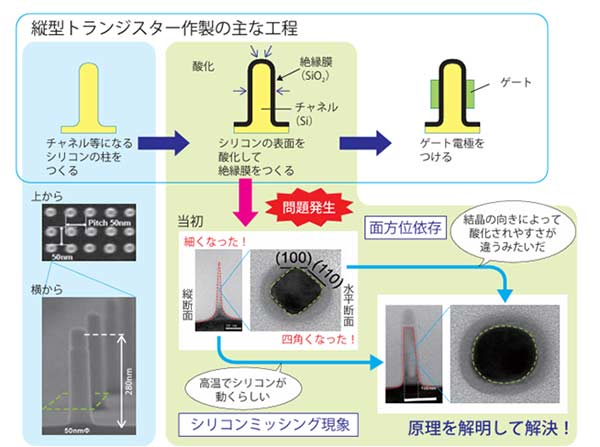

産学連携で縦型BC-MOSFETを活用したデバイスの開発を展開

遠藤センター長らの研究チームは、縦型BCトランジスタの基礎研究を進めてきた。従来のトランジスタがシリコンの土台に平面的に回路を形成するのに対し、縦型BCトランジスタは直径数十ナノメートルのシリコンの円柱にゲートを360度巻きつける構造のためゲート長を十分にとることで、リーク電流を大幅に減らすことができる(図2)。しかし、極細のシリコンの円柱に絶縁膜を形成するのが難しかった。5年間の研究でシリコンの結晶の方向(面方位)により酸化の程度が変わるために絶縁膜形成を妨げていたことをつきとめて、1メガビットの縦型BCメモリーを世界で初めて開発した(図3)。

この成果をもとに、2014年からは、縦型BCトランジスタ技術とスピントロニクス半導体技術との組み合わせにより、超低消費電力かつ高速動作を可能とする新規デバイスの開発に向けた研究開発を進めてきた。プロジェクトには大学だけでなく東京エレクトロン株式会社やマイクロンジャパン株式会社などの有力半導体関連企業が参画し、縦型BC-MOSFETの飛躍的な高集積化と省エネ性を実現する基盤技術とともに、ワーキングメモリー(DRAMやSTT-MRAMなど)を中心にロジックLSI、アナログLSI、AI・脳型LSI※5などの応用展開につながる共通基盤技術の開発を進めてきた。

この研究を通じて、縦型BC-MOSFETを周辺回路に搭載したギガビット級の大規模STT-MRAMを試作し、低電源電圧での動作実証に世界で初めて成功、高密度・高速のMRAMの実現に向けた集積化プロセス技術を確立した。また、ロジックLSIにおけるSRAMの大幅な面積縮小と待機電力削減にも成功している。

このような研究開発と併行して、2018年に東北大学発のスタートアップとなるパワースピン株式会社を設立し、国際集積エレクトロニクス研究開発センターを中核とした産学連携のもとで、縦型BC-MOSFETの実用化に向けて製造コスト、耐久性、信頼性などを含めた研究開発を進めている。

※5 AI・脳型LSI

脳の構造を模したニューロモーフィック技術を活用したAI半導体。

図2 縦型BCトランジスタの構造 トランジスタは、ゲート電圧により電気の通り道(チャネル)をつくり、ソースからドレインに電気を流すことで信号を伝える。ゲート長が短くなると、チャネルをつくらないときでもソースとドレイン間の電圧により「リーク電流」が通ってしまう。リークの元になるソースとドレイン間の電圧を下げることが縦型構造の狙いである。

図3 縦型トランジスタ作成の主な工程 ナノレベルの結晶をつくることで初めて明らかになったシリコンの円柱が痩せる「ミッシング現象」(中央)とその解決につながった「面方位依存」(右下)。

超高速なAI実現に貢献する光電融合半導体開発に参画

パワースピン社では、今回の研究成果を活用し、アイリスオーヤマ株式会社と共同で「非接触多人数対応検温カメラ」を開発した。従来の検温カメラの検出人数が5~10人/秒だったのに対し、40~170人/秒の高速検温を実現したもので、コロナ禍の中で開催された2023年5月の広島G7サミット(主要国首脳会議)の場でデモンストレーションされた。

また、東北大学国際集積エレクトロニクス研究開発センターは、次世代通信基盤(IOWN)の中核技術としてNTTなどが国際連携によって開発する「光電融合半導体プロジェクト」にも参画してメモリー制御技術の開発の一部を担うなど、超高速性が求められる将来のデバイス開発に貢献すべく研究開発を続けている。

- ナノテクノロジー・材料の成果一覧へ

- 事業成果Topへ

- English