事業成果

電気自動車や産業機器の省エネルギー化に貢献

SiCパワー半導体の大幅な性能改善2022年度更新

- 木本 恒暢(京都大学 大学院工学研究科 教授)

- 産学共創プラットフォーム共同研究推進プログラム(OPERA)

- 超スマート社会実現のカギを握る革新的半導体技術を基盤としたエネルギーイノベーションの創出(2018-2022)

界面の欠陥低減技術開発でSiCパワー半導体の大幅な性能改善

Si(シリコン)を中心とした半導体は、計算機や通信機のロジックやメモリに代表される情報処理用途に限らず、電気自動車や電車のモーター制御、変圧器や直流-交流変換器などいわゆる電力制御(パワーエレクトロニクス)にも広く用いられている。ただ後者の応用では、制御回路の消費電力(電力損失)が大きな問題となっており、低損失化を目指して、Siよりも基本特性の優れるSiC(シリコンカーバイド)によるトランジスタ開発が近年活発になっている。2020年7月にデビューした新幹線の最新モデルN700SにもSiCパワー半導体が用いられるなど、既に実用化が始まっている。

しかしながら、SiCトランジスタの心臓部となる酸化膜とSiCの境界部分(界面)には多くの欠陥が存在し、SiC本来の性能を発揮できない状況が過去20年以上続いていた。木本恒暢教授の研究グループは、2020年8月と9月に、物理的考察に基づく独自の手法により界面の欠陥を大幅に低減し、SiCトランジスタのチャネル移動度を2倍向上することを報告した。また2021年10月には、この研究をさらに発展させ、実用的に重要な構造において同特性を6~80倍向上させることに成功した。

今後カーボンニュートラルの世界を目指す中で、高まる再生可能エネルギーの高度活用、即ち電力エネルギーの高効率活用の要求に応えるべく、SiCパワー半導体の更なる高性能化が期待されている。

社会から求められる半導体パワーデバイスの進化

Si半導体において最も重要なトランジスタは、酸化膜と半導体の接合を利用したMOSFET(金属-酸化膜-半導体電界効果トランジスタ)である。Si-MOSFETは3端子のデバイスで、ゲート電極に与える電圧で、残る2つの電極(ドレイン(D)とソース(S))間の電気抵抗を変化させることができる。多くの応用では、この電気抵抗を通電状態と遮断状態の2つの状態で利用するスイッチとして利用し、情報処理ではonとoffの状態を1と0の2値に割り当てて演算を行い、パワーエレクトロニクスでは、ダイオードや他の部品と組み合わせて、電力を切り刻んで望む波形に変換してモーター等を駆動する。情報処理と異なり、パワーエレクトロニクスではエネルギー(電流)を制御する必要から、D-S間の通電時の電気抵抗(on抵抗)がそのまま損失になる。スイッチ(電流の通路[チャネル])は、酸化膜と隣り合う半導体界面に対応し、パワーエレクトロニクスの高効率化では「on抵抗を低く抑えること」、即ち半導体界面の結晶欠陥の低減が高性能化の鍵になっている。

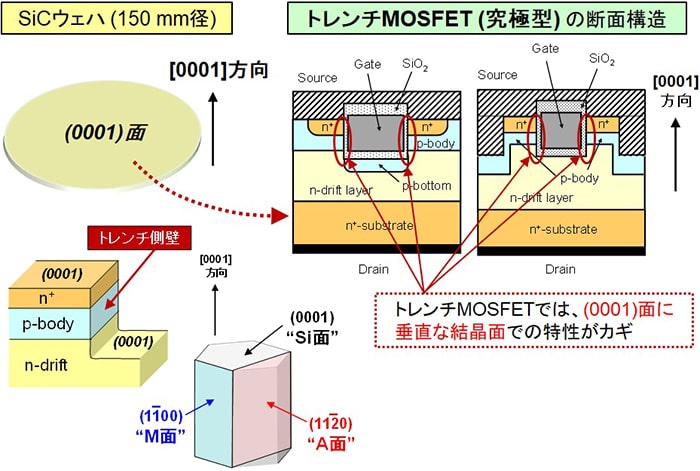

SiCはその基本的材料特性から、Siに比べてより高い電圧を取り扱うことが可能で高速にスイッチを開閉することができるが、制御回路のエネルギー損失に直接かかわる「on抵抗」は、チャネルを形成するSiC半導体の結晶面にも依存する。実用的には、「トレンチ(溝)型」と言われるMOSFETが最も有望であることがわかっており、このデバイス構造では、心臓部である酸化膜/SiC界面をSiCウェハ表面(「Si面」と呼ばれる)ではなく、ウェハ表面に直交する面(「A面」もしくは、「M面」)に形成する必要がある。即ち、ウェハ表面を垂直に掘りこんだ後に、その断面に酸化膜/SiC界面(チャネル)を作りこむことが求められ、この界面での結晶欠陥の低減を、より複雑なデバイス製造プロセスの中で実現していくことが、高機能化の第2の鍵となっている。

非酸化による酸化膜形成を考案(木本恒暢教授の研究グループの成果)

Si MOSFETでは、Siを熱酸化(酸素雰囲気で高温に加熱)することで、Siの表面に非常に良質の酸化膜(SiO2)が形成されるプロセスを活用する。この熱酸化膜は、Siと相性のよい電気的・機械的・熱的・化学的特性の優れた絶縁膜であり、今も発展的飛躍を続けている集積回路技術の基盤となっている。

Siと同様に、SiCも熱酸化すると表面にSiO2膜が形成される性質があるため、SiCの大きなメリットと認識され、これまで、この方法によりSiC-MOSFETが作製されていた。しかしながら、酸化膜/SiCの境界部分(界面)に極めて多くの欠陥(Siの場合の100倍以上)が存在し、この界面欠陥がSiCトランジスタの性能を大きく損ねていた。また長年にわたり、SiCの酸化条件の調整や、その後のさまざまな熱処理条件によって界面欠陥の低減を図ってきたものの顕著な成果がなく、この界面欠陥生成の起源も明らかにされてこなかった。

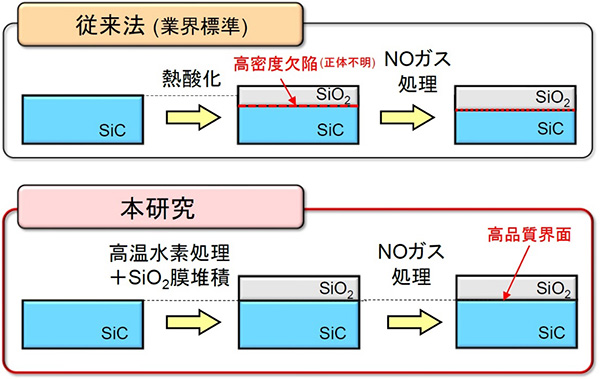

木本教授の研究グループは、「SiCを⼀層たりとも酸化させない手法で良質の酸化膜を形成する」という一見矛盾する目標を掲げて実験研究を行い、Si面での酸化膜界面形成手法として、以下の2点が欠陥低減に有効であることを見出し、従来の世界標準に比べて、界面欠陥を約5分の1に低減した(2020年9月発表時点)。

① SiCウェハ製造やトランジスタ製造の工程で必要なSiC表面の酸化過程で、SiC表面近傍に高密度の欠陥が導入されることに気づき、酸化膜を形成する前にこれを適切な方法(水素エッチング)で除去することが重要であることを見出した。

② ①により高品質なSiC表面を形成した後に、SiCの酸化により酸化膜(SiO2膜)を形成すると、新たに高密度の欠陥が発生することを確認した。この問題を解決するために、酸化膜をSiC表面に堆積する手法により、良質の酸化膜を形成した。

その後、木本教授グループは、この研究を発展させ、実用上重要なトランジスタ構造(結晶面、不純物密度)で画期的な性能向上を達成した(2021年11月発表)。その成果を下記の3点にまとめた。また、酸化膜/SiC界面形成で用いたプロセスを下図に示した。

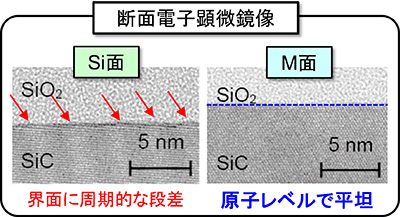

① 高性能SiC-MOSFET(トレンチ型構造)で必要となる、ウェハ表面に直交する結晶面(「A面」、「M面」)への酸化膜/SiC界面形成を行った。実験ではこのA面およびM面基板を準備し、上記の独自手法を用いてSiC-MOSFETを作製し、従来のSi面上MOSFET(従来の酸化膜形成法を採用)に比べて、6~7倍のチャネル移動度の向上を達成した。

② 実際に製造されるSiC-MOSFETでは、トランジスタの耐電圧の増大や信頼性向上のために、比較的高濃度のアクセプタ型不純物(アルミニウム)を添加したp型領域の上にMOS構造を形成する必要がある。今回、製造に用いられる高濃度p型SiCを用いてA面、M面上MOSFETを作製した結果、従来技術によるA面、M面上MOSFETに比べて6~80倍のチャネル移動度の向上を達成した。

③ ②の性能向上では、A面、M面の場合、酸化膜とSiC界面の平坦性が優れており、電子の散乱(走行の阻害)が著しく減少したためであると考えられる。

SiO2/SiC構造を形成する方法の模式図(上:従来法、下:本研究で提案する手法)

SiO2/SiC界面の断面電子顕微鏡像(M面では原子レベルで平坦な界面が得られている)

SiC パワー半導体の実用化で省エネを推進

本研究は、学理に基づく思考と実験を重ね、SiCパワー半導体で最も大きな問題とされてきた酸化膜/SiC界面の欠陥を大幅に低減したもので、実用上重要な構造(結晶面、不純物密度)で、SiCトランジスタのチャネル移動度を6~80倍向上させることに成功した。本研究の手法は、SiCパワー半導体の製造企業であれば、新たな特殊装置や高コストのプロセス導入は不要で、追加の設備投資なくSiC-MOSFETの量産に適用できる。また本研究成果を、作製プロセスがやや複雑になるものの微細化によって著しく性能を向上できるトレンチ型SiC-MOSFETに適用した場合には、①チップ面積縮小による低コスト化と、②信頼性の向上を達成することができる。特に①の低コスト化は、SiC-MOSFETのパワーエレクトロニクスへの応用展開を大幅に加速し、ひいては、SiCパワー半導体を通じた省エネ効果を一気に加速することが期待される。

現在、SiCパワー半導体の市場は世界で約700億円規模だが、5年後には2,000億円を超えると予想されており、SiCパワー半導体の普及により原子力発電所数基分の省エネが可能と試算されている。

またSiC-MOSFETは、本来であれば、チャネル移動度で200~250cm2/Vsといった数値が期待でき、大学での基礎研究が、欠陥低減などの基礎技術開発を通じて、SiCパワートランジスタの更なる性能向上を牽引することを期待したい。

- ナノテクノロジー・材料の成果一覧へ

- 事業成果Topへ

- English