ポイント

- 極微細な半導体ナノデバイスの電気的な特性を予測するには、量子力学的な効果を取り入れた複雑な計算に多くの時間がかかるため、回路設計に応用することは困難であった。

- 新方式のシミュレーターでは、計算量を従来の1,000分の1以下に削減し、従来1年以上かかるような量子論的効果を含んだ計算を、通常のパソコン1台により数日でできるようになった。

- ナノワイヤーやナノピラーなど新しいデバイスの回路設計に応用できると期待される。

JST 課題達成型基礎研究の一環として、大阪大学 大学院工学研究科 森 伸也 准教授とミリニコフ・ゲナディ 特任研究員らは、半導体デバイスの特性を原子レベルから計算できる新しいデバイスシミュレーターを開発しました。

現在の半導体集積回路の技術的・経済的な限界を打破するため、世界中で新しい構造、新しい材料のデバイスが数多く提案されています。その中から、実用に適した構造や材料を効率的に見つけ出すには、性能を予測するシミュレーターが必要です。ナノメートル(ナノは10億分の1)のサイズでは、量子論的な効果が性能に大きく影響するため、その効果を取り入れたシミュレーション技術の開発が盛んに行われています。しかし、現在提案されているいずれの方法も複雑な計算に多くの時間がかかるため、回路設計に応用することは困難でした。

今回研究グループは、ある特定のエネルギーの電子についてのみ計算し、さらに原子配置が乱れる部分は乱れの大きさを表すパラメーター1個のみをばらつき計算に使用することで高速化する新しい計算モデルを開発しました。その結果、従来1年以上かかるような原子論に基づく半導体集積回路の性能予測が、通常のパソコン1台の能力で数日あれば計算可能になりました。必要な計算量は従来の1,000分の1以下に削減されています。

この成果は、将来のナノワイヤー(電気を通すナノレベルの細線)やナノピラー(柱上のナノ構造)などの新しい構造のナノデバイスから構成される集積回路の設計に応用できると期待されるほか、さまざまなシミュレーション結果はさらに微細化して行く次世代の半導体集積回路の新たな設計指針の構築に貢献するものと期待されます。

今回の研究成果は、アメリカのワシントンで12月9日~11日(現地時間)に開催される「国際電子デバイス会議(IEEE International Electron Devices Meeting;IEDM)」で発表されます。

本成果は、以下の事業・研究領域・研究課題によって得られました。

戦略的創造研究推進事業 チーム型研究(CREST)

| 研究領域 |

「次世代エレクトロニクスデバイスの創出に資する革新材料・プロセス研究」

(研究総括:渡辺 久恒 (株)EUVL基盤開発センター 代表取締役社長) |

| 研究課題名 |

「原子論から始まる統合シミュレーターの開発」 |

| 研究代表者 |

森 伸也(大阪大学 大学院工学研究科 准教授) |

| 研究期間 |

平成21年10月~平成27年3月 |

JSTはこの領域で、微細化パラダイムのみでは実現できない機能・性能を持つ、革新的かつ実用化可能なエレクトロニクスデバイスを創製するための材料・構造の開発およびプロセス開発を行っています。上記研究課題では、膨大な計算時間を要する原子論的電子輸送シミュレーションを新しい計算アルゴリズム(R行列理論)の導入により短時間処理を可能とし、電子輸送シミュレーション、フォノン輸送シミュレーション、回路シミュレーションを統合したシミュレーターの開発を行っています。

<研究の背景と経緯>

半導体デバイス技術の発展は目覚ましく、ナノメートルレベルでの微細加工によりデバイスを高性能化・高密度化してきました。しかし、微細化が進むにつれリーク電流や開発コストなどの問題が顕著化し、さらに、デバイスサイズの縮小のみによる高性能化が困難になってきました。この限界を打破するため、従来の平面型シリコンMOS型トランジスター注1)に替わる、新しい構造・新しい材料のデバイスが数多く提案されています。多くの選択肢の中から、次世代デバイスとして実用に最も適した構造や材料を効率的に見つけ出すには、その性能を高速で予測できるシミュレーターが必要です。

これまでのシミュレーションでは、電子を古典的な粒子と考え、半導体デバイスをシリコン原子の集合体としてではなく、それらを平均化した連続体注2)として扱っていました。しかし、極めて微細な世界では、量子閉じ込め効果注3)やトンネル効果注4)などの量子力学的な効果のため電子を古典的な粒子として考えることが、もはやできません。さらに、デバイスがナノメートルのサイズになると原子の構造がデバイスの特性に大きな影響を及ぼし、連続体モデルでは説明ができなくなります。シリコン原子のわずかな配置の乱れや、1個の不純物の位置の違いにより、作製されたデバイスごとに特性が大きくばらつくことが問題となっています。このため、大きなサイズの性能予測シミュレーションでは、ナノメートルサイズの性能予測をすることは極めて困難です。

このような背景のもと、量子論的な効果を取り入れたデバイスシミュレーション技術の開発が盛んに行われています。しかし、いずれの方法も複雑な計算に多くの時間がかかるため、半導体集積回路の設計に応用することは現在のところ困難です。また、回路設計に不可欠なデバイス特性のばらつきを解析するには、原子配置や不純物原子の位置が異なる多数のサンプルに関するシミュレーションを行う必要があり、さらに計算時間が必要となります。そのため、原子論に基づくシミュレーションでのばらつき解析は現実的には不可能と考えられてきました。

<研究の内容>

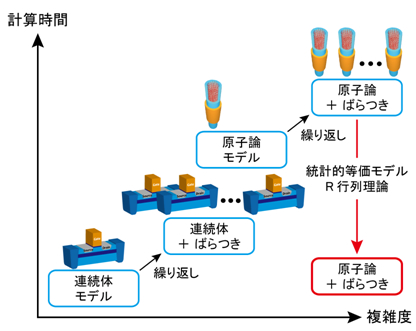

本研究では、電気的特性の高速な計算手法の1つであるR行列非平衡グリーン関数法注5)において、デバイスの電気的特性には関与しないエネルギーの電子についての計算を省略し、さらに個々のデバイスにおいて原子配置が乱れる部分は乱れの大きさを表すパラメーター1個のみをばらつき計算に使用することで高速化する、新しい計算モデルを開発しました。その結果、原子論的な効果を取り入れたナノデバイスの性能予測計算を、通常のパソコンで実行できるまでの高速化に成功しました(図1)。この高速化実現の鍵となる、従来必要だった計算の簡略化に関しては、最終的な計算結果であるデバイスの電気的特性に影響を及ぼさないことが、数学的に保証されています。

本研究で開発したシミュレーターを用いると、直径4nm、ゲート長10nm、全長30nmのシリコンナノワイヤートランジスター1,000個の伝達特性を、通常のパソコン1台を用いて、数日でシミュレーション可能です(図2)。この計算には従来1年以上の計算時間が必要となるため、現実的ではないと考えられてきました。さらに、パソコンを複数台用いる並列計算で、より短時間でばらつき解析が可能であり、また、スーパーコンピューターを利用すれば、さらに多くのサンプルのシミュレーションも可能です。

この高速化により、ばらつきを抑制できるデバイス構造・材料の探索や、原子論に基づく電気的特性シミュレーターの集積回路設計への応用が進むものと期待されます。

<今後の展開>

今後は、より現実的なナノ構造のデバイスについてのシミュレーションと実験データとの比較を行い、具体的な特性やシミュレーションの正しさを明らかにしていきます。また、トランジスター単体の性能予測だけでなく、複数のトランジスターから構成される電子回路としての性能を予測する回路シミュレーターや、電流によるトランジスター、配線の発熱を予測するシミュレーターなどとデータを連携することで、原子レベルから電子回路レベルまでの統合的シミュレーターの開発を行います。

これらの結果は、さらに微細化して行く次世代の半導体集積デバイスの新たな設計指針の構築に貢献するものと期待されます。

<参考図>

図1

原子論的デバイスシミュレーションは連続体モデルに比べ非常に多くの計算時間が必要です。回路設計に重要なばらつきの計算にはさらに多くの計算時間が必要です。新たに開発した統計的等価モデルにより、大幅な高速化が可能となりました。

図2 直径4nm、ゲート長10nmのシリコンナノワイヤートランジスター

(構造は(a)に示した)の1,000個の伝達特性のシミュレーション結果

わずかな原子配置の乱れの効果を原子論に基づいて計算すると、(b)上に示したように、1,000個のデバイスのそれぞれで異なったオン電流・オフ電流特性となることが分かりました。またI-V特性((b)下)を見ると、1,000個のデバイスの特性を平均した結果(黒)では、乱れを考慮しない場合の結果(青)に比べ、平均オン電流が60%も異なっており、乱れの効果を原子論に基づいて計算することが極めて重要であることが示唆されました。灰色の細かな線は、それぞれ1本が1個のデバイスを表しています。

<用語解説>

- 注1)シリコンMOS型トランジスター

- シリコン(半導体)基板の上に酸化膜、金属を形成した電子デバイス。金属に加える電圧により、半導体を流れる電流をオン・オフすることができる。金属(Metal)、酸化物(Oxide)、半導体(Semiconductor)の頭文字を合わせてMOSと呼ばれる。現在使われている集積回路はシリコンMOS型トランジスターが基本となっている。

- 注2)連続体

- 半導体は多数の原子から構成されている物質である。従来の半導体デバイスは大きいため、その原子論的な構造を平均化し、空間を連続的に物質が満たしていると考えることができる。このような扱いを連続体モデルと呼ぶ。デバイスがナノメートルのサイズになると原子論的な構造がデバイスの特性に大きな影響を及ぼし、連続体モデルでは説明ができなくなる。

- 注3)量子閉じ込め効果

- 量子力学的な粒子である電子を狭い空間に閉じ込めると、ある決まったいくつかの値のエネルギーを持つ電子しか存在できなくなる。このことを量子閉じ込め効果と呼ぶ。電子を閉じ込める空間のサイズが小さくなればなるほど、存在できるエネルギーの種類が限られてくる。そのため、ナノメートルスケールのデバイスでは、あらゆるエネルギーの電子が存在できる大きなデバイスとは大きく異なった特性を示す。

- 注4)トンネル効果

- 電子が自分のエネルギーより高いエネルギー障壁を通り抜けることができる量子的な効果。電子を古典的な粒子として考えると、電子は自分よりもエネルギーの高い障壁を通り抜けることは不可能だが、量子力学的な波としての電子はどんな高い障壁でも通り抜ける確率がゼロではなく、そのポテンシャル障壁が薄いほどより高い確率で通り抜けることができる。MOS型トランジスターでは、ポテンシャル障壁の高さにより、電流をオン・オフしているが、ナノメートルサイズのデバイスでは、ポテンシャル障壁を高くしてオフにしたつもりでも、トンネル効果で電子が障壁を通り抜けてしまい、電流が流れてしまうことが問題となる。

- 注5)R行列非平衡グリーン関数法

- デバイスシミュレーションを行うためには、電子の流れを記述する輸送方程式を仮定する必要がある。非平衡グリーン関数法は、最も広く用いられている量子力学に基づく輸送方程式の1つである。原子論的な計算では、デバイスに含まれる原子の個数が多いため、デバイス全体を一度に計算すると多くの時間が必要になる。R行列非平衡グリーン関数法では、一個一個の原子に関する計算を順に行い、デバイス全体の計算をするR行列アルゴリズムにより高速化を図っている。

<論文名>

「原子論に基づくナノデバイスのシミュレーション」(招待講演)

森 伸也1,2、ミリニコフ ゲナディ1,2、三成 英樹1,2、鎌倉 良成1,2、図師 知文3、渡邉 孝信3、植松 真司2,4、伊藤 公平2,4、宇野 重康2,5、土屋 英昭2,6

(1 大阪大学、2 JST-CREST、3 早稲田大学、4 慶應義塾大学、5 立命館大学、6 神戸大学)

<お問い合わせ先>

<研究に関すること>

森 伸也(モリ ノブヤ)

大阪大学 大学院工学研究科 准教授

Tel:06-6879-7731

E-mail:

<JSTの事業に関すること>

松尾 浩司(マツオ コウジ)

科学技術振興機構 戦略研究推進部

〒102-0076 東京都千代田区五番町7 K’s五番町ビル

Tel:03-3512-3525 Fax:03-3222-2063

E-mail: