ポイント

- スイッチング特性の良さを示すサブスレッショルド係数で世界最小の21mV/桁を達成

- 現在の半導体集積回路に比べ回路全体で消費電力を10分の1以下に低減が可能

- デジタル家電の待機電力を大幅カット、モバイル機器電池の消耗を半分に低減する夢の省エネデバイスへ道

JST 課題達成型基礎研究の一環として、JST さきがけ専任研究者の冨岡 克広、北海道大学 大学院情報科学研究科の福井 孝志 教授らは、半導体中のトンネル効果注1)を用いることで、従来のトランジスター(電子の流れを電圧で制御してオンオフするスイッチ素子)の理論限界を大きく下回る低消費電力トランジスターの開発に成功しました。この素子はあらゆる電子機器の省エネルギー技術へ応用できます。

パソコンのLSIやマイクロプロセッサなどで使われている半導体集積回路は、基礎となるトランジスタ-を小さくし、集積度を高めることで、高性能化、低消費電力化、低コスト化を実現してきました。しかし、近年、低消費電力化が頭打ちになり、半導体回路内の消費電力が大幅に増えています。低消費電力化の妨げになっているのはスイッチに利用しない電流が漏れ出すリーク電流と、トランジスターのサブスレッショルド係数注2)に理論的な限界(60mV/桁)があるためです。これまでのトランジスターのサブスレッショルド係数は60~100mV/桁でした。

本研究グループは、トランジスター構造を縦型にし、ラップ状にゲート電極を作ることで、電流のリークを抑えました。さらに、ナノメートルスケールの結晶成長技術によってシリコンとインジウムヒ素(InAs)ナノワイヤ界面を形成し、その界面で生じる電子のトンネル効果による電流をスイッチ素子に使うことで、サブスレッショルド係数の理論限界60mV/桁を大幅に超える21mV/桁を初めて達成しました。この結晶成長技術を用いた界面構造は、従来の不純物ドーピングや化合物半導体などの手法における技術的なボトルネックを回避できるため、本来トンネルトランジスターが示せる小さなサブスレッショルド係数を実現しました。

この要素技術を応用すると、現在の半導体集積回路に比べ、回路全体の消費電力を10分の1以下に低減できます。また、あらゆるデジタル家電の待機電力やモバイル機器の電池の消費を大幅にカットすることができます。今回、世界中の企業がしのぎを削る中、少人数の研究グループで、世界にさきがけて開発に成功しました。本研究は、北海道大学 量子集積エレクトロニクス研究センターで行われ、その要素技術は、すでに日本を含む世界5ヵ国・地域に特許出願されています。

本研究成果は、2012年6月12日から15日(米国・ハワイ時間)に開催される半導体国際会議では最高峰の1つである「VLSIシンポジウム2012」での招待講演として12日に発表されます。

本成果は、以下の事業・研究領域・研究課題によって得られました。

戦略的創造研究推進事業 個人型研究(さきがけ)

| 研究領域 |

「革新的次世代デバイスを目指す材料とプロセス」

(研究総括:佐藤 勝昭 東京農工大学 名誉教授)

|

| 研究課題名 |

「Si/III-V族半導体超ヘテロ界面の機能化と低電力スイッチ素子の開発」 |

| 研究代表者 |

冨岡 克広(科学技術振興機構 さきがけ専任研究者) |

| 研究期間 |

平成21年10月~平成25年3月 |

JSTはこの領域で、CMOSに代表される既存のシリコンデバイスを超える革新的な次世代デバイスを創成することを目標として、環境やエネルギー消費に配慮しつつ高速・大容量かつ高度な情報処理・情報蓄積・情報伝達を可能とする新しい材料の開拓およびプロセスの開発を図る挑戦的な研究を対象とするものです。

<研究の背景と経緯>

パソコンのLSIやマイクロプロセッサなどで使われている半導体集積回路は、構成要素のトランジスターを小さくし集積度(トランジスターの数)を増やすことで、性能を高めてきましたが、トランジスターを小さくすることには限界が生じつつあります。トランジスターを小さくすると、スイッチに使用しない電流が漏れ出すリーク電流が大きくなるためです。そのため、現在では、トランジスター構造を平面から立体的な構造にすることでリーク電流を抑制し、性能を高める手段が取られています。さらに、小さな電圧でシリコンよりも電流が流れやすい材料などの導入も検討されています。これらの技術を使うことは、急場しのぎにはなりますが、いずれ限界が訪れます。これは、トランジスターのサブスレッショルド係数に理論的な限界があるからです。

集積回路の低電力化には、一つ一つのトランジスターの駆動電圧を小さくすることが有効です。駆動電圧を小さくするためには、サブスレッショルド係数を小さくすることが必要ですが、普通のトランジスターでは、半導体の中を流れる電子の数を電圧で制御して、電流をオンオフしているので、サブスレッショルド係数には理論的限界があります。これは、室温で60mV/桁です。どのような構造や材料を使ったとしても、この方法でオンオフする電流を使う限り、この値を下回るスイッチ素子は実現できません。そのため、サブスレッショルド係数の限界を突破するような、低電力スイッチ素子の開発研究が欧米を中心に盛んに行われていますが、世界的な集積回路メーカーでさえもサブスレッショルド係数を60mV程度しか低減できていません。これは、従来の不純物ドーピングや化合物半導体だけでヘテロ接合を作る手法では、ナノメートル構造に不純物原子を制御良く作る技術がないことや、化合物半導体だけでは酸化物や半導体界面の悪さが悪影響を及ぼすことがボトルネックとなって、理論限界を突破するようなスイッチはできなかったためです。

<研究の内容>

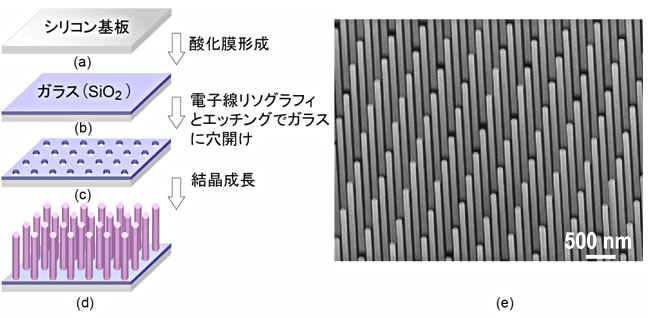

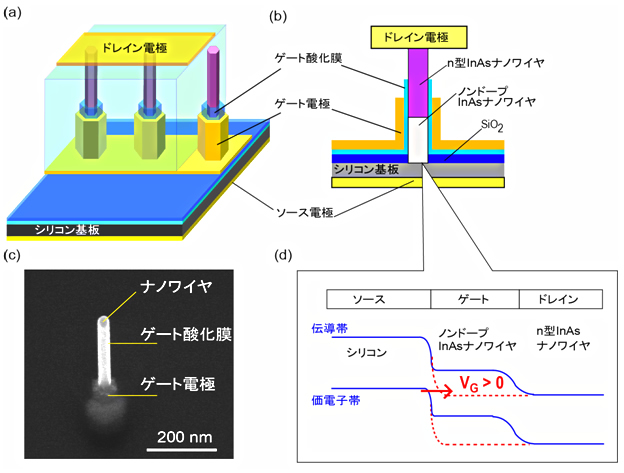

今回の研究では、半導体結晶成長技術(図1)を駆使し、シリコンと化合物半導体のナノ接合を作ることによって、新しい界面を形成し、その界面にできる障壁を電子が量子的に通り抜けるトンネル効果を使い、障壁の大きさを電圧で制御して電流をオンオフすることが可能な、低消費電力型スイッチ素子として機能するトンネルトランジスターを開発しました(図1、図2)。この界面を使ったトンネルトランジスターは既存のボトルネックを回避できるもので、世界最小のサブスレッショルド係数21mV/桁を達成しました(図3)。この素子をさらに高性能化すると、回路全体で現在の半導体集積回路に比べ1/10以下に消費電力を低減させることが期待できます。

【原理の説明】

上記の現象は、シリコンと化合物半導体接のナノ接合を作ると、図2(d)のようにバンド構造に段差を生じます。オフ状態では、シリコンの中の電子がこの間を通ることができないため、電子を流すことができませんが、ゲート部分で電圧を加えて、段差を大きくすると、シリコンの価電子帯と化合物半導体の伝導帯のエネルギーが重なるようになって、接合部分にできた薄い障壁を電子が量子的に通り抜ける現象(トンネル効果)が生じます。これにより電流が流れるようになったと考えられます。結晶成長技術で非常に小さな領域に、きれいなナノ接合を作ることがポイントです。

<今後の展開>

現在のIT社会を支えているパソコンやスマートフォン、デジタル家電に使用される半導体集積回路は数多くの製品に搭載されており、いずれも半導体トランジスターからなる集積回路を用いているため、ジュール熱によって多大なエネルギー損失を生じます。この消費電力の削減はあらゆる電子機器の大きな問題であり、トランジスター開発は消費電力削減との戦いといってもよい状況です。

本研究で初めて開発された低電力スイッチ素子は、従来のトランジスターが抱えていた発熱によるエネルギーロスの問題を根本的に解決しうるものです。集積回路を搭載した製品では、デジタル家電の待機電力を大幅にカットすることができ、また、モバイル機器の電池の消耗を半分にすることが期待できます。環境に配慮した省エネルギーな電子技術開発への貢献が期待できます。

<参考図>

図1 半導体結晶成長技術:選択成長工程の流れとナノ構造の作製例

- (a)シリコン基板

- (b)シリコン基板にガラス(SiO2)を形成する。

- (c)電子線リソグラフィとエッチングでガラス膜に穴を開ける。

- (d)結晶成長で半導体ナノワイヤを作製する。

- (e)選択成長工程で作製したシリコン基板上の化合物半導体ナノワイヤ。直径80ナノメートルの垂直自立ナノ細線が林立していることが分かる。この技術を使うと、シリコン基板上に、化合物半導体からなるナノメートルスケールの柱を立てることができる。

図2 開発したトンネルトランジスター素子

-

(a)縦型三端子(ドレイン・ゲート・ソース電極)構造の模式図。シリコン基板上に形成された垂直自立ナノ細線の側面が、ゲート酸化膜とゲート電極で包まれた構造を有している。

- (b)縦型三端子構造の断面図。シリコン基板上に形成されたナノワイヤは、図に示すように、不純物を入れていないノンドープ層InAs層と、不純物を入れたn型InAs層で作られている。今回のアイデアは、シリコン基板とノンドープInAsナノワイヤのナノ接合部分にできるバンド構造を利用している。

- (c)作製した新型トランジスターの電子顕微鏡像。試作したスイッチ素子を斜め方向から観察した図。直径30ナノメートルのInAsナノワイヤの側壁にゲート酸化膜・ゲート電極が形成されている。図(a)に示すように、ナノワイヤの側壁全面がゲート酸化膜で覆われ、ゲート電極で包まれていることが分かる。

- (d)スイッチ素子構造のバンド構造。青色線が、ゲートで電圧をかけてない時のバンド構造。電圧をかけていないときは、シリコンの電子は、InAsナノワイヤへ移動できないが、正のゲート電圧をかけると、バンド構造の一部は図中の赤色破線のように変化し、シリコンの価電子帯とInAsナノワイヤの伝導帯が近づく。これらが近づき、シリコン側の電子がInAsナノワイヤ側へトンネルして移動することで電流が流れる。

図3 開発した低消費電力スイッチ素子のスイッチ特性

オフ状態では、シリコンの中の電子が図2(d)のシリコンとInAsナノワイヤの間を通ることができないため、電子を流すことができませんが、ゲート部分で電圧を加えて、段差を大きくし、図2(d)の赤色破線のようにすると、接合部分にできた薄い障壁を電子が量子的に通り抜ける現象(トンネル効果)が生じます。今回開発した素子は、ゲート電圧が-0.4V以上で電流が流れはじめます。サブスレッショルド係数は室温で21mV/decであり、普通のトランジスターよりも小さなサブスレッショルド係数になります。

<用語解説>

- 注1) トンネル効果

- エネルギー的に通常は超えることのできない領域を粒子が量子力学的に一定の確率で通り抜ける現象。半導体のトンネル効果は、江崎 玲於奈 博士によって発見された。

- 注2) サブスレッショルド係数

- トランジスターの電流(ドレイン電流)が電圧(ゲート電圧)に対して、増加する割合を示す値。

<発表タイトル>

“Steep-Slope Tunnel Field-Effect Transistors Using III-V Nanowires/Si Heterojunction”

(III-Vナノワイヤ/Siヘテロ接合を用いたトンネルFETの作製)

doi: 10.1109/VLSIT.2012.6242454

<お問い合わせ先>

冨岡 克広(トミオカ カツヒロ)

科学技術振興機構 さきがけ専任研究者

〒060-8628 北海道札幌市北区北13条西8丁目

Tel:011-706-7176 Fax:011-716-6004

E-mail:

福井 孝志(フクイ タカシ)

北海道大学 大学院情報科学研究科 教授

量子集積エレクトロニクス研究センター センター長

〒060-8628 北海道札幌市北区北13条西8丁目

Tel:011-706-6870 Fax:011-716-6004

E-mail:

木村 文治(キムラ フミハル)、原口 亮治(ハラグチ リョウジ)、橋本 典親(ハシモト ノリチカ)

科学技術振興機構 戦略研究推進部

〒102-0076 東京都千代田区五番町7 K’s五番町

Tel:03-3512-3525 Fax:03-3222-2063

E-mail: