### 研究開発項目

# 1. 拡張性を有する誤り耐性 Si 量子ビットデバイス技術

## 2023年度までの進捗状況

### 1. 概要

本研究開発項目では、誤り耐性を有する大規模化に適した Si 量子ビットデバイス技術の開発を目指します。これまでの少数量子ビット系で達成された誤り耐性閾値を上回る高精度な量子ビット制御を発展させ、これらの制御精度を損なわずに大規模化を進め量子誤り訂正を実装可能なアーキテクチャ・量子ビットレイアウト・試料構造・信号伝送技術を開発する必要があります。これらの要素技術を確立し、真に拡張性を有する Si 量子ビットデバイスを追究します。

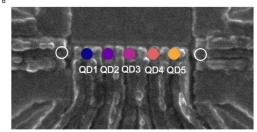

図1 Si/SiGe 量子井戸基板に作製した5量子ビット試料の電子顕微鏡写真。

大規模な量子ビットデバイスにおいて量子ビット制御精度の再現性を確保するため、本項目では各物理パラメータを試料構造に応じて自在に設計しながら均一性を維持することのできるSi/SiGe量子井戸型の量子ビットデバイスを作製します(図1)。産業プロセスとも連携し、高精度な量子演算操作を実証することで、大規模な誤り耐性量子計算の実現に向けたブループリントを描くことを目指します。

### 2. これまでの主な成果

- ① 直列5量子ビット試料を作製し、各量子ビットの初期 化、読み出し、量子ゲート操作を実証

- ② 2量子ビットの制御位相ゲート操作におけるエラーの メカニズムを解析し、その補償方法を解明

- ③ 量子誤り訂正に求められる高速・高忠実度な量子ビット読み出しを実証

- ④ 量子ビット読み出し結果に応じたフィードバック制御 により、量子ビットのアクティブリセットを実証

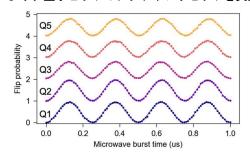

図2 5つの量子ビットそれぞれに共鳴するマイクロ波によって駆動されたコヒーレント振動(ラビ振動)。

①では5つの量子ビットを直列に配置した試料を作製し安定的に動作させることに成功し、各量子ビットの初期化・読み出しとゲート操作を実証しました(図2)。量子ビット性能から得られた知見をデバイス構造にフィードバックし、量子誤り訂正の実装に向けた開発指針を得ました。

②では量子演算においてボトルネックとなり得る2ビットゲート操作におけるエラーをゲートセットトモグラフィーと呼ばれる手法で解析し、エラーを最小化する制御波形を体系的に生成しました。また、エラーの起源に関わる量子ビットのノイズ相関を検出・解析しました。

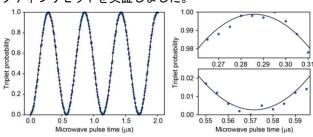

③、④では、量子誤り訂正の実装時に必要不可欠な高速・高精度量子ビット読み出しとフィードバック制御を実現しました。量子ビットのコヒーレンス時間(Љ\*~10µs)よりも十分に短い積算時間(~1µs)で 99%以上の高忠実度読み出しを初めて実証しました(図3)。さらに量子ビット読み出しの結果をリアルタイムで量子ビット制御波形にフィードバックすることで、量子ビットを所望の状態に初期化するアクティブリセットを実証しました。

図3 スピンのパリティ読み出しを利用した高忠実度な量子ビット測定によって得られた高明瞭なラビ振動データ。

### 3. 今後の展開

複数量子ビットの高忠実度制御、高忠実度読み出し、フィードバック制御といった量子誤り訂正に求められる技術要素を着実に実現しています。今後はさらなる大規模化に向けて、十字等の擬2次元配列の制御性の検証や、スピンシャトリング等の遠隔量子ビット結合技術を応用した量子ビットレイアウトの開発、密集した量子ビットに精確な制御信号を伝達しシグナルインテグリティを担保する技術の開発に取り組みます。これらは誤り耐性量子計算機の実現に一つも欠かすことのできない要素であり、これらの要素を統合したプラットフォームの確立を目指して研究を推進します。

### 研究開発項目

# 2. 中距離量子結合技術

# ここから、新・未来へ MOONSHOT RESEARCH & DEVELOPMENT PROGRAM

### 2023年度までの進捗状況

### 1. 概要

半導体量子ビットを大規模化するために必要な空間的な 自由度を確保するため、スピン量子ビットの中距離量子結 合に取り組みます。半導体のナノスケールの集積性能を最 大限に引き出すためには、量子情報の制御に必要なマイク ロスケールの回路を考慮し、量子ビットのプロセッサーを 構成する必要があります。中距離量子結合技術の開発によ り、量子ビットアレイ間の非局所的な結合を実現し、柔軟 なビット配置の設計が可能になります。

本研究開発項目では、配線や電圧要件の異なる伝送方式の研究開発を行い、各段階に応じて効率的な方式を選択できるよう広く取り組みます。スピン量子ビットの伝送には、既存の量子ビットの安定的閉じ込め、および制御技術に加え、半導体量子ビットを空間的に移動させる仕組みが必要です。その上で、量子計算素子内に組み込む効率の良い結合技術として採用するために、半導体中を移動するスピン量子状態の物理の解明から、原理実証や、量子結合機能を達成する試作構造の開発を行います。スピン量子ビットの伝送を基に、量子ビットアレイの結合を可能にし、誤り耐性付き量子ビットの新たな構成の基盤を築くことを目指します。

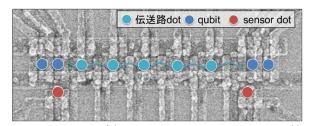

図1 中距離伝送と量子結合の模式図。

### 2. これまでの主な成果

半導体量子ビットの中距離伝送としていくつかの候補が 検証されている中、本研究ではこれまで、電荷を移動させ るシャトリング方式と、スピンを移動させるスピン鎖方式 の2種類の研究開発を推進してきました。

#### - スピンを電子ごと運ぶシャトリング方式

電荷結合素子として半導体産業でなじみのある伝送形式が、単一電子スピン量子ビットにも適合しやすいと考えられます。その際、電子スピンを安定して閉じ込め、コヒーレンスを保つことが重要です。これまで、もつれ状態を3サイト先へ順次トンネルさせること、あるいは量子ビットを2サイト間で多数回往復させる検証などが先行し、項目1の予備成果として2サイト先の量子ビットとの二量子ビットゲートが示されています。

図2 シャトリング専用量子ドットアレイの電子顕微鏡写真。

近年は、類似する形として、周期的な電圧信号で閉じ込めポテンシャルを形成しつつ、より遠くへ流すコンベイヤーモードが注目され、量子ビットの伝送に専用の量子結合器を開発する本項目に適合する有望な方式として、デバイスの試作と評価の準備を継続しています。

#### - スピンを交換する相互作用を連ねたスピン鎖方式

従来より、位置を固定して量子ビットを並べる構造が信頼されてきたことから、仲介する状態にスピンを埋めておく方式にも取り組んでいます。特に、交換相互作用で常に結合したスピン鎖の状態を介した、断熱伝送方式に現在取り組んでいます。この方式の利点は、伝送に使えるスピン鎖状態に一度初期化できれば、始点と終点の電圧だけで操作が完了し、遅延の少ない伝送が期待される点です。

図3 スピン鎖方式の転写模式図と、ショートカット法適用時の量子ビット状態の模式図。

### - 断熱操作に関連する物理

乱雑さに対抗する性質を持つ伝送方式を模索する中で、 共通する物理として断熱操作に焦点を当て、従来低速であった操作に適切な最適化を施すことで数倍の高速化と桁違いの精度向上が見込める、実証実験の成果を挙げています。

### 3. 今後の展開

今後は引き続き初期の実証実験に向けて設備の拡充を進め、離れた量子ビット間の結合実験を目指します。そして項目間との連携を密にし、シリコン量子コンピュータの条件に近いデバイス設計の基で評価を蓄積し、誤り耐性閾値を容易に超える最適化を検討していくことで、プロセッサーを構成する要素として価値のある量子結合器の開発に取り組みます。

### 研究開発項目

# 3. 誤り耐性を満たす同位体制御 Si/SiGe 基板技術

### 2023年度までの進捗状況

### 1. 概要

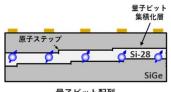

本研究開発項目では、誤り耐性を有するシリコン量子計 算機の実現に向けて、量子ビットデバイスと中距離量子結 合を搭載するのに必要となる、同位体制御されたシリコン・ シリコンゲルマニウム(Si/SiGe)の基板材料の開発を目指 します。量子ビットの性能を最大限に引き出し、誤り耐性 閾値を超えた量子ビットを自在に配列制御するために、集 積化層となる同位体 Si-28 が SiGe 薄膜に埋め込まれた高 品位な量子井戸型の基板材料が必要となります。

量子ビット配列

図1量子ビット配列を集積化する同位体制御 Si/SiGe 基板 の概略図(左)と電子顕微鏡による断面構造写真(右)。

本項目では、量子ビットの制御性と配列自由度を格段に 向上させるため、①量産プロセスに適応し、高品質な同位 体層の成膜が可能な同位体制御技術、及び②原子ステップ というヘテロ界面の段差を抑制する界面制御の基盤技術の 開発に取り組みます。また、③同位体基板の材料性能を広 範囲に評価するプロセス基盤の技術確立を並行し、半導体 産業との互換性を維持して大規模な誤り耐性型シリコン量 子計算の実現に向けた新たな基盤技術の確立に挑戦します。

### 2. これまでの主な成果

#### ① 高品質成膜を可能とする同位体制御技術の開発

配列した量子ビットを安定的に動作させ、量子状態を長 距離に渡ってコヒーレントに伝送するには、集積化するス ケールで同位体基板を高品質化し、試料構造内のポテンシ ャルの均一性を確保することが重要です。これまでに、電 荷トラップとなる不純物濃度の低減、同位体層での界面の 急峻性と平坦性の向上、また歪みや組成の揺らぎに起因す る不均一性を抑制した小規模な同位体基板を試作し、量子 ビットを搭載する基板側全体の高品質化要件に基づいた量 産対応の同位体成膜システムの導入・整備を行いました。

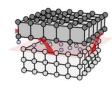

② 軽元素を用いた界面制御に向けた要素基盤技術の開発

量子ビット配列と干渉し得る界面ステップの微視的起源 の理解に基づいた発生抑制手法として、軽元素である水素 の欠陥終端や結合切断といった相反的特性を利用し、同位 体基板の内部構造改変による新たな界面制御技術を考案し ました。この原理検証に向けた基盤技術として、効率的な 制御条件の探索を可能にする高スループットな顕微評価技 術を開発し、これまで直接測定が困難であった同位体界面 のステップ間隔をあらわす構造因子をマルチスケールで精 密測定する技術を開発しました。これにより、同位体基板 に集積化する量子ビット配列の設計指針として有用な結果 を得ました。

図2軽元素導入による基板界面制御の概念図(左)、試料断 面構造(中)、ステップ構造因子の局所空間分布(右)。

図3 同位体基板を大面積評価する一次元配列したスプリ ット型デバイスのモデル設計(左)と試作構造(右)。

### ③ 同位体基板の大面積プロセス評価技術の開発

量子ビットを大規模集積化する同位体基板に内在する結 晶欠陥に関して、広範囲にデバイス性能評価する技術開発 に取り組みました。量子ビットの性能を律速し得る、同位 体基板内の電気的雑音を高速計測する高周波ボードの設 計・試作を行いました。さらに大面積評価するプロセス技 術も並行開発し、汎用パターニング技術で試作可能な電極 構造としてスプリット型構造を採用し、一次元配列による デバイス設計・試作を進めました。これにより同位体基板 のフィードバック開発を加速することが期待できます。

### 3. 今後の展開

誤り耐性閾値を超える量子ビット配列を搭載可能で、量 子状態を転送する中距離量子結合のスケールで結晶欠陥に よる散乱がない、拡張性を有する高品位な同位体制御 Si/SiGe 基板の技術開発を進めます。今後、軽元素導入に よる界面制御技術の原理検証を進め、同位体基板の大面積 デバイス評価による実用性の検証と改善に取り組みます。 また、同位体基板の供給と項目間での知見共有を進め、半 導体産業との連携強化に向けた根幹技術としていきます。 これらの要素技術を基に、同位体基板の品質と量子ビット のデバイス性能を紐づける新たなスケーリング技術の確立 を目指し、真に誤り耐性を満たすシリコン量子プラットフ ォームの実現に向けた研究開発を推進します。

### 研究開発項目

# 4. 新原理電子波束量子ビットの開発

### 2023年度までの進捗状況

### 1. 概要

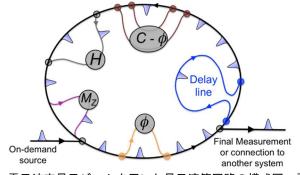

本研究項目では、半導体量子回路を緩和・変形せずに伝搬する電子波束の状態で定義される量子ビットを用いた新しい量子計算手法の実証とその基盤技術の開発を行っています。将来的には、電子源から生成した電子波束量子ビット列をループ回路に導入し、多数の電子波束が同じ量子回路を繰り返し、条件を変えながら伝搬するようなシステムを構築し、少ない量子回路で多数の波束量子ビットを任意に制御することを目指します。

電子波束量子ビットを用いた量子演算回路の模式図。電子波束量子ビットは電子源からオンデマンドに生成され、ループ型回路に組み込まれた少数の演算回路で状態操作が行われる。ループ型回路を伝搬中、電子波束はデコヒーレンス耐性が高い Time-bin 量子ビットの形で保持される。

この達成のため、電子波束量子ビットを高密度で生成し、 高い忠実度で操作する技術の開発(課題1)、及び電子波束 の伝導の量子力学的な制御と電子波束の単一波束単位での 読み出し技術の開発(課題2)に取り組んでいます。

### 2. これまでの主な成果

電子波束量子ビットを高密度で生成し、高い忠実度で操作する技術の開発に取り組んでいる課題1では、単一伝導モードの干渉計を用いた電子波束の量子干渉実験を行うための試料開発と実験系の構築を行いました。設計した試料は電子波束量子ビットの1量子ビット演算に加えて2量に加えて2量にから、実験の準備を進めています。また、実験系については特に号を整えましたが可能なセットアップを整えました。また、並行して実験を進め、研究の進捗を加速させるため、従来の実験セットアップに加え、新たに希釈冷凍機の導入を行い、測定環境を整備しました。さらに、高密度な電子波束の生成技術として光パルスを電気パルスに変換する技術の開発に取り組み、実験に必要となるレーザーシステムを導入しました。

電子波束量子ビット試料の電子顕微鏡写真(左)、冷凍機中で試料を搭載するコールドフィンガー(中央)、希釈冷凍機内部の構造(右)。

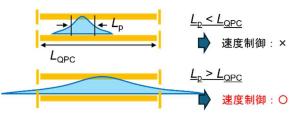

電子波束の伝導の量子力学的な制御と電子波束の単一波 東単位での読み出し技術の開発に取り組んでいる課題2に 関しては、電子波束の新しい速度制御法の開発に取り組み ました。その結果、電子波束の長さに対して適切な距離で2個の局所的な閉じ込め構造を配置し、その閉じ込めを制御することで、電子波束の速度が制御可能であることを実証しました。この成果は電子波束に対する遅延回路などへの応用が可能です。また、単一電子波束の読み出し技術の実証に向けて、試料の設計を行うとともに、希釈冷凍機を始めとした実験セットアップの整備を行いました。2024年度には整えたセットアップで単一電子波束の読み出し実験を開始する予定となっています。

局所的な閉じ込めを用いた電子波束の速度制御。 $L_{\rm p} > L_{\rm QPC}$ のとき、局所的な閉じ込めで電子波束の制御ができることを示している。

### 3. 今後の展開

課題1では、光パルスと電気パルスの変換に基づくピコ 秒オーダーの幅の電子波束の生成技術の実証や高い忠実度 の電子波束量子ビット操作の実証を行います。また、timebin量子ビットと which-path量子ビットの変換技術の実証 実験に取り組み、電子波束量子ビットの長距離コヒーレン スの実証を行います。課題2では、単一電子波束の読み出 し実験に取り組み、10個以下の電子を含む電子波束の単発 測定による検出を目指します。これらの技術は、電子波束 を用いた量子コンピュータ実現に向けた基盤技術となります。