## 研究開発項目

## 1. ハードウェア向け誤り訂正アルゴリズムと FPGA によるバックエンドシステム

## 2024年度までの進捗状況

## 1. 概要

本研究開発項目では、誤り訂正に必要なエラーシンドローム解析を高速かつ低遅延で行える誤り訂正バックエンドシステムの開発を行う。そのために、次の3課題を実施している。課題1では、高速・低遅延でかつスケーラブルなエラーシンドローム解析を実現するための誤り訂正ハードウェアと、FPGAクラスタによる誤り訂正バックエンド(BE)システムの開発を行う。課題2では、BEシステムのハードウェア実装方式最適化による性能改善について調査するため、量子誤り訂正(QEC)コア回路主要部分のASIC化の検討とその性能評価を行う。課題3では、項目2の量子フロントエンド(FE)および誤り訂正BE相互間を接続する高性能かつ高信頼な相互結合網技術、ならびに誤り訂正BEの大規模化に備えてFPGAクラスタの高信頼化技術の開発を行う。

## 2. これまでの主な成果

## 課題1) 誤り訂正ハードウェアとFPGAクラスタ

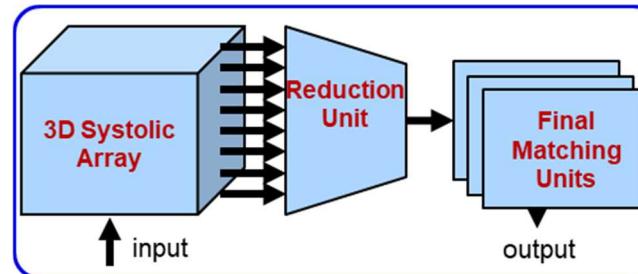

誤り訂正では、物理Qubitから得られるエラーシンドロームグラフに対して最小重み完全マッチング問題を解く必要がある。このために、FPGAハードウェアとして効率的に実行可能な図1のシンドローム部分グラフアルゴリズムを開発し、さらに、複数FPGAによる並列実行に向けてアルゴリズムの改良および拡張を行った。併せて開発したソフトウェアシミュレータにより評価を行ったところ、アルゴリズムの最適化と並列化により論理誤り率が大幅に改善されることを確認した。

また、FPGA向けに開発したシステムオンチップ(SoC)であるAFU Shellを用いて、本アルゴリズムを量子誤り訂正(QEC)回路モジュールとしてFPGA上に実装し、その機能検証と面積・動作周波数の評価を行った。符号距離に対する回路資源消費量と処理性能の特性を分析した上で、複数FPGAによる並列化に向けて、リダクションユニットの出力を多数のFPGA上に実装したファイナルマッチングユニットに分配する方式を第一候補とすることとした。

図1 複数のファイナルマッチングユニットを有するシンドローム部分グラフアルゴリズムのハードウェア設計

## 課題2) QECコアのASIC向け評価

QECコアの具体的なハードウェア実装方法、ASIC向けの最適化手法について検討した。それぞれの要素回路について論理合成、配置配線することで定量的な性能指標を評価するとともに、各要素回路のASIC実装上性能ボトルネックとなる部分について検討した。

また、QECコアの中核を担う誤りデコーダについてテストチップによる評価を進めるとともに、ASIC向けのマイクロアーキテクチャを策定した。22-nm CMOS製造プロセスで製造したテストチップを実測評価し、先行するデコーダーに

対する優位性を確認した。また、提案するASIC向け最適化による性能改善についてもシミュレーションで検証した。

## 課題3) ディペンダブルなエラー訂正バックエンドの実現

FE-BE実証システムの開発に向けて、FEで読み出されたシンドローム情報を転送するEthernetフレームを縮約することで効率的にネットワークの帯域幅を削減する手法を開発し、FPGAへの実装を行った。FE実機がなくともBEによる誤り訂正システムの開発が進められるよう、計算によって事前に生成したシンドローム情報を実データレートでネットワークに送信するフロントエンドエミュレータを実装し、運用中である。これにより、36台までのFEを模擬したネットワークトラフィックを生成可能であり、現時点でも利用可能な物理Qubit数に対しても充分である。

また、BEのFPGAクラスタ内での通信の効率化を視野に、Ethernetに代わる高速・低レイテンシの多対多通信の方法を検討し、概念検証用のハードウェアを開発した。

## 3. 今後の展開

これまで、複数FPGAでのスケーラブルな処理に対応可能な誤り訂正バックエンドシステムの実現に向けて、量子誤り訂正アルゴリズム、そのハードウェア設計、FPGA SoCやフロントエンド(FE)-バックエンド(BE)間ネットワーク等、システムを構成する基本的な技術要素を開発してきた。今後は、アルゴリズムの改良を継続し、100物理量子ビット規模の量子誤り訂正に対するスケーラビリティを示しながら、FPGAクラスタ上に並列量子誤り訂正ハードウェアのBEシステムを実装する予定である。さらに、項目2と連携して、FEとBEを接続した実証システムを構築し、実際の超伝導量子デバイス、または量子誤りシミュレーション結果を用いて量子誤り訂正の実証を行う計画である。

## 2. 量子ビット制御フロントエンドの先鋭化

### 2024年度までの進捗状況

#### 1. 概要

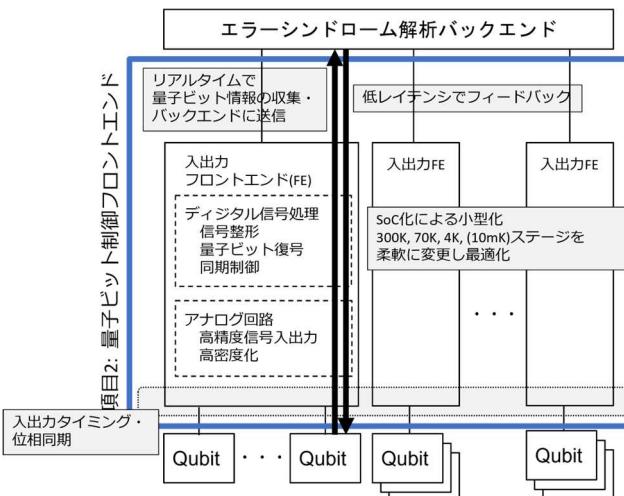

本研究開発項目では、スケーラブルな高集積量子誤り訂正システムを実現するための量子ビットの制御と観測を行うフロントエンド（図1）の性能向上と小型化を目指す。

具体的には、(1) デジタル信号処理を活用したシステム簡略化と信号品質の向上、(2) システムの高集積化による小型化、(3) 複数ユニットの同期に必要なクロック分配の効率化、(4) エラーシンドローム解析バックエンドと連携して誤り訂正処理を行う観測およびフィードバック制御の実装、について個別に取り組んできた成果を、実際の超伝導量子ビットを用いて評価するために統合した。また、研究開発してきた技術を超伝導以外の方式の量子ビットの制御に利用

するためのシステムアーキテクチャの検討を行なった。

#### 2. これまでの主な成果

2023年度までに要素開発を行った技術を100量子ビット程度向けに評価できるシステムとして、信号処理ボード、制御ボード、筐体を開発した（写真1）。

写真1：100量子ビット程度の制御を想定した制御装置

2023年度までに開発した実験ボードおよび集積化したRF回路モジュールを用いて、実際の量子ビットを制御するためのシステムとして構築するために、モジュールのサイズの調整や統合化のために必要なボードの開発をおこなった。

エラーシンドローム測定用のFPGAファームウェアを100量子ビット向けの環境で利用できるよう複数の装置で同期して実行できるように拡張した。拡張ファームウェアを複数の制御装置上で動作させ、量子ビット制御時と同様の同期精度でエラーシンドローム測定処理を繰り返し実行できることを確認した。

加えて、超伝導量子ビット以外の量子コンピュータへの技術展開を目的として、イオントラップおよび中性原子を用いる量子コンピュータ向け量子ビットの制御システムの構成として、ヘテロジニアス構成の制御システムアーキテ

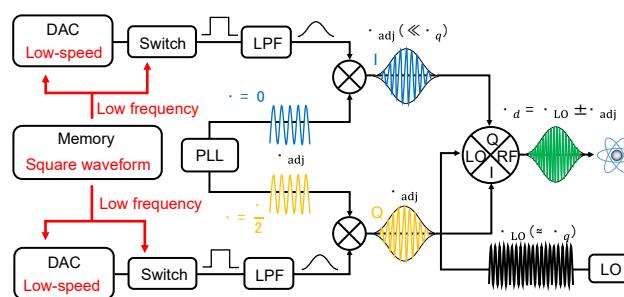

クチャを検討し（図2）、その有効性を評価するためのプラットフォームを実装した。

図2：ヘテロジニアス構成の制御システムアーキテクチャ

#### 3. 今後の展開

2025年度では、これまでの研究開発要素をシステムとして組み合わせた100量子ビット程度向けの制御装置を用いて、実際の量子ビットの制御・観測をおこない、実環境における繰り返し動作や多系統の制御における同期精度、信号品質、フィードバック遅延などの観点で、性能を評価する。また、誤り訂正処理に必要な量子ビットの制御と観測ができる方式を確立し、エラーシンドローム解析バックエンドと組み合わせて誤り訂正が可能なシステムが実現できることを示す。

加えて、他の量子ビット方式の量子コンピュータに対して検討したアーキテクチャを、実際の量子ビットの制御に利用し、性能を評価する。

## 研究開発項目

## 3. 光/Cryo CMOS 集積回路によるスケーラブルな古典-量子インターフェース

## 2024年度までの進捗状況

## 1. 概要

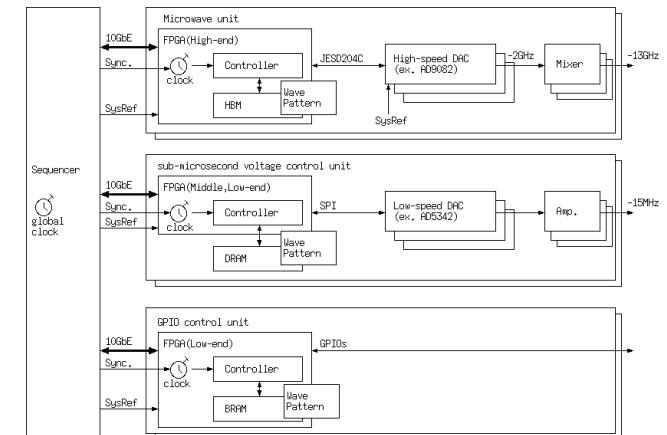

スケーラブルな量子コンピュータを実現するためには、室温環境-極低温環境をまたぐ膨大な配線をコンパクトにしつつ、古典-量子間で通信される膨大な量のデータを効率的に伝送する必要がある。本研究開発項目では、図1の通り、古典-量子の境界で動作する光/Cryo CMOS 集積回路を開発し、高効率な情報伝送を実現する。キー技術として図1の①~④を開発している。進捗状況として、(a)量子ビット制御アーキテクチャ、(b)光集積回路の低温特性測定、(c)Cryo CMOS 向け PDK、(d)Cryo 集積回路の設計技術において成果を得ている。

図1：研究開発項目の全体像

## 2. これまでの主な成果

## (a) 量子制御アーキテクチャ

図2に示す低コスト量子ビット回路アーキテクチャを提案し、従来よりも大幅に簡素な素子で十分なゲート忠実度を実現可能なことを明らかにした。加えて、得られた知見を基にデザインガイドラインの構築を進めた。

図2：提案アーキテクチャの概要

## (b) 光集積回路の低温特性測定

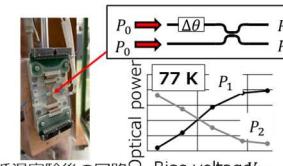

液体窒素中に光集積回路を入れ、その動作測定を測定した。室温動作時と同様のスイッチング特性を確認した(図3)。液体ヘリウム環境下での光集積回路の特性評価環境を構築した。

図3：液体窒素中での光スイッチ特性

## (c) Cryo CMOS 向け PDK

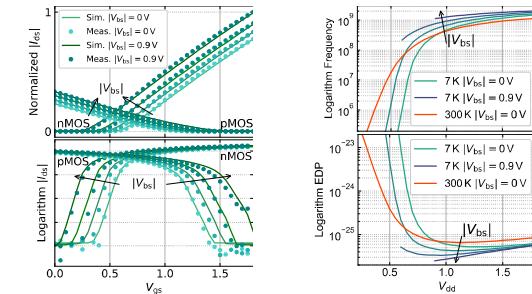

昨年度行った機械学習ベースのモデル化手法に加えて、業界標準モデル化手法および表面電位に基づくモデリング手法を開発した。業界標準モデルについては広く採用されているBSIM4を対象として電流の基板バイアス依存性をモデル化した(図4左)。リング発振器設計に応用し、試作することなく、基板バイアス印加と電圧スケーリングにより電力最適化設計ができるることを実証した(図4右)。

図4：電流特性模擬（左）とリング発振器への応用（右）

## (d) Cryo 集積回路の設計技術

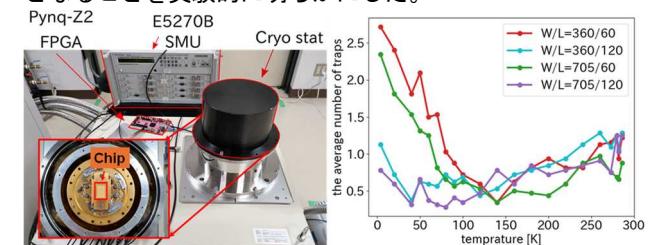

極低温環境におけるCMOS回路の信頼性向上に向け、極低温動作可能な測定環境(クライオスタート、FPGA制御基板等)を構築するとともに、これを用いてトランジスタのランダムテレグラフ雑音(RTN)特性の統計的解析を行った(図5)。極低温領域ではRTNの影響が100K付近で一時に緩和される一方で、3.8Kといった極低温ではむしろ顕著となることを実験的に明らかにした。

図5：極低温におけるRTN

## 3. 今後の展開

各要素技術の統合を積極的に検討し、提案システムの実証およびスケーラビリティ見積もりを狙う。

## 4. フロントエンド・バックエンドのCryo CMOS化

### 2024年度までの進捗状況

#### 1. 概要

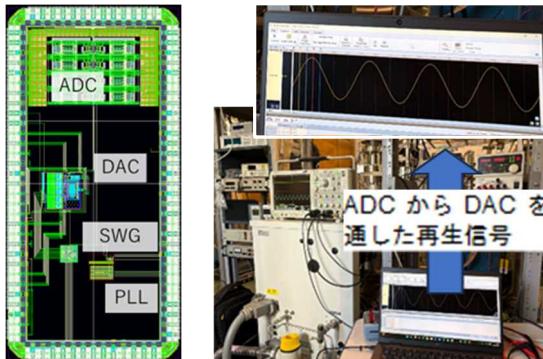

本研究開発項目では、スケーラブルなシステム構築のためのデバイス開発を目標に、Cryo(極低温4K)で安定動作可能なASIC(アプリケーション専用集積回路)やSoC(システムオンチップ)の開発を行う。課題1のデジタル回路(Sine Wave Generator)、課題2のPLL(Phase-Locked Loop)、課題3のDAC、課題4のADCの4つの回路ブロックを集積したSoC(System on a Chip)を試作し、その極低温での正常動作を確認した(図1)。ただし、DACの極低温での性能に問題があり、2025年度に試作を行う予定である。

図1 試作SoCのレイアウトとCryo(4.2K)での測定結果

#### 2. これまでの主な成果

項目1、4、5では、項目2よりすでにFPGA上に実装済のデジタル信号処理プロセッサ(DSP)のRTL(Register Transfer Level)をASIC向けに改変することで22nmバブルCMOSプロセスを用いてASIC化した。設計手法の問題から正常動作とはならなかつたが、得られた知見をもとに4K

で動作するSRAMマクロを設計し、それを使って一部演算をビット幅の小さい浮動小数点化した第2版を設計中である。Cryoで疑似SRAMとして利用可能なGCDRAMを試作し、Cryoではmsオーダーの保持時間となることを実測により確認した。

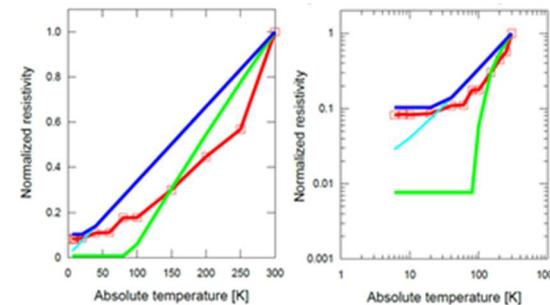

項目2では、CryoにおけるRF(高周波)フロントエンド回路実現に向け、デバイスマodel化および要素回路の設計評価を継続して実施した。デバイスマodel化については2023年度に提案した配線抵抗モデルを実測で確認・改良し、実用性の高いモデルの提案を行った。図2に実測結果とモデルの比較の一例を示す。提案モデルは従来のモデルよりも高い精度を達成したが、4K付近ではなお誤差が生じることが分かった。RF要素回路についてはクロック生成PLLを設計し、4Kでの動作を実測で確認した。また、RF信号源およびミキサ回路を22nm CMOSプロセスにて設計した。

図2 各種配線の抵抗率の温度依存性実測結果

—:実測結果 ■:従来(PDK) —:改良モデル —:2023年モデル

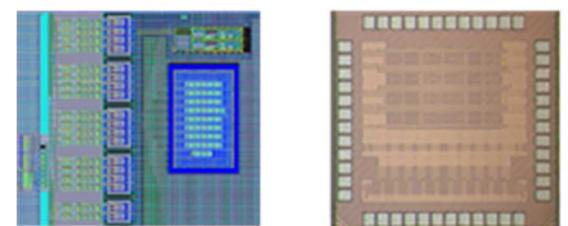

項目3では22nm CMOSプロセスで設計したDAC(12bit、2Gsps、右列にレイアウト 図3a)を常温及び4Kで測定した。測定の結果、DACの線形性の悪さから有効bit数(ENOB)が6bitと想定の性能を出せなかつたが、

4Kでの測定環境の構築など次につながる環境構築ができ、次回の試作への改善点も明らかになった。また、ベイズ最適化を用いて8bitユナリ型DACの自動設計を実現した。8bitDACの回路規模で実行時間が6時間以下であることから、12bitDACへ拡張した場合の実行時間の問題が今後の課題として明らかになった。課題4では、Cryoで動作する性能スケーラブルな高速ADCを実現するために、22nmバブルCMOSプロセスを用いて、8チャネルタイムインターリーブで動作するADCを設計した。また、タイムインターリーブ動作時に課題となるチャネル間ミスマッチ補正回路を設計し、これらのテストチップを作成した(図3b)。作成したADCは常温及び液体ヘリウム(4.2K)環境下で正常動作が確認され、分解能10bit、サンプリングレート2GS/sのADCの開発に成功した。

(a) 12bit DAC レイアウト (b) 8ch ADC チップ

図3 試作チップの画像

#### 3. 今後の展開

次年度はデジタル部、DAC、ADC、RF-PLLを統合したSoCの改良版を試作する。試作したSoCは高エネルギー加速器研究機構だけではなく、京都工芸繊維大学に設置予定のライオスタッフでも測定を行う。デジタル部、ADC、DAC、RF各部で2025年以降に向けた要素回路の設計と試作も行う。デジタル部ではGCDRAMのメモリアレイを試作し、マクロとしての動作を確認するとともにそれを組み込んだデジタル回路を設計するための高位合成系の実装も行う。

## 5. 常温で動作するフロントエンドアナログ RF 部の LSI 化

### 2024年度までの進捗状況

#### 1. 概要

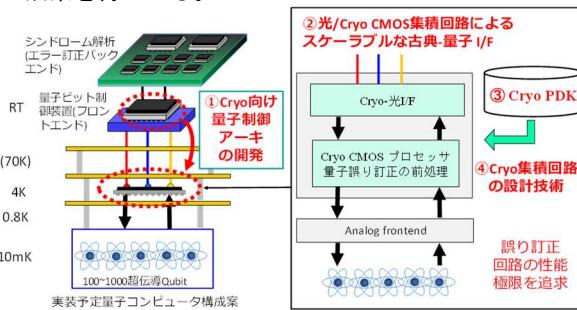

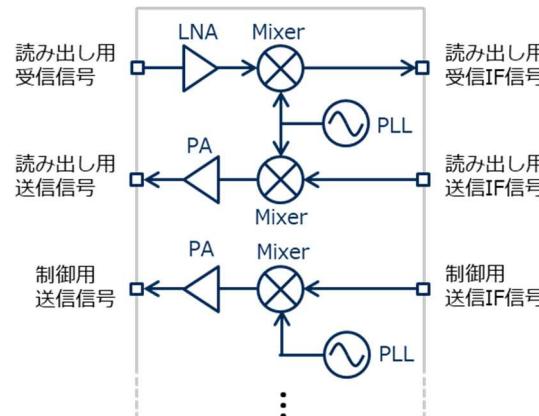

現状の常温環境に置かれた量子ビット制御装置において、マイクロ波制御信号を送受信するフロントエンドアナログ RF 部(図1)は、高周波特性やノイズ性能に優れた化合物半導体デバイスや bipolar デバイス、多くのディスクリート部品で構成され、実装サイズが大きく、消費電力が大きい。今後、量子ビット数を増やしていくためには、フロントエンドアナログ RF 部の実装サイズおよび消費電力を飛躍的に削減する必要がある。そこで本研究開発項目では、フロントエンドアナログ RF 部の主要な機能ブロックである PLL(Phase Locked Loop)回路と送受信回路について、常温環境での使用を想定し、微細 CMOS デバイスでの設計を行い、小型化及び省電力化を目指す。さらに集積化で課題となる送受信間のアイソレーションの向上にチャレンジする。

#### 2. これまでの主な成果

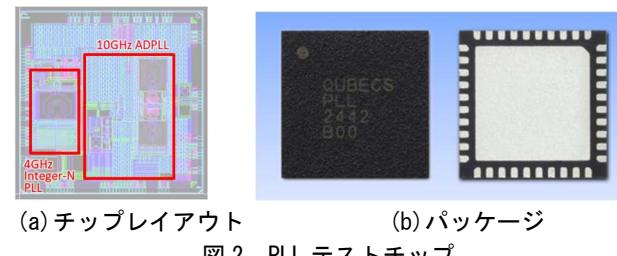

PLL 回路の低消費電力化、低ノイズ化の取り組みとして、PLL 比較周波数を 1GHz に設定し PLL 帯域を広くすることで、PLL 帯域内ノイズ化の低減を図った。その 1GHz の信号は簡素な Integer-N PLL で生成する構成とした。さらに、微細 CMOS プロセスを活かして、比較周波数 1GHz で動作するデジタルリッチな ADPLL (All Digital PLL) を設計した。PLL テストチップ(図2)を試作し、性能評価した結果、出力周波数 10GHz 時の PLL 帯域内位相ノイズは -105dBc/Hz であり、既存の量子ビット制御装置に搭載されている PLL に近いノイズ性能を得た。さらに、量子ビット制御装置で重要な長期の位相揺らぎについては、ルビジウム発振器を基準とした測定系で、測定時間 1,000 秒、測定時間分解能 40 ミリ秒の時間軸測定において、ADPLL 単体で 0.12 度 rms を確認した。本開発の PLL の消費電力は、既存の量子ビット制御装置搭載の PLL より約 80% 低減を図った。

受信回路の低ノイズ化の取り組みとして、10GHz 帯 CMOS LNA (Low Noise Amplifier) の回路構成をノイズキャンセル抑圧構成とした。LNA には高周波で信号損失を最小化する種々のレイアウト技術を用いたトランジスタを新たに開発した。送信回路は、PA (Power Amplifier) から受信回路への信号リークを抑圧するために、PA 回路の負荷に磁気リーク

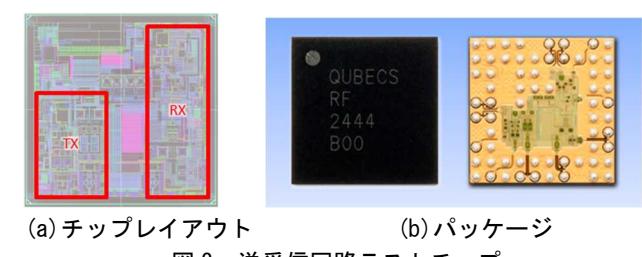

を抑えるクローバ型のトランジスタを開発した。さらに、送受信回路間アイソレーションの向上を目的として、LNA と PA に完全差動回路構成を採用した。こうした取り組みの有効性を実証する送受信回路テストチップ(図3)を 22nm SOI (Silicon On Insulator) CMOS で試作し、高周波特性の優れる FOWLP (Fan Out Wafer Level Package) に封止し、常温にて性能評価を実施した。10GHz 帯 CMOS LNA の NF (Noise Figure) は ESD (Electro-Static Discharge) 耐性を有しながら約 2.5dB を達成し、CMOS LNA として業界トップレベルの NF を確認した。本開発の LNA の NF 特性は、シミュレーション結果と実測値の比較的良好な一致を示した。また、PA の送信出力は、微細 CMOS プロセスにおける低電圧動作においても既存の量子ビット制御装置と同等の 10dBm 以上を実現した。さらに、送受信間アイソレーションは、送信回路と受信回路を同一チップに集積しながら、目標値である 70dB 以上を達成した。本開発の送信回路と受信回路の消費電力は、既存の量子ビット制御装置の 1/10 程度を実現した。

#### 3. 今後の展開

今後は、テストチップの性能評価を完了させ、評価結果から課題抽出を行い、実現性を踏まえたフロントエンドアナログ RF 部の統合化の設計指針の確立を目指す。