# 実施状況報告書

2024 年度版

大規模集積シリコン量子コンピュータの

研究開発

# 水野 弘之

株式会社日立製作所 研究開発グループ

#### 1. 当該年度における研究開発プロジェクトの実施概要

# (1) 研究開発プロジェクトの概要

本研究開発プロジェクトでは、シリコン電子スピン量子ビットを用いた量子コンピュータの開発、特にシリコン半導体の回路集積化技術を活かした大規模集積シリコン量子コンピュータの開発を行う。研究開発項目1"量子コンピューティングシステム"では、量子ビットアレイ、制御回路の構造設計、回路仕様の策定を行うとともに、試作に着手して量子ビット特性を評価する。研究開発項目2"極低温複数チップ実装システム"では、量子ビットの読み出し機構の構築に不可欠な高分解能アナログ・デジタル変換回路の設計・評価、および、極低温環境モニタリングシステム構成とシミュレーション評価を行う。研究開発項目3"ホットシリコン量子ビット"では、ホットシリコン評価1に向け、提案する量子ビットアレイ構造の一部を用いた「小規模な実験回路」の先行開発を行い、課題の早期抽出を通じ評価環境の立上げを行う。また、研究開発項目4"小規模回路による量子演算"では「小規模な実験回路」を用いた基本量子ビット操作の先行評価を行い、検討結果を本開発プロジェクトで進めるシリコン2次元量子ビット構造設計に反映させることで、開発の高効率化を図る。

### (2) 研究開発プロジェクトの実施状況

研究開発項目1では、2次元量子ビットアレイについて、アレイ構造の試作・評価を通じ、 1量子ビットのスピン操作の実証実験を行った。昨年度までに実施した大規模量子ビット アレイ、制御回路の設計・試作、および、希釈冷凍機の導入、量子ビット制御・測定エレク トロニクスを用いて各課題推進者による試作素子の評価・解析を実施した。スピン操作に おいて、コヒーレンスをさらに改善させるスピン操作シーケンスについて検討した。スピン 量子ビットにおいて、外界からのノイズを削減し、コヒーレンス時間を延伸させる量子ビット 操作技術(CCD:Concatenated Continuous Driving)を開発した。ランダマイズドベ ンチマークを用いたゲート操作忠実度は、従来のスピン操作方法で95±1%であったの に対し、開発したスピン操作技術CCD適用下では99.1±0.1%となり、CCDによりゲ ート忠実度を大幅に改善したことを確認した。量子ビット操作の実証実験に着手し、2量 子ビットのエンタングル状態を反映したCROT(Controlled Rotation)スペクトルを観 測するとともに、CROTによる2量子ビット操作に成功し、当該年度のマイルストーンを達 成した。前年度までに開発した極低温制御チップの改良に向けて、量子ビットの更なる高 精度制御を目的に、位相低減方式であるポーラー変調方式を適用したマイクロ波発生回 路チップの詳細設計を完了した。ポーラー変調方式においては、振幅変調を間欠動作さ せることで電力効率を改善し、位相変調用のLO(局部発振器)ブロックにはサンプリングP LL(位相同期ループ)方式を採用し位相低減を図った。検討の結果、位相誤差成分であ るジッタを137fsecから80fsecに低減できる見込みを得た。前年度設計したもう一つの 制御チップであるブリッジチップにおいては、チップ設計・試作を完了し、量子ビットチッ プと組み合わせたシステム評価を開始した。このブリッジチップと量子ビットチップを接続 しQBAのチャージスタビリティダイアグラムパターンを取得し良好なハニカムパターンを 確認した。これまで開発してきた量子オペレーティングシステムの拡張を進めるとともに、 量子デバイス実験者に対して実験を効率化するためのワンクリック量子ビット測定システ ムの構築を完了した。さらに、シリコン量子ビットでFTQC(誤り耐性量子コンピュータ)シス

テムの実現に向けて、システム設計に寄与するシミュレーション環境の構築と量子誤り訂 正アーキテクチャの検討を行った。

研究開発項目2では、極低温複数チップ実装システムにおける量子ビットアレイチップの制御および環境モニタリング機能を統合した極低温インタフェース機構の構築に向けて、100mK温度で動作可能な極低温アナログ回路のアーキテクチャ開発を進めるとともに、テストチップを用いた極低温動作検証を実施した。低消費電力を維持しながら広帯域動作を実現するAD変換回路および極低温下で信号の選択・分配を行うスイッチ回路を開発し、64量子ビット以上の制御を可能とする回路要素の基盤を構築した。また、極低温マルチチップパッケージングを発展させ、シリコン貫通ビアを活用した排熱機構を有するチップパッケージング技術を開発し、その製造プロセス開発および極低温耐性評価を実施した。さらに、環境モニタリングシステムの構築に向けて、量子ビット近傍においてパルス信号波形を生成・取得する機構を開発し、取得した波形データに基づいてパルス信号波形を生成・取得する機構を開発し、取得した波形データに基づいてパルス信号波形を生成・取得する機構を開発し、取得した波形データに基づいてパルス信号波形を生成・取得する機構を開発し、取得した波形データに基づいてパルス信号波形を生成・取得する機構を開発し、取得した波形データに基づいてパルス信号波形を生成・取得する機構を開発し、取得した波形データに基づいてパルス信号波形を生成・取得する機構を開発し、取得した波形データに基づいてパルス信号波形を生成・取得する

研究開発項目3では、量子ビットアレイ構造の一部を用いた「小規模な実験回路」に加えて、新たに提案、設計し研究開発項目1で作製した量子ドットデバイスを用いて実験を遂行した。これらの実験を基に、シリコン量子ビットの~1Kでの高温動作を達成した。加えて、令和7年度目標の電子スピン系とホールスピン系のベンチマークに先立ち、電子スピンとホールスピンの性能比較可能なデバイス構造の基礎的な評価を行った。さらに、インターポーザ(中間基板)上に集積された複数のシリコン量子ビットデバイスの評価に向け、複数量子ビット読み出しに適した読み出し回路の評価を行った。

研究開発項目4では、シリコン量子ビットを効率的に演算させるための手法の開発、シリコン量子ビットによる量子演算実現に向けた課題の早期抽出を目的とし、初期化、読み出し、ビット操作、ビット結合性などの基本操作を効果的に組み込むことのできる量子ビットアレイ構造および制御方法の探索に取り組んでいる。当該年度はなかでも、量子ビットアレイ構造の一部を構成する基本的な「小規模実験回路」等を活用して、読み出し、初期化に関する方式の検証に取り組んだ。また、量子デバイスの非断続的な安定化に向けた取り組みを開始した。得られた知見を、研究開発課題1"2次元量子ビットアレイ"で進める2次元量子ビットアレイ構造に反映し、小規模量子回路の実装と、さらなる大規模化に向けた課題の抽出に取り組んだ。

## (3) プロジェクトマネジメントの実施状況

本プロジェクトでのマネジメント体制、各種マネジメントに係る会議運営、国際連携、および、アウトリーチ活動は、代表機関主導により体制を構築、実運用を実施しており、プロジェクトマネジメントも順調に推進している。昨年度に引き続き、代表機関の産学連携部門、広報部門、知財担当部門等の本プロジェクトの運営に必要となるアシスタントスタッフも含むPM支援体制チームでプロジェクト推進を行った。グローバル連携として、日立ケンブリッジ研究所に加えてInteruniversity Microelectronics Centre (imec) との国際連携体制を強化した。

当該年度は、広報活動の一環として、米メタ社のInstagram、当プロジェクトのホームページおよび新たに開設したYouTubeチャンネルを活用した情報発信を推進した。

#### 2. 当該年度の研究開発プロジェクトの実施内容

#### (1) 研究開発項目1:量子コンピューティングシステム

研究開発課題1:2次元量子ビットアレイ

当該年度実施内容:本研究開発課題では、2次元量子ビットアレイについて、アレイ構造の試作・評価を通じ、1量子ビットのスピン操作の実証実験を行った。「小規模な実験回路」を用い、量子ビットに電子スピンを回転させるために必要となるマイクロ波を照射することで、明瞭なラビ振動を確認した。1量子ビットの2軸回転操作の実証を行った。2軸操作は、印加するマイクロ波のπ/2パルスを位相を制御しながら2段階に照射することで行う。2段階に照射したマイクロ波の位相依存性を取得したところ、期待通りスピン反転確率の位相依存性が周期2πのcos関数となっていることを確認した。以上の結果により、電子スピンの2軸操作が可能であることを実証した。

続いて、スピン操作において、コヒーレンスをさらに改善させるスピ ン操作シーケンスについて検討した。スピン量子ビットにおいて、外 界からのノイズを削減し、コヒーレンス時間を延伸させる量子ビット操 作技術(CCD:Concatenated Continuous Driving)を開発し た。具体的には、スピン操作時に印加するマイクロ波の位相変調を利 用し、X, Y, Z 軸の3軸、360°全方向で電子スピンをノイズから保護 しながらスピン操作を行う。試作した量子ビットアレイに開発したスピ ン操作を適用した結果、コヒーレンス時間が100倍以上(1.2 $\mu$ 秒→ 211 μ 秒)と劇的に改善することを実験的に確認した。本成果は、半 導体デバイス・回路の国際会議で権威のあるVLSI Symposium 2024にて発表するとともに、日立製作所よりニュースリリースを行った (https://www.hitachi.co.jp/New/cnews/month/2024/06/0617.html "日立、量子コンピュータの実用化に向けて量子ビットの寿命を100 倍以上長く安定化させる操作技術を開発")。なお、今回の結果は、 安定同位体が混合した天然シリコンを用いて試作した量子ビットアレ イに適用した結果である。シリコン29による磁気ノイズを排除すること が可能となる同位体制御シリコンを用いることで、コヒーレンス時間の さらなる延伸が期待される。同位体制御シリコンを適用した量子ビット アレイは、現在imecにて試作中であり、今後、適用効果を確認する 予定である。

次に、操作忠実度の評価を実施した。ゲート忠実度の評価にはランダマイズドベンチマークを用いた。評価した結果、ゲート操作忠実度は、従来のスピン操作方法で95±1%であったのに対し、開発したスピン操作技術CCD適用下では99.1±0.1%となり、CCDによりゲート忠実度を大幅に改善したことを確認した。この結果は天然シリコンを用いたデバイスであっても表面符号誤り訂正に必要な臨界閾値99%に達しており、CCDの有効性を大きく示すものと言える。以上の一連の結果により、1量子ビット操作技術立ち上げは完了し、当該

年度のマイルストーンであった"2次元量子ビットアレイ構造にて、スピン操作シーケンスの仕様策定"を達成した。

1量子ビット操作技術立ち上げ完了を受け、2量子ビット操作の実証実験に着手した。なお、評価にはimecで試作したチップを用いた。 隣接した2量子ドットにおいてそれぞれスピン共鳴を確認しラビ振動を取得できることを確認した。2量子ビット操作方式としてCROT方式を採用し、評価行った結果、2量子ビットのエンタングル状態を反映したスペクトルを観測するとともに、CROTによる2量子ビット操作に成功し、当該年度のマイルストーンを達成した。

本研究は、東京科学大、理研と密接に連携して進められたものである。また、技術内容に関しては、海外連携先の日立ケンブリッジ研究所とも密に議論し検討を進めた。来年度以降も、継続して密接に連携して研究を推進し、目標達成をめざす。

最後に、量子ビットアレイの試作に関する取り組んだ結果について 示す。大規模量子ビットアレイ動作の実証に向け、令和5年度より、i mecと共同研究契約を締結し、試作を開始した(Hitachi-imec Ta ndem PJと呼ぶ)。直径300mmのSi基板 に対応した世界最先端の imecの試作クリーンルームを活用し、大規模量子ビットアレイ試作ス キーム構築を目指す。当該年度は、本PJの5年目のマイルストーン実 証に必要となる4×4以上の2次元量子ドットアレイが集積された量子 ビットアレイチップを設計するとともに、マルチフィジックス物理シミュレ ータ(COMSOL)を用いて、3次元アレイ構造を構築し、基本量子ビ ットアレイの動作の検証を行った。その結果、アレイ上に配置した制 御ゲートに電圧を印加し、形成するポテンシャルを高精度に制御する ことで、任意の位置で2量子ビット操作可能となるポテンシャルプロフ ァイルを実現できる見通しを得た。設計したアレイはimecにて試作を 実施した。imecとは、密接な連携体制を構築して試作を進めた結 果、量子ビットアレイチップは、当該年度中に完成させることができ、 基礎評価を開始した。来年度は、継続して詳細評価実験を実施し、 マイルトーン達成を目指す。

課題推進者:水野 弘之(日立製作所)

研究開発課題2:量子ビット高精度制御・高感度読み出し回路

当該年度実施内容:(A)極低温制御チップ(CAC)の開発

前年度までに開発したCAC-2の改良に向けて、量子ビットの更なる高精度制御を目的に、位相低減方式であるポーラー変調方式を適用したマイクロ波発生回路チップの詳細設計を完了した。ポーラー変調方式においては、振幅変調を間欠動作させることで電力効率を改善し、位相変調用のLOブロックにはサンプリングPLL方式を採用し位相低減を図った。検討の結果、位相誤差成分であるジッタを1

37fsecから80fsecに低減できる見込みを得た。また、マイクロ波発 生回路の低雑音化のため電圧制御発信器(VCO)方式をこれまで の20GHz直接発振型から周波数2逓倍方式とした。さらに同相モー ド容量と差動モード容量の比、及びインダクタ間の結合係数を最適 化することにより、同相モード共振インピーダンスを増加させ、位相雑 音を改善する同相成分最適化技術を考案した。考案内容を詳細設 計し、その試作チップ(CTEG3)を極低温雰囲気において評価した ところ、発振周波数レンジ8.9GHzから11.2GHzの広範囲な条件 においてVCO位相雑音は -123.1dBc/Hzから -121.4dBc /Hzと2.7dBに抑えることができた。本成果を、半導体デバイス・回 路の主要な国際会議であるESSERC 2024にて発表した。このV CO発振器を適用した前述のポーラー変調方式のマイクロ波発生回 路に組み込むことで、RFジッタ <131fsec(RFフィデリティ99.9 7%)を達成見込み、製作完了した CTEG4チップを評価基板に組み 込み現在極低温雰囲気にて評価中である。また、RFフィデリティ99. 99%化、すなわちRFジッタ<78fs実現に向けてデジタル入力で位 相変化させるDigital Time Converter方式を導入し、変調信号 起因の位相誤差キャンセルによる位相誤差低減技術の改良と発振 器の低雑音化を検討予定である。

#### (B) 量子ビットアレイチップ (QBA) の開発

前年度設計したもう一つの制御チップであるブリッジチップにおいて は、チップ設計・試作を完了し、量子ビットチップと組み合わせたシス テム評価を開始した。階層アーキテクチャを構築するために、ブリッ ジチップにはCACチップからの量子ビット制御コマンドを受けるシリ アルパラレルインターフェース(SPI)通信機能、量子ビット素子に印 加するバイアス電圧選択・切り替え機能、量子ビット素子からの出力 電流やチップ内の温度を計測する機能、複数の計測回路を制御す るためのトリガ信号生成機能の4つの機能を搭載した。このブリッジチ ップと量子ビットチップを接続しQBAのチャージスタビリティダイアグ ラムパターンを取得し良好なハニカムパターンを確認した。 今後は量 子ビット操作の一つであるシャトリング(量子ドットアレイ中の電子移 動)操作の評価を予定している。また、スケーラブルな量子ビット構造 とその操作方法の検討の過程で、シャトリング操作には正弦波と位相 制御の二つの機能が必要と分かった。そこで量子ビットチップ近傍に 配置するブリッジチップに、高精度シャトリング操作を可能とする信号 生成回路を搭載する時定数制御方式を考案した。時定数を制御す る方法としては、コンデンサ素子を駆動経路に追加し、量子ビット素 子のゲート充放電時間を調整する。本手法の効果をシミュレーション にて確認し、従来方式と同等なフィディリティ(>99.9%)が得られる 見込みを得た。高精度読出しについては、前年度までに反射方式と 電流方式を組み合わせたハイブリッド方式の効果をシミュレーションにより確認した。本年度はそれぞれの要素技術の評価を進めた。反射方式を用いてQBAのチャージスタビリティダイアグラムを取得、電流方式は試作チップ評価にてDCゲイン~15 MV/A (1 nAを 15 mV に増幅)を確認した。事前のシミュレーションによるゲイン値と同等の結果が得られ、所望の動作を確認できた。最終年度は各要素方式の読出し高速化の実証や、ハイブリッド方式の代案検討を進める予定である。以上の一連の結果により、当該年度のマイルストーンであった"量子ビット高精度制御・高感度読み出し回路によるシステム設計"を達成した。

課題推進者:水野 弘之(日立製作所)

# 研究開発課題3:システムアーキテクチャ

当該年度実施内容:本研究開発課題では、これまで開発してきた量子オペレーティングシステムの拡張を進めるとともに、実験を効率化するためのワンクリック量子ビット測定システムの構築を完了した。さらに、シリコン量子ビットによるFTQCシステムの実現に向けて、システム設計に寄与するシミュレーション環境の構築と量子誤り訂正アーキテクチャの検討を行った。以下に本年度の進捗状況の詳細を(A)量子オペレーティングシステム、(B)シリコン量子ビットシミュレーション環境、(C)シリコン量子誤り訂正アーキテクチャの3項目に分けて説明する。

#### (A) 量子オペレーティングシステム

実験者支援のための量子オペレーティングシステムの拡張と、1 量子ビ ットのラビ振動測定を自動化するワンクリック量子ビット測定システムを 開発した。量子オペレーティングシステムの拡張においては、実験のた めのソフトウェアフレームワークおよびデータ管理系を設計し、さらに実 験および測定器ライブラリを実装した。ワンクリック量子ビット測定システ ムでは、分析処理の自動化手法を応用し、自動校正ライブラリの実装を 完了した。天然シリコンデバイスを用いた実証試験の結果、自動校正に よって測定時間を81%削減できることを確認するとともに、動作状態の トレーサビリティの確保と温度・デバイス特性変動時に対する自動校正 機能を確認した。さらに、複数のゲートの動作条件を自動最適化しなが らスピン共鳴周波数を計測することで、ゲート電圧変化に伴うスピン共 鳴周波数変化、すなわちシュタルクシフトの観測を確認した。また、本測 定システムの成果を基に、今後シリコン量子コンピュータをクラウド公開 することを想定したシステム化を想定し、入出力データを自動保存する 実験履歴管理機能と、実験の関係性をグラフ形式で俯瞰・管理すること で実験プロセスを資産化・再利用する機能の実装を完了した。さらに、 実機提供と相補的な役割を果たす、デバイスと連携したシミュレーション であるデジタルツインのプロトタイプを実装し、正常に動作することを確 認した。

(B)シリコン量子ビットシミュレーション環境

シリコン量子ビットを用いたFTQCシステムの研究加速に向けて、今年度からシリコン量子ビット操作の確立とシステムアーキテクチャの設計を目的とした、デバイス・回路・論理レベルの3階層から成るシミュレーション環境の構築を開始した。

デバイスシミュレーションでは、マルチフィジックスシミュレータCOMSO Lによる3次元アレイ構造のシミュレーション環境の構築を完了した。スケーラブルな2次元量子ビットアレイにおいて量子ビット操作を行うためには、各々縦・横方向に配置された 2 量子ビット間の結合を、ゲート電極への電圧印加によって制御する必要がある。シミュレーションの解析を行った結果、ポテンシャルを高精度に制御することで、2次元に配列された任意の縦・横の2量子ビットにおいてビット間結合を制御し、量子ビット操作が行えることを確認した。

シリコン量子ビットで量子誤り訂正を実現するには、大規模化と高フィデリティ化を両立するシャトリング技術の開発が必要となる。そこで、従来のアナログ制御に対して、簡易な回路構成で実装可能な矩形波(デジタル)近似によるデジタルシャトリング制御方式を提案した。本方式をスイッチマトリックス回路で実装し、実装時に想定される時定数や電圧ばらつきも含めた制御波形を回路モデルシミュレーションで生成した。本制御波形を用いたシャトリング操作に伴い発生するバレー分離励起に起因するリークエラー率を、物理モデルで評価した結果、従来技術である正弦波に位相変調を施した高精度アナログ波形と同等のフィデリティ性能が得られることを確認した。

論理レベルシミュレータは、表面符号を用いた量子誤り訂正エラー評価からシステム仕様策定に寄与することを目的に開発を開始した。従来の表面符号シミュレータでは理想的なノイズモデルを扱うものに限られていたが、本シミュレータでは各ゲート処理のフィデリティや想定されるエラー率など、個々のデバイス特性も考慮した形で誤り訂正を実行する。今年度は個別にノイズモデルを追加する機能と論理エラーの可視化機能の実装を完了し、表面符号において論理演算の順序を変えることで生じるHookエラーの影響解析を完了した。

#### (C)シリコン量子誤り訂正アーキテクチャ

シリコン量子ビットにおける表面符号の実装には、T2緩和時間内で誤り 訂正に必要な処理を行うための時間的制約に加え、量子ビットの制御 に必要な配線をレイアウトするための空間的制約を満たす必要がある。 本課題を解決する手段として、シャトリング操作を活用した量子誤り訂正 アーキテクチャの検討が報告されている。量子ビットを2次元に疎配置し た構造について配線レイアウトを検討し、制御配線の本数とシャトリング 速度の関係から、既存の回路実装技術で実現可能な物理量子ビット数 を見積もった。さらに、表面符号を擬似2次元構造で表現した量子誤り 訂正アーキテクチャについても同様の解析を実施した結果、量子ビット を2次元に疎配置した構造と比較して、必要なシャトリング速度の条件が 緩和されることを確認した。

課題推進者:水野 弘之(日立製作所)

(2) 研究開発項目2: 極低温複数チップ実装システム

研究開発課題4:極低温複数チップ実装

① 極低温制御チップおよび環境モニタリングチップに搭載する極低温アナログ回路の開発

当該年度実施内容:

令和6年度は、64量子ビット以上の制御を可能にする極低温アナログインタフェースの構築に向けて、極低温複数チップ実装システムにおける量子ビットアレイチップの制御および環境モニタリングを実現する極低温アナログ要素回路の開発と、その極低温評価を実施した。

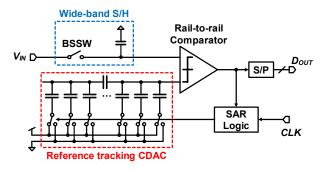

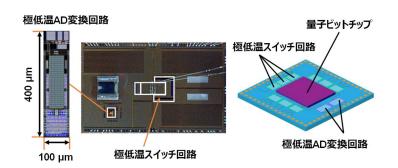

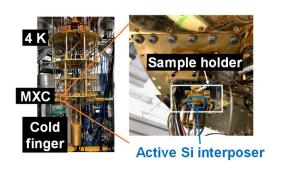

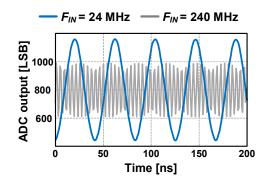

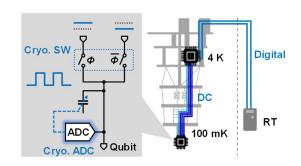

令和5年度までに開発した4Kで動作するAD/DA変換回路技術 を基に、本年度はより量子ビットに近い100mK領域での制御信号 生成と観測を可能にする極低温スイッチ回路と極低温AD変換回路を 開発した。100mKで動作する極低温アナログ回路は、より厳しい 消費電力制約が課せられるため、本研究では定常電流を消費するバッ ファ回路を排除した逐次比較型AD変換アーキテクチャを考案した (図1)。このアーキテクチャでは、バッファ回路を含まずに広帯域特 性を確保するため、二分探索動作のための容量型DAC(CDAC) を入力信号経路から切り離し、比較器のリファレンスノードに接続す る方式を採用した。これにより、入力信号経路には独立したサンプリ ング容量を配置可能となり、極低温下における低熱雑音・低リーク特 性を活かして入力容量の最小化を図ることができる。一方、リファレ ンス電圧を二分探索電圧として利用することにより入力レンジが縮小 する課題に対しては、比較器をレール・ツー・レール動作とすること で対応した。本AD変換回路を180nmプロセスで設計し、チップ 試作を行った(図2)。本チップは量子ビットチップをフリップチップ 実装するためのアクティブインターポーザーとして用いることを想定 しており、極低温スイッチ回路も統合している。極低温スイッチ回路 は複数信号を選択するセレクタ機能とともに、入力電圧を保持して分 配する機能を有する。これにより、制御信号本数を抑えながら64量 子ビット以上のバイアス電圧制御を可能としている。本試作チップを 希釈冷凍機のプレート(図3中MXC)に搭載し、100mK以下の 温度に冷却して動作実験を行った。図4は外部から正弦波信号を入力 した際のAD変換結果を示しており、AD変換回路が100mKで正 常に動作することを確認した。また、動作時の消費電力は、約30μ

Wであり、100mKステージの冷却能力に対して十分に低く抑えられている。これは、本回路が定常電流を排除したダイナミック動作のみの構成であるため、動作周波数を下げることで消費電力を抑制できるためである。なお、低い動作周波数で広帯域信号を取得する手法として等価サンプリング手法を用いている。

本成果により、量子ビット読出しや環境モニタリングへの応用が可能なAD変換回路について、量子ビット近傍での動作の可能性を示すとともに、100mK以下という極低温環境における超低消費電力動作を実現する回路設計基盤技術を確立した。なお、本成果は国際学会ASSCC 2024にて口頭発表を行った。

図1 極低温AD変換回路アーキテクチャ

図2 極低温アナログ回路の試作チップ

図3 極低温評価セットアップ

図4 100mKでのAD変換動作結果

② 極低温マルチチップパッケージング技術の開発および製造法と設計法の確立 当該年度マイルストーン:極低温マルチチップパッケージングによる量子ビット チップとインタフェースチップの統合化設計と製造法

当該年度実施内容:令和6年度は、極低温マルチチップパッケージングを発展させ、 シリコン量子ビットチップと極低温制御回路および環境モニタリング チップを実装したマルチチップ構造デバイスの構築に加え、シリコン 貫通ビアを応用した排熱機構の検討および極低温環境下での評価を実 施した。

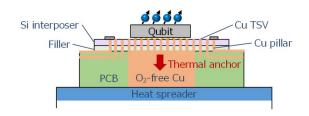

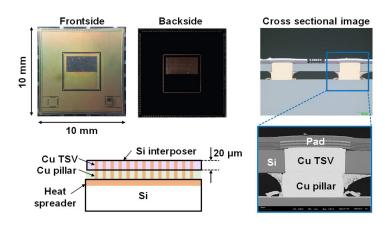

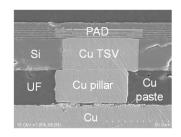

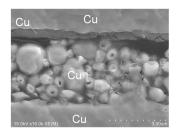

> シリコン量子ビット近傍に制御回路や環境モニタリング回路を集積 するマルチチップ構造では、回路動作時に発生する熱をいかに効率的 に排出するかが重要な課題となる。しかし、共通基板であるシリコン インターポーザは、極低温下で熱伝導率が低下するため、ヒートスプ レッダへの熱移動が制限される。そこで、図5に示すように、薄化した シリコンインターポーザに銅の貫通ビアを形成することで排熱経路を 確保する構造を検討した。薄化したシリコンインターポーザは、無酸 素銅プレートを有するPCB基板と接続され、チップ回路面で発生す る熱は銅貫通ビアを介して最短経路でヒートスプレッダへ放熱される 設計とした。銅貫通ビアと銅基板の接続には、銅ピラーによるCu-Cu接続を採用し、高い熱伝導経路を実現した。本チップパッケージ ング構造の製造プロセスおよび極低温耐性を評価するため、20μm に薄化したシリコンインターポーザに銅貫通ビアを形成し、20μm 厚の銅ピラーを介して銅基板と接合した積層チップパッケージを試作 した(図6)。断熱消磁冷凍機を用いて本チップに室温と極低温間の熱 サイクルを加えた後、断面観察により正常な接合が維持されているこ とを確認した。本成果は、IEEE ECTC2024にて口頭発表 を行った。次年度は、研究開発課題5の環境モニタリング技術を活用 し、パッケージ内部の温度モニタリングにより、本パッケージング構 造の排熱特性評価を実施する。

図5 排熱構造を有する複数チップパッケージング構造

図6 排熱チップパッケージング構造の試作

研究開発課題5:環境モニタリング手法

当該年度実施内容:令和6年度は、環境モニタリングシステムの構築に向けて、シリコン量子ビットの制御に用いるパルス信号のモニタリングおよびフィードバックシステムの構築とその極低温評価を実施した。

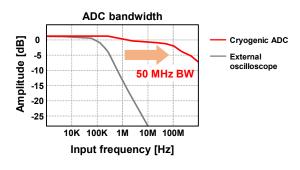

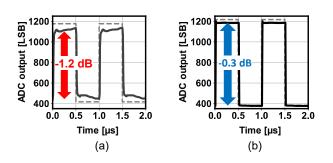

研究開発課題4-1で開発した極低温スイッチ回路と極低温AD変換 回路を用い、パルス信号波形の取得とフィードバック制御による波形 整形機能の検証を行った。図7に示すように、100mK領域におい て極低温スイッチから発生したパルス信号波形を、極低温AD変換回 路で取得し、その情報を基に、極低温スイッチ回路内に搭載した可変 容量をフィードバック制御する機構を開発した。量子ビット制御に必 要なパルス信号波形を高精度に観測するためには、広帯域での波形取 得が不可欠である。従来は、希釈冷凍機の外部に信号を引き出してオ シロスコープ等で観測していたが、長距離配線に伴う寄生成分の影響 により、広帯域な観測が困難であった。一方、本研究で開発した極低温 AD変換回路は、量子ビット近傍で直接波形を取得可能であり、研究 開発課題4-1で構築した広帯域設計技術により、約50MHzの広 帯域性能を確認した(図9)。本AD変換回路を用いて100mK領域 でパルス波形を取得した結果を図10に示す。図10(a)は外部から パルス信号を入力した結果であり、波形には寄生素子の影響による減 衰や変動が見られる。一方、図10(b)は希釈冷凍機内部の100m K領域で生成されたパルス信号の波形であり、高品質な波形が得られ ていることがわかる。このように得られた波形情報をもとに、パルス

波形を調整するフィードバック回路の構築を進めた。次年度は、多様なパルス波形を量子ビットに供給し、それぞれの波形と制御精度との相関を評価することで、量子ビットの高精度制御を実現するためのフィードバック制御手法の確立に取り組む。

図7 熱サイクル試験後の断面観察結果

図8 パルス制御信号のモニタリングシステム

図9 極低温AD変換回路の帯域特性

図10 取得したパルス波形 (a) 外部からパルス波を入力、(b) 100 mK 領域で波形を生成課題推進者: 永田 真 (神戸大学)

(3) 研究開発項目3: ホットシリコン量子ビット 研究開発課題6:シリコン量子ビットの高温動作 当該年度実施内容:

当該研究開発課題では、令和3年度から令和7年度にかけて、希釈冷凍機温度から温度制御を行って動作温度を徐々に高温化していくことで、量子ビット操作のフィデリティ向上に関する課題抽出、高温動作の評価・検証を行う。この計画に沿って、当該年度は、希釈冷凍機と量子ビット制御エレクトロニクスからなる極低温量子デバイス測定系を利用して、当該年度のマイルストーンであるシリコン量子ビットの高温(~1K)での動作を達成した。

高温( $\sim$ 1K)動作に向けて行った前年度のマイルストーンである300mK動作でのコヒーレントなスピン操作の実証を土台とし、900mKにおいてもホールスピンの電気双極子共鳴動作によるコヒーレントな時間発展を示唆する結果を得た。また、高温下での高忠実度動作に向けた技術開発も進めており、位相変調マイクロ波を用いることでスピン位相緩和時間( $T_2$ <sup>Rabi</sup>)を伸長させる効果を、ホールスピン系において初めて実証した。

翌年度のマイルストーンである電子スピン系とホールスピン系のベンチマークに向けて、新たに構築した測定システムを用いて、研究開発項目1で試作した、同一チップ上で電子スピンとホールスピンの性能比較可能なデバイス構造の測定を行った。電子系とホール系双方での量子ドット形成の確認や高周波反射位相測定の動作といった基礎的な評価と電荷ノイズ環境の比較を行った。その結果、同一チップかつ同一チャネル上に形成された量子ドットにおいて、電子系とホール系で電荷ノイズの大きさにほとんど差異がないことが明らかになった。この結果は、両極性キャリアのスピン特性を比較する上での前提となる。

極低温回路と量子ビットチップのインターポーザ接続について、研究開発項目2との連携のもと研究を推進した。量子ビットと周辺回路の接続問題を解決するための第一歩として、シリコンインターポーザ基板上に量子ドットチップと信号分岐を行うセレクタ回路を集積し、極低温下での電気特性を評価した。評価の結果、実装されたセレクタ回路を用いて、狙い通りの量子ドットを選択的に制御可能であることが示された。

課題推進者:小寺 哲夫(東京科学大学)

(4) 研究開発項目 4: 小規模回路による量子演算 研究開発課題 7:アレイ化と量子ビット基本演算の両立 当該年度実施内容:

(1) 小規模な実験回路を用いた量子ビット基本演算の方式検証 量子ビット基本演算のうち、とりわけ読み出し、初期化と、アレイ化 の両立においては、環境系(電子溜め)と隣接していない量子ビット に対する読み出し、初期化が重要である。その実行方式の主なものと して、量子ビットを物理的に移動するシャトリング輸送や、比較的大きな領域に閉じ込めた多電荷系の利用開拓などが挙げられる。前者のシャトリング輸送の活用に関しては、研究開発課題1と協力して、小規模実験回路で具体的な実証に取り組んだ。量子ビット列中のシャトリング輸送によって、環境系(電子溜め)と結合していない量子ビットの初期化、読み出しを実現し、2量子ビットの動作を実証できた。大規模化にむけてはさらなる高速化が望ましいが、同様の手法によって256量子ビット以上のアレイにおいて初期化、読み出しが可能であると見込んでいる。またシャトリングの高速化、高精度化にむけて、制御パルス条件と輸送電荷量の関係性等から、輸送精度に与える駆動周波数と断熱性の影響を調べた。一方で、多電荷系の利用開拓に関しては、研究開発課題6等と連携して多スピン系の物理開拓に取り組み、少数スピン系とは異なるコヒーレンスや、環境系(電子溜め)および電荷雑音との結合の影響について報告した。

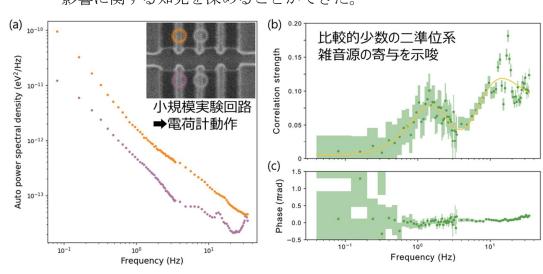

以上に加えて、アレイ化時に重要な課題の一つである量子ビット誤りの空間相関のさらなる検証として、量子ビット読み出し信号と量子ビット共鳴周波数とのゆらぎ相関を観測し、電荷雑音が誤り相関を引き起こすことのさらに直接的な実証を得た。この効果は同位体制御された量子ビットにおいてより顕著になることが見込まれる。また、量子ビット読み出しに用いる電荷計信号同士の雑音相互相関に着目して、雑音相関をより簡便、効率的に評価可能な手法を開拓した。さらには、デバイスへの制限を緩和した雑音相互相関の測定法を開発し、さまざまな条件下での雑音相互相関評価を実行した。以上の進展をうけて、新たに雑音の空間相関を利用した量子デバイスの非断続的な安定化実現に取り組むこととし、このための測定系の構築準備と、雑音相関に基づくフィードバック制御系の導入準備を行った。一連の取り組みで、量子ビットアレイでの基本演算およびシャトリング等の性能を制限する比較的疎な分布を持つ電荷雑音源とその影響に関する知見を深めることができた。

図11 電荷計信号同士の雑音相互相関評価 (a)小規模実験回路を電荷計動作させた際の電荷雑音の自己相関スペクトル。1/f タイプの雑音スペクトルが観測されている。 (b)電荷計信号同士の雑音の規格化された相互相関スペクトル。強い周波数依存性を示し、比較的少数の電荷雑音源が、相関雑音に支配的な影響を及ぼしていることが示唆された。

課題推進者:米田 淳(東京大学)

研究開発課題8:量子ビットの量子制御性の検証

当該年度実施内容:

(1) 小規模な実験回路を用いた量子ビット基本演算の方式策定

量子ビット基本演算のうち、とりわけ読み出し、初期化と、アレイ化の両立においては、リザバーと隣接していない量子ビットに対する読み出し、初期化が重要である。その実行方式の主なものとして、量子ビットを物理的に移動するシャトリング輸送や、比較的大きな領域に閉じ込めた多電荷系の利用開拓などが挙げられる。前者のシャトリング輸送の活用に関しては、研究開発課題7"小規模な実験回路を用いた量子ビット基本演算"と協力して、小規模実験回路で具体的な実証に取り組んだ。大規模化にむけてはさらなる高速化が望ましいが、同様の手法によって256量子ビット以上のアレイにおいて初期化、読み出しが可能であると見込んでいる。以上に加えて、アレイ化時に重要な課題の一つである量子ビット誤りの空間相関のさらなる検証として、量子ビット読み出し信号と量子ビット共鳴周波数とのゆらぎ相関を観測し、電荷雑音が誤り相関を引き起こすことのさらに直接的な実証を得た。この効果は同位体制御された量子ビットにおいてより顕著になることが見込まれる。

(2) 産業プロセスと量子ビット制御の適合性の検証

研究開発課題1"2次元量子ビットアレイ"と協力し、大規模化に適した産業用半導体プロセスに近い方法で製造した量子ビットの量子制御性を検証した。これまでの量子ビット制御実験の知見をもとに、産業プロセスによって多数の量子ビットを集積したデバイスにおける誤り訂正操作の実装方法の検討を実施した。また、研究開発課題4"極低温複数チップ実装"と協力し、熱管理や多数の配線引き出しに適したフリップチップ実装技術と量子制御性の適合性を検証した。量子ビットチップを静電破壊から保護するESD(静電気放電)保護素子をSiインターポーザに実装し、その極低温特性の評価を実施した。さらに昨年度評価したインターポーザから浮遊容量を大幅に低減させることで、極低温における量子ビットのRF反射読み出しに応用可能であることを確認した。これらの結果より、大規模な量子ビット制御に適合するインターポーザ設計に着手する上で重要な知見を得ることができた。

課題推進者:中島 峻(理化学研究所)

#### 3. 当該年度のプロジェクトマネジメント実施内容

#### (1)研究開発プロジェクトのガバナンス

# 進捗状況の把握

昨年度に引き続き、代表機関に構築したPM支援体制チームでプロジェクト推進を行った。PM支援体制チームには、日立製作所の産学連携部門、広報部門、知財担当部門等の本プロジェクトの運営に必要となるアシスタントスタッフが含まれる。研究開発プロジェクトのマネジメント業務、JSTとの連絡(PD等への報告、研究開発機関、JSTとの実施規約他実施管理上の各種調整業務)を産学連携部門が、研究開発成果の広報アウトリーチ活動を広報部門が、知財戦略、および、知財の取り扱い方針の策定を知財担当部門が担当している。加えて、各担当部門が密接に連携して本研究開発プロジェクトの推進・管理・支援を円滑に行うため仕組みについても、令和3年度から継続して運用している。

昨年度と同様に、プロジェクト全体定例会議を中心としてプロジェクト運営を行った。本定例会議では、重要事項の連絡・調整、各課題推進者の進捗状況・課題の把握、および共有等を行っており、各課題推進者一体となった研究開発体制の構築に大きく貢献している。また、積極的にサイトビジットの機会を設けており、課題推進者のアセットなどの正確な状況把握を行うとともに、研究開発課題の詳細議論・深耕、および、具体的な対策案の詳細議論も実施した。

#### 研究開発プロジェクトの展開

本プロジェクトでは、目標である大規模集積シリコン量子コンピュータの開発に向け、トップダウン、および、ボトムアップの2つのアプローチを採用している。トップダウン的なアプローチに必要となる半導体プロセス技術やCMOS回路・システム技術、さらにはマイクロプロセッサおよびコンピュータ技術に関して広範な技術開発の経験を有する学術界・産業界からの課題推進者(トップダウン的アプローチ)と、量子物理に精通しシリコン量子ビット操作の高精度化に関して世界最先端の位置にある学術界からの課題推進者(ボトムアップ的アプローチ)からなる研究開発体制を構築している。2つのアプローチに長けた各課題推進者が密接に連携することで、産業化と互換性のある大規模量子コンピュータの開発を強力に推進できると考える。とくに、プロジェクト内において日立製作所の研究者を理化学研究所や東京科学大学に派遣して共同実験を行ったり、神戸大学の研究者が日立製作所にて共同実験するなどを頻繁に交流や共同実験・研究を行っている。また、山本 俊PM、小芦PM (大阪大学藤井教授)のムーンショット目標6内プロジェクト間連携体制を構築している。さらに、大森 PM に課題推進者をアサインし、研究者を一部オーバーラップさせることで研究を加速している。

#### (2)研究成果の展開

学会・論文投稿、招待講演、および、学術誌への総説の寄稿を通じ、研究成果の情報公開を行った。これまでの活動に加え、展示会での成果発表による積極的なプレゼンス向上に努めるとともに、各課題推進者の所属する学生、および、関係者に向けた講義活動等を通じ、若手の人材育成に向けた取り組みを継続的に行った。

各課題推進者のグループからの成果発表の多くは国際会議や国際的論文誌にて発表 しており、これらの投稿などを通じグローバルな連携体制の構築を進めている。ケンブリッ ジ大学のキャベンディッシュ研究所内に設置された量子基礎物理に強みを持つ日立ケンブリッジ研究所との国際連携を継続しており、当該年度においても日立ケンブリッジ研究所の研究者と双方のサイトビジットも含めて意見交換の機会を設けた連携を本格化させた。また、ベルギーの非営利研究機関imecとの国際連携も強化している。

#### (3) 広報、アウトリーチ

課題推進者の所属している組織での研究成果に関する広報活動は、それぞれの機関にて活発に進めてもらっている。プロジェクト全体としては、米メタ社のInstagram(アカウント名:ms6siliconugntum)と当プロジェクトのホームページ

(https://ms6siliconquantum.jp)および当該年度に開設した当プロジェクト専用の YouTube チャンネル(https://www.youtube.com/@ms6siliconquantum)を活用して情報発信を 推進した。また、量子コンピュータ本体およびシリコン量子ビットチップ模型や量子コンピュータの動作原理解説用に作製した動画を活用し、文部科学大臣(2024年5月)を はじめとした多くの研究拠点来訪者に本プロジェクトの取り組みを紹介するととも に、技術展示会(2024年9月)に出展して広く一般に情報を発信した。

# \*Instagramの QR コード

#### (4) データマネジメントに関する取り組み

データマネジメントの一環として、BOX、および、Slackの運用を継続した。セキュリティ保護の必要となるファイル共有には、高度なセキュリティ対策が施されたBOXを活用する一方で、Slackは、研究課題推進者間での議論、情報共有を行う場として利用している。アクセス権に関しても制限を適正化することで、セキュアな情報管理と、課題推進者間での円滑な情報共有とを両立するデータマネジメント環境を構築した(BOX:各研究課題機関の取り纏め層のみにアクセス権を付与、Slack:各研究課題を行う参加者全員にアクセス権を付与)。

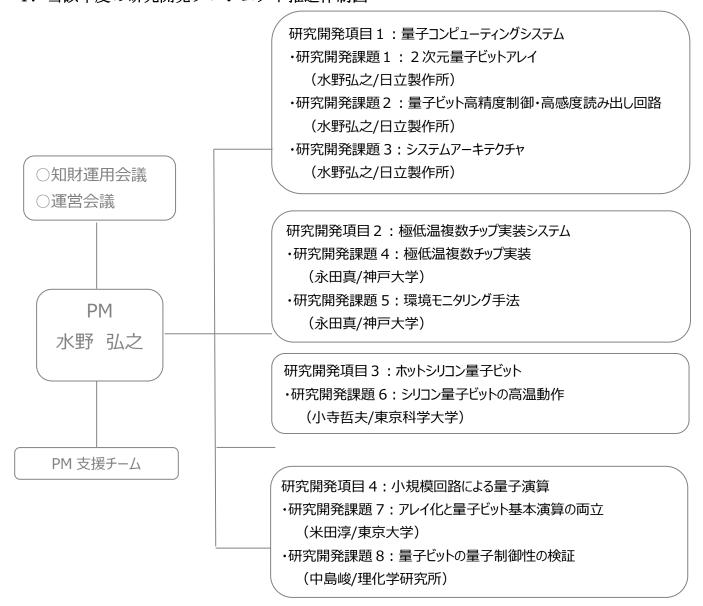

# 4. 当該年度の研究開発プロジェクト推進体制図

#### 知財運用会議 構成機関と実施内容

構成機関について、議長は PM、参加者は PM、課題推進者、同機関の知財部門、JST など関係部門が考えられるが、案件ごとに PM が機構と協議のうえ決定する。また、必要に応じて、本規約の遵守に同意した外部有識者を加える。実施内容は、本研究開発プロジェクトに関連する知的財産権の実施許諾条件等の運用に関し必要な事項について協議する。実施方法は、PM の判断により書面等による協議で代替できるものとする。

当該年度実施回数: 該当なし

#### 運営会議 実施内容

構成機関について、議長は PM、参加者は PM、課題推進者、PM が必要と認めた外部有識者、JST 等から構成する。実施内容については、実施規約に記載された以下の内容を中心に協議する場とする。 PM による新たな研究開発機関の参加、参加機関等以外からの本研究開発プロジェクトへの新たな関与者、実施規約の改正、課題推進者間の情報交換・助言等も協議の上行えるようにする。

当該年度実施回数:4回

# 5. 当該年度の成果データ集計

| 知的財産権件数  |    |            |      |      |

|----------|----|------------|------|------|

|          | 特許 |            | その他産 | 業財産権 |

|          | 国内 | 国際(PCT 含む) | 国内   | 国際   |

| 未登録件数    | 6  | 16         | 0    | 0    |

| 登録件数     | 0  | 0          | 0    | 0    |

| 合計(出願件数) | 6  | 16         | 0    | 0    |

|        | 会  | 議発表数 |    |

|--------|----|------|----|

|        | 国内 | 国際   | 総数 |

| 招待講演   | 8  | 7    | 15 |

| 口頭発表   | 13 | 16   | 29 |

| ポスター発表 | 4  | 7    | 11 |

| 合計     | 25 | 30   | 55 |

|          | 原著論文数(※ | (proceedings を含む) |    |

|----------|---------|-------------------|----|

|          | 国内      | 国際                | 総数 |

| 件数       | 0       | 9                 | 9  |

| (うち、査読有) | 0       | 9                 | 9  |

|     | その他著作物 | 数(総説、書籍など) |    |

|-----|--------|------------|----|

|     | 国内     | 国際         | 総数 |

| 総説  | 4      | 0          | 4  |

| 書籍  | 0      | 0          | 0  |

| その他 | 0      | 0          | 0  |

| 合計  | 4      | 0          | 4  |

| 受賞件数 |    |    |  |

|------|----|----|--|

| 国内   | 国際 | 総数 |  |

| 4    | 1  | 5  |  |

| プレスリリース件数 |

|-----------|

| 2         |

| 報道件数 |  |

|------|--|

| 26   |  |

ワークショップ等、アウトリーチ件数