# 1. 量子コンピューティングシステム

## 2024年度までの進捗状況

### 1. 概要

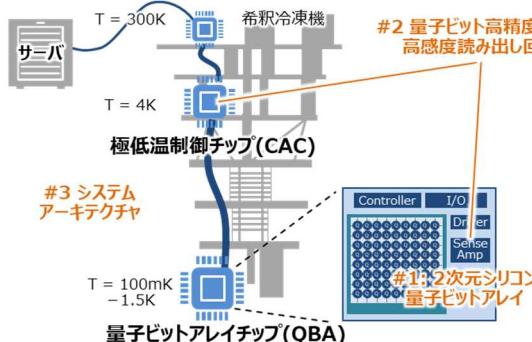

本研究開発項目は、プロジェクト全体を統括して量子コンピュータをシステムとしてまとめる役割を担いますが、図1の三つ（#1、#2、#3）の具体的な研究開発課題に取り組んでいます。

図1 本研究開発項目の構成

一つ目は、シリコン量子コンピュータを大規模化する際のマイルストーンである量子ビットの「2次元量子ビットアレイ」化に関する研究です。二つ目は、この量子ビットアレイを高精度に制御し量子情報を高感度に読み出すために必要となる「量子ビット高精度制御・高感度読み出し回路」を開発します。三つ目は、システム全体をコンピュータとして動作させるための「システムアーキテクチャ」を開発します。これらによって、シリコン半導体技術の特徴を活かした大規模集積シリコン量子コンピューティングシステムの実現をめざしていきます。

### 2. これまでの主な成果

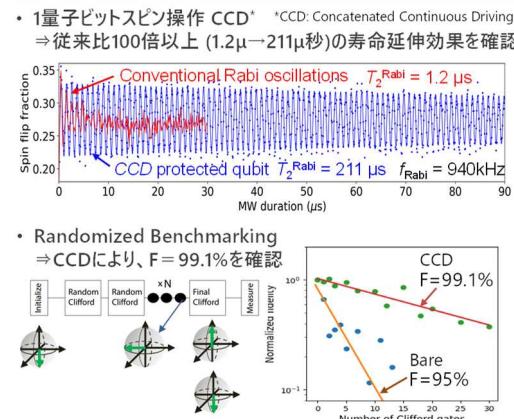

2次元量子ビットアレイ化に関する研究では、アレイ構造の試作・評価を通じ、1量子ビット、2量子ビットのスピン操作を行いました。スピン操作においてコヒーレンスをさらに改善させるスピン操作シーケンスについて検討し、スピン量子ビットにおいて、外界からのノイズを削減し、コヒーレンス時間を延伸させる量子ビット操作技術（CCD）を開発しました。また、2量子ビットのエンタングル状態を反映したCROTスペクトルを観測するとともに、CROTによる2量子ビット操作に成功しました（図2）。

図2 コヒーレンス時間延伸技術（CCD）

量子ビット高精度制御・高感度読み出し回路の研究では、量子ビットの更なる高精度制御を目的に、位相低減方式であるポーラー変調方式の適用したマイクロ波発生回路チップの詳細設計を完了し、振幅変調を間欠動作させることで電力効率を改善、位相変調用のLOブロックにはサンプリングPLL方式を採用し位相低減を図りました。検討の結果、位相誤差成分であるジッタを137 fsecから80

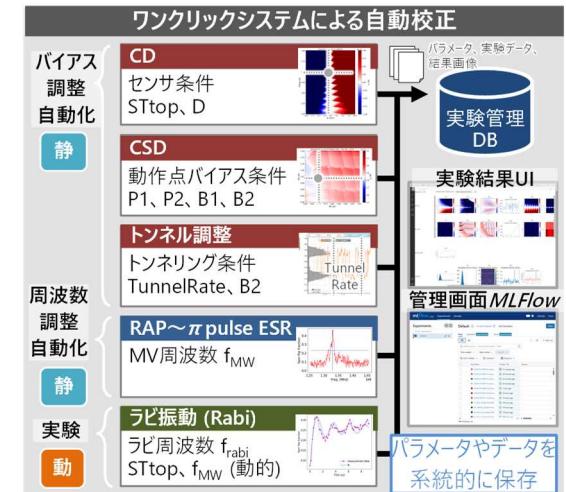

fsecに低減できる見込みを得ました。システムアーキテクチャの研究では、実験者支援のための量子オペレーティングシステムの拡張と、1量子ビットのラビ振動測定を自動化するワンクリック量子ビット測定システムを開発しました。分析処理の自動化手法を検討し、自動校正ライブラリの実装を完了した。天然シリコンデバイスを用いた実証試験の結果、自動校正によって測定時間を81%削減できることを確認とともに、動作状態のトレーサビリティの確保と温度・デバイス特性変動時に対する自動校正機能を確認しました（図3）。

図3 ワンクリック量子ビット測定システム

### 3. 今後の展開

FQC実現に向けては常識にとらわれない様々なノイバーションが必要です。プロジェクト内外との連携によって、半導体技術を最大限に活用した量子ビットアレイ構造での量子ビット操作を実現し、さらにシステムレベル実装によってその高信頼・効率化に取り組みます。

## 2. 極低温複数チップ実装システム

### 2024年度までの進捗状況

#### 1. 概要

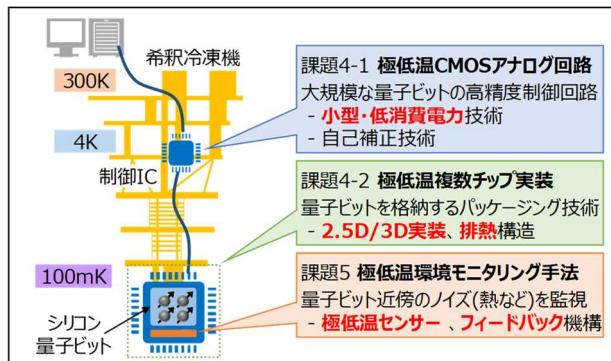

本研究開発項目は、シリコン量子コンピュータの大規模集積化に向けた極低温回路実装基盤技術を担っています。本テーマの達成により、多数のシリコン量子ビットの高精度制御および高密度実装が可能となり、プロジェクトが目指す大規模集積シリコン量子コンピュータの開発、さらにはムーンショット目標6で掲げる誤り耐性型汎用量子コンピュータの実現に貢献します。

その達成に向けて、次の3つの挑戦的な課題に取り組んでいます。まず、希釆冷凍機内部から多数の量子ビットを制御可能とする小型・低消費電力の極低温アナログ回路を開発します（課題4-1）。また、希釆冷凍機に量子ビットを格納する実装技術において、量子ビットチップとそのインターフェース機能をインターポーラー上に集積する革新的なパッケージング技術を開発します（課題4-2）。さらに、量子ビットの制御精度に影響を与える環境ノイズを監視し、制御回路にフィードバックする極低温環境モニタリング手法を確立します（課題5）。

#### 2. これまでの主な成果

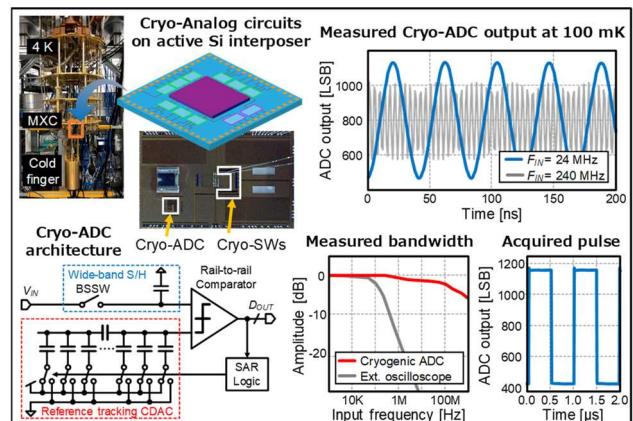

希釆冷凍機内の4Kステージからシリコン量子ビットを制御するため、16ビットのバイアス電圧生成回路を含む極低温量子制御回路を開発してきました。さらに高精度な制御を実現するため、量子ビットにより近い100mKの温度領域において信号の観測や量子ビットの読み出しに適用可能な極低温ADC変換回路を開発しました。本ADC変換器では、極めて厳しい消費電力の制約を満たしつつ広帯域性能を両立することを目的に、新たな回路アーキテクチャを考案し、これに基づく試作チップを開発しました。希釆冷凍機に本試作チップを搭載し、100mK温度領域において、30μWの消費電力で正常に動作することを確認しました。さらに、本回路を環境モニタリングシステムにおけるパルス信号波形の観測に適用し、等価サンプリング手法を用いることで、量子ビット近傍におけるパルス波形を1nsスケールの時間分解能で取得しました。

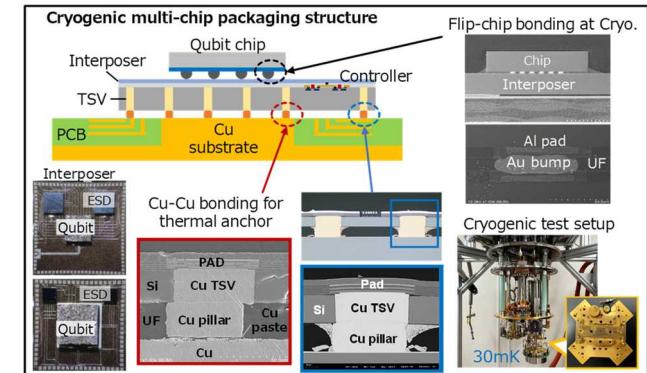

極低温複数チップ実装技術では、量子ビットチップとインターフェースチップの統合パッケージングの開発に加え、量子ビット動作時に発生する熱を効率的に排熱するチップ

実装技術の検討を行いました。シリコンインターポーラーにシリコン貫通ビアを形成し信号伝送と排熱を両立する極低温パッケージング構造を開発しました。銅の貫通ビアに銅ピラーを形成し、Cu—Cuボンディングにより銅基板と接続するプロセス技術を構築しました。さらに本パッケージング構造の極低温耐性を評価するため、極低温冷凍機を用いて熱サイクル試験を行い、断面観察により正常に接合状態が維持されていることを確認しました。現在は、極低温温度センサーを活用した環境モニタリング技術を用いて本構造の排熱特性評価の準備を進めています。

#### 3. 今後の展開

極低温量子制御回路や環境モニタリング技術を実際の量子ビット実験環境に導入します。量子ビット近傍におけるパルス信号の生成・観測を通じて、量子ビット制御精度の改善効果を検証します。また、極低温チップパッケージング技術では、インターポーラーを用いた量子ビット実験を継続するとともに、TSVを介した信号伝送および排熱機構の効果について実証評価を進めます。これらの取り組みを通じて、大規模集積シリコン量子コンピュータの実現に向けた回路・実装基盤技術を開発します。

## 研究開発項目

## 3. ホットシリコン量子ビット

## 2024年度までの進捗状況

## 1. 概要

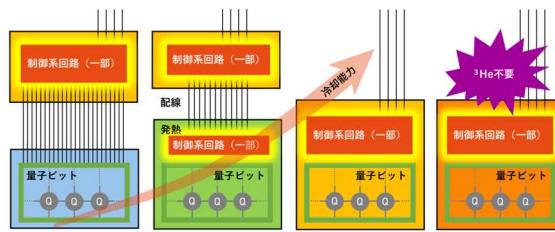

本研究開発項目では、シリコン量子ビット系を用いて、高温動作量子ビット（ホットシリコン量子ビット）の実現を目指します（図1）。ここでいう高温とは、通常固体量子ビットが動作する数十ミリケルビン(mK)と比べて高い、1ケルビン(K)程度（-272°C程度）を指します。通常より高温（1K以上）で動作する量子ビットが実現すれば、冷却能力の兼ね合いから、許容される回路消費電力（発熱）が飛躍的に向上し、量子ビットの近傍に極低温制御回路を配置することが可能になると期待されます。これにより、大規模集積シリコン量子コンピュータの実現に貢献することを目指します。

ホットシリコン量子ビットの実現に向けた課題として、温度上昇に伴う量子情報保持時間の低下が知られています。この常識を打ち破るべく、未開拓の物理の深耕と解明に基づき、量子情報保持時間が極大値をとるスイートスポットの探索に挑戦しています。また、量子ビットの性能や集積性・発熱の観点から電子スピン系とホールスピン系の比較を行うことで、高性能なホットシリコン量子ビットの達成に繋げることを目指しています。

図1：量子ビットの高温動作による許容される回路消費電力の向上と極低温制御系実装の概念図

## 2. これまでの主な成果

## ホットシリコン量子ビット実現に向けた要素技術の開発

- ① 操作：～1Kでのシリコン量子ビットの動作・高温下での高忠実度動作に向けた技術開発

- ② 読み出し：高温に適した読み出し手法の開発及び実証

- ③ 大規模化に向けた取り組み：集積構造提案・機械学習による自動調整・電荷雑音の評価・フリップ実装

+α シリコン量子コンピュータ実現に向けた多方面へのアウトリーチ活動

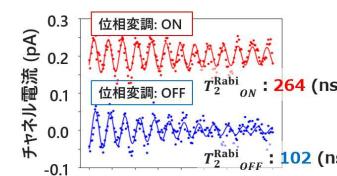

①操作：2024年度までのマイルストーンとなる～1Kでのシリコン量子ビットの動作として、ホールスピンのコヒーレントな時間発展が観測されました。また、高温下での高忠実度動作に向けた技術開発も進めており、位相変調マイクロ波によるスピニ位相緩和時間( $T_2^{\text{Rabi}}$ )の伸長効果をホールスピンで初めて実証しました（図2）。

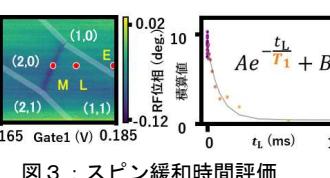

②読み出し：高周波反射測定法とは、量子ビット系に印加した高周波の反射率から量子ビットの状態を読み取る手法であり、高温でのスピニ量子ビット読み出し法として有望視されています。我々は、本手法の感度評価やそれを用いた高感度化などの技術開発に取り組んできました。開発した技術を用いて量子ビ

ットの情報保持能力のパラメータの一つであるスピニ緩和時間( $T_1$ )の評価が達成されました（図3）。[C. Kondo, et al., Jpn. J. Appl. Phys., 64, 01SP09 (2025)]

図2：位相変調マイクロ波による位相緩和時間の伸長

図3：スピニ緩和時間評価

Phys., 64, 01SP09 (2025)]

③大規模化に向けた取り組み：多角的なアプローチから大規模化に向けた研究を行ってきました。量子ビット集積構造の実現に向け、高密度構造にもかかわらず高速かつ個別制御が可能な二次元アレイ構造の提案や、モデルベース強化学習の手法を用いることで従来の手法と比較して高い汎用性が期待される量子ドット自動調整技術の開発を行いました。[C. Kondo, et al., APL Mach. Learn. 3, 016114 (2025)] また、量子ビットの性能を制限する代表的な雑音である電荷雑音の温度依存性の評価を行い、ホールスピン系において1Kまでの温度上昇に対して雑音レベルがほとんど増加せず、高温動作に有望であることが示唆されました。さらに、量子ビットとその制御用の極低温古典回路との集積技術の開発を進めています。神戸大学とのプロジェクト内連携により、インターポーザへフリップ実装されたシリコン量子ビットチップで、4Kにおいて想定された特性が確認されました。[T. Futaya et al., Jpn. J. Appl. Phys., 63, 03SP64 (2024)] さらに、同インターポーザに実装されたセレクタ回路による選択的制御が示されました。アウトリーチ活動：シリコン量子コンピュータの実現には個々の要素技術の開発とそれらの統合が求められます。そのため幅広い分野の研究者に技術を発信していくことが重要です。半導体量子ビットの研究動向と展望、個々の要素技術や課題などをまとめ、発表しました。[T. Kodera, JSAP Rev. 2024, 240101 (2024)、等] 将来の研究開発を牽引する量子人材の育成も行っており、QIH-MS6共催量子技術スプリングスクールの運営協力等を行いました。

## 3. 今後の展開

今年度までに蓄積した高温化・忠実度向上に関する課題の知見や量子ビットの初期化・読み出し・操作等の技術を活用しながら、シリコン量子ビットの1Kでの動作を評価・検証します。さらに、電子スピン系とホールスピン系のベンチマークを行います。

## 4. 小規模回路による量子演算

### 2024年度までの進捗状況

#### 1. 概要

本研究開発項目は、大規模なシリコン量子ビットアレイ構造の開発と並行して、将来的にその一部を構成する小規模実験回路を活用することにより、量子コンピュータ実現に向けた課題の早期抽出を目指しています。

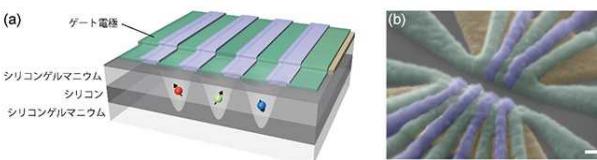

図1に示すような、量子ビットとしての動作が確立している小規模実験回路を用いて、量子ビットの初期化、読み出し、コヒーレント制御といった基本動作の高性能化を追究し、それらを組み合わせた量子演算操作を実証します。大規模な系での誤り耐性量子計算の実現可能性や、アレイ構造と両立する量子ビットの演算方式を検証し、プロジェクトの目指す大規模アレイ構造の設計指針を与えることを目指します。

図1 3つのシリコン量子ビットを制御可能な Si/SiGe 型の三重量子ドット試料の模式図(左)および電子顕微鏡写真(右)。スケールバーは 100 nm(1千万分の1 メートル)。

#### 2. これまでの主な成果

主に以下の6つに大別されます。

- ①アレイ内部の量子ビット初期化・読み出し手法を確立

- ②3つの量子ビットに対する汎用的な制御を実現

- ③誤り耐性閾値を上回る高精度2量子ビット操作を実現

- ④量子ビット制御の高速化とエラー低減の関係性を解明

- ⑤3つの量子ビットによる位相誤り訂正操作を実証

#### ⑥量子ビット間の誤り相関を観測

このうち、⑥は一次元シリコン量子ビットアレイ構造内部の量子ビットの初期化および読み出し手法を確立するものです。これまで困難だったアレイ内部の量子ビットの初期化・読み出し操作を実証しました。

⑦では、3つのシリコン量子ビットに対する汎用的な(ユニバーサルな)量子操作を実証しました。高い忠実度(88%)で3つのシリコン量子ビットの量子もつれ状態を生成できていることを世界で初めて確認しました。

⑧、⑨では、これまで量子ビット制御のボトルネックとなっていた2つの量子ビット間の制御 NOT 操作の高忠実度化を実現しました。誤り耐性量子計算の実現に十分な水準の高忠実度(99.5%)を実証し、雑音の低減によるさらなる高精度化に向けた研究開発の指針を得ました。

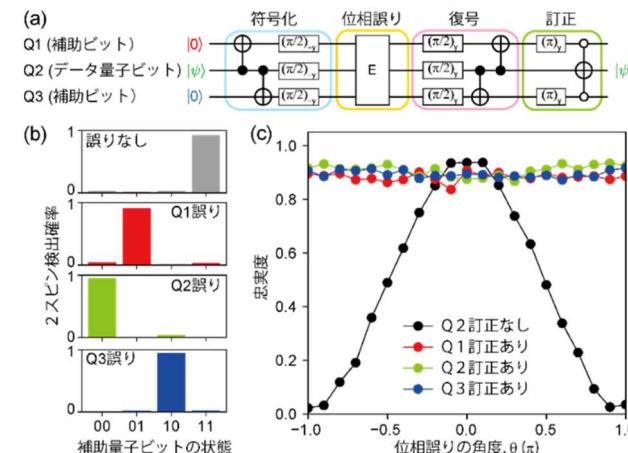

⑩では、3つの量子ビットの高忠実度制御を組み合わせて、位相誤り訂正回路をシリコン量子ビットで初めて実証しました(図2)。誤り耐性シリコン量子コンピュータの開発に

図2 シリコン3量子ビットを用いた位相誤り訂正実験。

おける重要なマイルストーンを達成したと言えます。

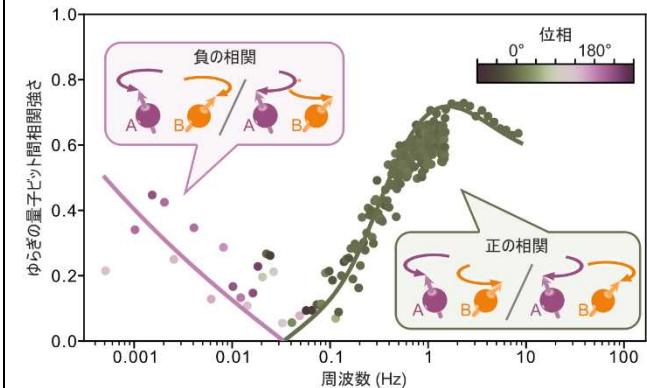

⑪では、アレイ構造における量子誤り訂正で課題となる、量子ビット間の誤り相関を評価しました。シリコン量子ビットに誤りをもたらす位相回転速度のゆらぎの測定(図3)から、隣接サイト同士でシリコン量子ビット間の誤り相関が強くなりうること、相関が距離に応じて減衰することなどが明らかになりました。また、相間に着目した雑音源の特性評価手法の開拓、電荷雑音相関評価の新規手法確立など、シリコン量子コンピュータの将来設計と性能向上に資する成果が得られました。

図3 シリコン量子ビット間のゆらぎの相関測定結果。

#### 3. 今後の展開

誤り耐性量子コンピュータの実現に向けて、これまでの高忠実度制御のパフォーマンスを損なわずに大規模化を図る方策の開発と、シリコン量子ビット誤り相関の理解深耕および活用に取り組んでいきます。シリコン量子ビットおよびアレイ構造の特徴、特性、制約等を踏まえて、大規模化に適した操作、初期化、読み出しなどの制御手法を検討し、大規模アレイ構造への適用を目指します。