スケーラブルな高集積量子誤り訂正システムの開発

#### 研究開発項目

# 5. 常温で動作するフロントエンドアナログ RF 部の LSI 化

## 2024年度までの進捗状況

#### 1. 概要

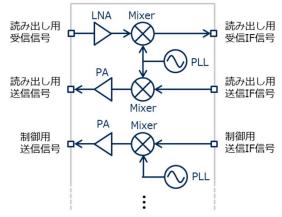

現状の常温環境に置かれた量子ビット制御装置において、マイクロ波制御信号を送受信するフロントエンドアナログ RF 部(図 1) は、高周波特性やノイズ性能に優れた化合物半導体デバイスや bipolar デバイス、多くのディスクリート部品で構成され、実装サイズが大きく、消費電力が大きい。今後、量子ビット数を増やしていくためには、フロントエンドアナログ RF 部の実装サイズおよび消費電力を飛躍的に削減する必要がある。そこで本研究開発項目では、フロントエンドアナログ RF 部の主要な機能ブロックであるPLL (Phase Locked Loop) 回路と送受信回路について、常温環境での使用を想定し、微細 CMOS デバイスでの設計を行い、小型化及び省電力化を目指す。さらに集積化で課題となる送受信間のアイソレーションの向上にチャレンジする。

図1 Qubit フロントエンドアナログ RF 部構成例 (一部)

### 2. これまでの主な成果

PLL 回路の低消費電力化、低ノイズ化の取り組みとして、PLL 比較周波数を 1GHz に設定し PLL 帯域を広くすることで、PLL 帯域内ノイズ化の低減を図った。その 1GHz の信号は簡素な Integer-N PLL で生成する構成とした。さらに、微細 CMOS プロセスを活かして、比較周波数 1GHz で動作するデジタルリッチな ADPLL (AII Digital PLL)を設計した。PLL テストチップ(図 2)を試作し、性能評価した結果、出力周波数 10GHz 時の PLL 帯域内位相ノイズは-105dBc/Hz であり、既存の量子ビット制御装置に搭載されている PLL に近いノイズ性能を得た。さらに、量子ビット制御装置で重要となる長期の位相揺らぎについては、ルビジウム発振器を基準とした測定系で、測定時間 1,000 秒、測定時間分解能40 ミリ秒の時間軸測定において、ADPLL 単体で 0.12 度 rmsを確認した。本開発の PLL の消費電力は、既存の量子ビット制御装置搭載の PLL より約 80%低減を図った。

(a) チップレイアウト

(b) パッケージ

図 2 PLL テストチップ

受信回路の低ノイズ化の取り組みとして、10GHz 帯 CMOS LNA (Low Noise Amplifier)の回路構成をノイズキャンセル 抑圧構成とした。LNA には高周波で信号損失を最小化する種々のレイアウト技術を用いたトランジスタを新たに開発した。送信回路は、PA (Power Amplifier) から受信回路への信号リークを抑圧するために、PA 回路の負荷に磁気リーク

を抑えるクローバ型のトランスを開発した。さらに、送受 信回路間アイソレーションの向上を目的として、LNA と PA に完全差動回路構成を採用した。こうした取り組みの有効 性を実証する送受信回路テストチップ(図 3)を 22nm SOI(Silicon On Insulator) CMOS で試作し、高周波特性の 優れる FOWLP (Fan Out Wafer Level Package) に封止し、常 温にて性能評価を実施した。10GHz 帯 CMOS LNA の NF (Noise Figure) はESD (Electro-Static Discharge) 耐性を有しなが ら約2.5dBを達成し、CMOS LNAとして業界トップレベルの NF を確認した。本開発の LNA の NF 特性は、シミュレーシ ョン結果と実測値の比較的良好な一致を示した。また、PA の送信出力は、微細 CMOS プロセスにおける低電圧動作に おいても既存の量子ビット制御装置と同等の 10dBm 以上を 実現した。さらに、送受信間アイソレーションは、送信回 路と受信回路を同一チップに集積しながら、目標値である 70dB 以上を達成した。本開発の送信回路と受信回路の消費 電力は、既存の量子ビット制御装置の 1/10 程度を実現し

(a) チップレイアウト

(b) パッケージ

図3 送受信回路テストチップ

#### 3. 今後の展開

今後は、テストチップの性能評価を完了させ、評価結果から課題抽出を行い、実現性を踏まえたフロントエンドアナログRF部の統合化の設計指針の確立を目指す。