## Large-scale Silicon Quantum Computer

#### Project manager

(selected in2020)

# MIZUNO Hiroyuki

#### Distinguished Researcher, Center for Exploratory Research, R&D Group, Hitachi, Ltd.

Leader's institution Hitachi. Ltd.

#### R&D institutions

Kobe University, Tokyo Institute of Technology, RIKEN

## Summary of the project

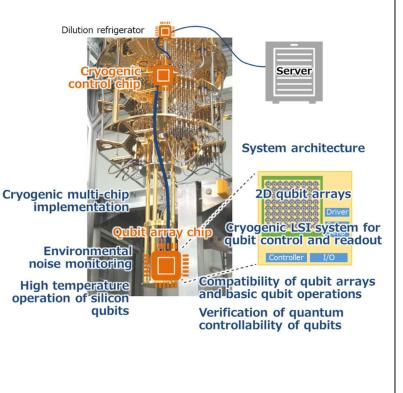

In order to realize a quantum error tolerant general-purpose quantum computer, it is necessary to improve both "quality" and "quantity" aspects of quantum computers. While the current development of quantum computers is dominated by a bottom-up approach that prioritizes "quality" and increases the number of qubits, this project will take the opposite top-down approach. In other words, in order to take advantage of the advanced integration capability of silicon semiconductor technology (i.e., the ability to implement a large number of elements with uniform characteristics), we will promote a system design that emphasizes "quantity" from the beginning. Next, we will develop various technologies (two-dimensional qubit arrays, cryogenic CMOS circuits and mounting systems, hot silicon qubits, digital correction, etc.) made possible by this high silicon integration to improve the "quality" of the system as a whole and realize an error-resistant general-purpose quantum computer.

## Milestone by year 2030

We will launch an experimental cloud service that will enable largescale silicon quantum computers and demonstrate the effectiveness of error correction and silicon quantum computers.

### Milestone by year 2025

We will develop a two-dimensional qubit array and demonstrate qubit operations on a silicon quantum computer using this array.

## **Project structure**

| R&D Theme                                     | Performer                                               | R&D challenge                                                                                                           |

|-----------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| 1 Quantum computing<br>system                 | Hitachi/<br>Hiroyuki Mizuno                             | 1 2D qubit arrays<br>2 Cryogenic LSI system for<br>qubit control and readout<br>3 System architecture                   |

| 2 Multi-chip cryogenic<br>packaing technology | Kobe Univ./<br>Makoto Nagata                            | 4 Cryogenic multi-chip implementation<br>5 Environmental noise monitoring                                               |

| 3 Hot silicon qubits                          | Tokyo Tech/<br>Tetsuo Kodera                            | 6 High temperature operation of silicon qubits                                                                          |

| 4 Quantum computing in small qubit systems    | Tokyo Tech/<br>Jun Yoneda<br>RIKEN/<br>Takashi Nakajima | 7 Compatibility of qubit arrays<br>and basic qubit operations<br>8 Verification of quantum<br>controllability of qubits |