# 戦略的創造研究推進事業 CREST 研究領域「ディペンダブル VLSI システムの 基盤技術」 研究課題「ディペンダブルネットワークオンチップ プラットフォームの構築」

研究終了報告書

研究期間 平成 20年 10月~平成 26年 3月

研究代表者:米田 友洋 (国立情報学研究所 アーキテクチャ科学研究系、教授)

# §1 研究実施の概要

# (1) 実施概要

集積システムの微細化・大規模化が進むにつれ、さまざまなアプリケーション製品の高機能化が図られ、VLSI 内収容コア数は急速に増加することになり、その実現はますます難しくなる、本研究は、GALS-NoC(Globally Asynchronous Locally Synchronous-Network On Chip)というアプローチをベースとして、高ディペンダブル・高性能・高アダプタブルなプラットフォームを実現し、セーフティクリティカルな車載制御アプリケーションに適用して、その有効性を実証しようというものである。

これを実現するため、本研究では、次のように回路レベル、ルーティングレベル、CPU コアレベル、および LSI チップレベルの各レベルにおいて、それぞれに適した高ディペンダビリティ実現手法を提案している。

- 回路レベル:オンチップネットワークを完全非同期式に実現した.これにより、各種環境変動や局所的な性能劣化に対しても高い耐性を得る.

- ルーティングレベル: 故障チップ, 故障ルータ, 故障リンクを迂回する, ディペンダブルルーティングアルゴリズムを開発した.

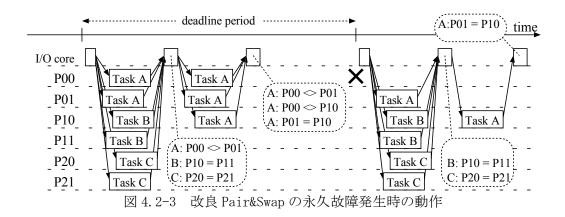

- CPUコアレベル: CPUコアレベルの故障に耐え,高信頼なアプリケーションタスク実行を実現するために,改良 Pair&Swap 方式を開発した.この方式では,通常は,各タスクを2つのCPUコアで二重実行し,その結果を比較することによりCPUコアの故障を検出する.不一致が生じた場合には,一時的に三重実行を行い,正しい結果を得るとともに,故障CPUコアを同定し,二重実行のためのペアを変更する.その後は,通常の二重実行に戻る.なお,ソフトエラー等に基づく一時的故障については,三重実行時に不一致が生じないため,元のペアを使い続ける.

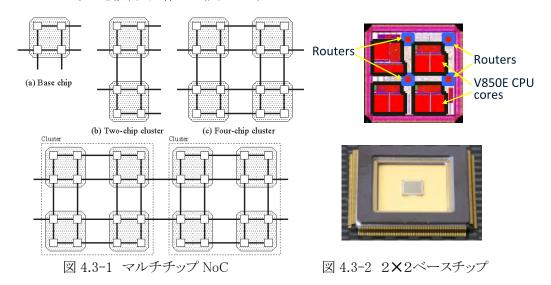

- LSI チップレベル:チップレベルの冗長性も容易に実現できるように,マルチチップ NoC を 提案している.マルチチップ NoC では,チップ内のオンチップネットワークがシームレスに マルチチップネットワークに拡張され,故障チップを迂回するルーティングを用いることにより,LSI チップ故障に対する高い耐性を持つ.

また,自動車メーカ・自動車関連メーカにてソフトウェア開発において多用される Simulink 記述を解析し、そこから自動生成された C コードによるタスクを、NoC 構成された複数のコアにメモリ制約や通信時間などを考慮した上で冗長に割り当てるためのソフトウェア開発支援ツールを開発した。これにより、ユーザは単一系の(冗長化を考慮していない)アプリケーションソフトウェアを開発するのみで、上記ハードウェアプラットフォーム上で、アプリケーションの高ディペンダブル実行を容易に行える。

さらに、提案手法を四輪独立制御に基づく統合車体制御という高度な実問題に適用し、HILS(Hardware In the Loop Simulation)システムにより詳細な実証を行うとともに、自動車関連メーカなどが提案プラットフォームを容易に評価できるような評価キットを開発し、上記アプリケーションをサンプルとして実行できる形で準備している。評価キットは、複数のNoCチップ、IOコアを実現する FPGA、HILS インターフェース、および簡易プラントモデルを含む。簡易プラントモデルは、ユーザが本格的な HILS システムを自前で用意することなくプラットフォームを評価できるように、精度は高くなくても、ECU機能のテストができる程度の小規模なプラントシミュレータであり、FPGA 上のソフトプロセッサにより実現する。さらに、さまざまな構成を試してみたいユーザのために、NoC を実現できる程度の大規模 FPGA を実装し、NoC チップの代替えとして使用できるようにする。

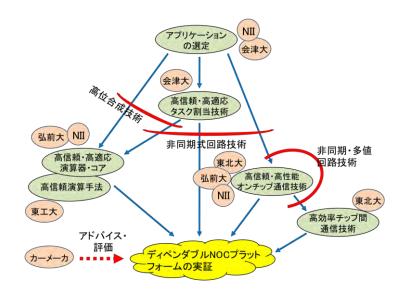

このように、本研究チームは、セーフティクリティカルな車載制御アプリケーションを高ディペンダブル・高性能・高アダプタブルに実行するためのプラットフォームを開発するという一貫した目標に向かって研究を進めてきた。これは本チームを構成する各研究グループが開発した要素技術、例えば、NII・弘前大グループによる完全非同期式オンチップネットワーク技術、弘前大・東工大グループによる冗長コア上での高信頼タスク実行技術、会津大グループによる故障を考慮した多重タスク割り当て・スケジューリング技術、東北大グループによる高速かつ高信頼

電流モードチップ間通信技術などを統合し、ハードウェアとソフトウェアからなる一つのプラットフォームという形にまとめ上げることにより成し得たものである.

#### (2)顕著な成果

<優れた基礎研究としての成果>

1. ディペンダブルルーティング機能を有する完全非同期式オンチップネットワーク

概要: (200 字程度) 単一チップ故障, 単一ルータ故障, 単一リンク故障等の故障要素を迂回し, パケットを目的地まで送り届けることのできるディペンダブルルーティングを, 完全非同期式オンチップネットワーク上に実現した. 非同期式ネットワークや耐故障ルーティング技術自体は従来から研究されていたが, それらを組み合わせ, 局所的な性能劣化に対して高い耐性を持つという回路レベルから故障要素を迂回するというルーティングアルゴリズムレベルまでのディペンダビリティを総合的に向上させた点が新しい.

#### 2. 高速かつ高電力効率非同期機能メモリ技術

概要: (200 字程度) データ転送ボトルネックを解消する典型例として,機能メモリ (Content-Addressable Memory: CAM)を取り上げ,その高性能化と低消費電力化の両立を実現した.検索アルゴリズムの改良と共に,非同期式制御を活用することにより,従来方式 CAM(65nm CMOS プロセス実現)と比べ,90nm CMOS プロセス実現にも関わらず,検索時間,電力効率を共に低減させることに成功した.

# 3. 冗長コア上での高信頼タスク実行技術

概要: (200 字程度) 豊富な冗長コアが存在する環境で、タスク実行を高信頼かつ高可用に行う技術を開発した。この方式では、通常は、各タスクを2つの CPU コアで二重実行し、その結果を比較することにより CPU コアの故障を検出する。不一致が生じた場合には、一時的に三重実行を行い、正しい結果を得るとともに、故障 CPU コアを同定し、二重実行のためのペアを変更する。この技術は、従来の単純な三重実行やスペアを用意しておく方式に比べ、より効率よくサービスを長時間提供し続けることができる。

# <科学技術イノベーションに大きく寄与する成果>

1. 冗長コアへの多重タスク割り当て・スケジューリング技術

概要: (200 字程度) 上記の冗長コア上での高信頼タスク実行を行うために,各コア上にアプリケーションの各タスクを冗長に割り当て,二重実行をどのコアでいつ実行させるかというタスク割り当て・スケジューリングを行う技術を開発した.この技術により,ユーザは単一系のアプリケーションソフトウェアを開発するのみで,冗長コア上での高信頼タスク実行が可能となる.この技術はツール化し,評価キットに含めるとともに,カー関連メーカからツール単体としての関心を寄せられている.

# 2. マルチチップネットワークオンチップ技術

概要: (200 字程度) チップ内のオンチップネットワークがシームレスにマルチチップネットワークに拡張されるマルチチップ NoC を開発した.これは,一つのチップに多数のコアを搭載することに対して,カーメーカ等が持つチップ故障の懸念を解決するためのものであり、この技術により,豊富な冗長性を容易に実現できるという優れた特長を持つネットワークオンチップベースの統合型 ECU がカーメーカ等に受け入れられるようになった.この技術は特許出願済である.

#### 3. 高速かつ高信頼電流モードチップ間通信技術

概要: (200 字程度) 高速シリアルデータ転送を実現するための非同期式電流モード回路を開発した. 少ない配線数, 高い電流駆動能力, 効率的なパワーゲーティング機能などの特長を有する電流モードシングルトラック方式を考案し, 高速性と低消費電力性を両立した

チップ間インターフェース部を実現した.また、転送エラー対策として、Level-Encoded Dual-Rail (LEDR) 符号の性質を利用した再送機構も考案した.この回路を応用することによりマルチチップ NoC のシステム性能を向上させることが可能である.

# § 2. 研究構想

#### (1) 当初の研究構想、課題設定

#### ①本研究の背景、社会や産業に存在する問題と本研究の課題設定

集積システムの微細化・大規模化が進むにつれ、さまざまなアプリケーション製品の高機能化が図られ、VLSI 内収容コア数は急速に増加することになり、その実現はますます難しくなる。まず、チップ内長距離配線の伝送速度低下や伝送障害、配線困難性、配線間干渉等の問題が生じる。また、高速クロックのネットワーク全域への分配困難性や、アイドルネットワーク部の電力消費も大きな問題である。さらに、非常に高い信頼度を必要とするアプリケーションの場合、コア故障による該当機能の処理能力喪失を防ぐために、コアの冗長化や故障検出・診断情報に基づく動的再構成が必須となるが、従来のバス接続構成では予め冗長化構成を決めておく必要があり、ディペンダビリティを保証するためのフレキシビリティ実現に制約が大きかった。

これらを解決するために、GALS-NoC(Globally Asynchronous Locally Synchronous-Network On Chip)方式が研究されるようになってきたが、依然として解決すべき問題がある. 例えば、NoC 構成 によりフレキシビリティ実現は容易となるが、コア故障の検出や診断の手法、また、それに基づく動 的再構成法などのディペンダビリティ実現手法が確立されていない. すべてのタスクを三重化実行 するなどではなく、必要となる信頼度に応じた冗長化構成が選択されるべきである. チップ全体の 故障を考慮する必要がある場合は、チップレベルの冗長性を持たせる必要があるが、オンチップネ ットワークをシームレスにマルチチップネットワークに拡張する手法は確立されていない. また, 単 なるコアの寄せ集めによる冗長・不要部分の増加や微細化によるチップ内の局所的な性能劣化と いう問題も大きい、これらはチップの物理的、コスト的な実現性を難しくし、またマージン増加による 性能低下を引き起こす. ある試算によると, 32nm テクノロジでは, さまざまな要因に起因するばらつ きにより,標準のものに比べて 6 倍以上も遅いゲートが存在し得る.これを単純にマージン増加で 対応するのは非常に非効率的である。さらに、GALS-NoC におけるオンチップネットワーク部に生 じる局所的な固定故障やソフトエラーは、パスが遮断されることにより多くの正常コアが使用不能と なる危険性を持つ.このような問題が及ぼす影響は、プロセスのテクノロジが進み、微細化が進む につれてより大きくなることに注意しなくてはならない. そこで、プロセスの微細化により悪影響を受 けるのではなく、その恩恵を十分に享受できるプラットフォームの開発が非常に重要となりつつあ る.

# ②本研究チームの達成目標。

VLSI 内収容コア数が急速に増加し、また、微細化が進んでも、設計・実装が容易で、プロセステクノロジの進化の恩恵を享受できるプラットフォームとして、我々は「多数のコアが適応的に協調動作して異種多様なタスクを効率よく、かつ、高信頼に実行できるプラットフォーム」を考え、それを新しい技術に基づくマルチチップ NoC システムとして実現すること、および、それを車載制御系システムにおいて実証することを目標とする。具体的には、以下を達成することによりこのプラットフォームを実現する。

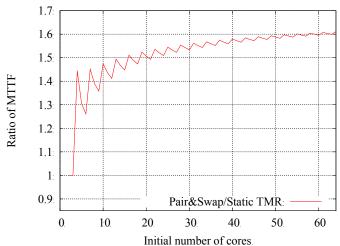

1. 同種の複数の CPU コアやアクセラレータコアと入出力を司る IO コア等を高速なオンチップネットワークで接続する. これにより、センサ・アクチュエータ等の入出力と、それらに対する処理を行うコアとの対応に自由度が増す. また、タスクの信頼度要求と想定する故障パターンに応じた複数の冗長化構成を求めておき、各コアの故障状況に応じて適応的に構成を切り替えてタスクを実行する. これにより、タスクの信頼度要求に応じた冗長性を持たせることが容易となり、また場合によっては重要度の小さい処理を切り捨てること等も合わせて、重要な処理をより長時間にわたり遂行し続けることができる. 例えば、静的に冗長タスク割り当てを行った上で、プロセス二重化と比較により故障の検出を行い、一時的な三重化実行により永久故障コアの同定と再構成を行う改良 Pair&Swap[2-1]手法を用いた場合、非冗長なものに比べてはもちろ

ん,静的な三重化冗長(TMR: Triple Module Redundancy)を構成したシステムと比較しても、障害が生じるまでの時間(MTTF: Mean Time To Failure)を延ばすことが出来る. 仮に初期状態のコア数が 6, コアの障害率を $\lambda$ とすると、改良 Pair&Swap の MTTF は  $29/(20\,\lambda)$ ,静的 TMR の MTTF は  $69/(60\,\lambda)$ となり、動的なタスク割り当てを行うことにより、約 1.26 倍長く重要な処理を遂行し続けることが出来る. この差は初期状態のコア数が増加するとより顕著になることが見込まれる. コア数とMTTFの関係を比較すると上図のようになり、コア数が増加すれば重要な処理を 1.6 倍程度長く継続実行することが望める.

- 2. オンチップネットワークを完全非同期式により実現する. これにより, 局所的な性能劣化に対しても高い耐性を持ち, また同期式で必要となる過度のマージンやシンクロナイザによるオーバヘッドを除去できる. 各コアは, ローカルなクロックで動作することができ, クロック木生成やクロックスキューの問題に対する実装コストが大幅に低減できる.

- 3. オンチップネットワークをシームレスにチップ間に拡張できる機構を実現する. これにより, 冗長化タスクを異なるチップ上のコアで実行することが容易となり, 自動車メーカの厳しいディペンダビリティ要件に, より容易に対応できる. ただし, LSI パッケージのピン数制約により, マルチチップネットワークでは, オンチップネットワークのトポロジを完全に保存できない, また, チップ間リンクのバンド幅が減少する等の問題が生じる. これらを, 前者についてはルーティングアルゴリズムの工夫により,後者は完全非同期式オンチップネットワークと高い整合性を持つ,高速・高効率のチップ間通信を開発することにより解決する.

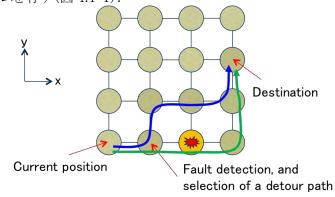

- 4. ディペンダブルかつ適応的ルーティングアルゴリズムを有するオンチップネットワークを実現する. これにより、ネットワーク部の局所的な故障による影響を最低限に抑え、正常コアの多くを救済することができる. 例えば、4×4構成の2次元メッシュで座標(1,1)のルータが故障した場合、広く使われているXYルーティング(まずX方向に移動し、次にY方向に移動する)では、すべてのコアにおいて、故障したルータに接続されているコア(1,1)以外のいくつかのコアとも通信ができなくなるのに対し、1ルータ故障に耐えられるディペンダブルルーティングアルゴリズムでは、(1,1)以外のコアとの通信は影響を受けない. コア(1,1)以外のコアで、影響を受ける送受信ペア数の全体に対する割合で比較すると、XYルーティングの17%に対し、

ディペンダブルルーティングでは 0%となる. また, 座標(2, 2)のルータも同時に故障した場合 を考えると, XYルーティングでは 33%と 1/3 のペアが通信できなくなるのに対し, 前記ディペンダブルルーティングではその割合を全体の 4%に抑えることができる.

- 5. 四輪独立制御に基づく統合車体制御という,高度な実問題に適用して,HILS(Hardware In the Loop Simulation)システムにより詳細な実証を行う. これにより,自動車メーカ,自動車関連メーカに提案手法の有効性をアピールできる.

- 6. 自動車メーカ,自動車関連メーカで,提案プラットフォームを容易に評価できるような評価キットを開発し,上記四輪独立制御に基づく統合車体制御アプリケーションをサンプルとして実行できる形で提供する.これは,ハードウェアとして,試作した複数のNoCチップ,IOコアを実現するFPGA, HILS インターフェース,および簡易プラントモデルを含む. 簡易プラントモデルは,ユーザが本格的な HILS システムを自前で用意することなくプラットフォームを評価できるように,精度は高くなくても,ECU 機能のテストができる程度の小規模シミュレータであり,FPGA上のソフトプロセッサにより実現する.さらに,さまざまな構成を試してみたいユーザのために,NoCを実現できる程度の大規模FPGAを実装し,NoCチップの代替えとして使用できるようにする.一方,上記ハードウェアでのソフトウェア開発を容易にするために,単一系のSimulink 記述を入力とし,与えられた信頼度要求を満足するように静的にタスクを冗長に割り当てるツールを提供する.

このようなプラットフォームの実現により、このプラットフォームのユーザである自動車メーカは、量産時のコスト削減(従来のエンジン制御関係の ECU 例えば 10 チップを、冗長化も含めて 3 つの NoC チップで実現でき、チップ数が7割程度減る)、および、ディペンダビリティの実現容易性(センサ・アクチュエータと ECU の対応をフレキシブルにでき、また、NoC により容易に冗長化や動的な実行コア再構成を実現できる)を享受することができる。また、その結果、車のユーザにとっても、メインテナンスコスト減につながると考えられる。

[2-1]Masashi Imai, Tomohiro Yoneda: "Duplicated Execution Method for NoC-based Multiple Processor Systems with Restricted Private Memories," Proc. of DFT2011, (Vancouver, Canada), Oct., 2011.

# ③本研究の特徴

本研究は、GALS-NoC(Globally Asynchronous Locally Synchronous-Network On Chip)というアプローチをベースとして、高ディペンダブル・高性能・高アダプタブルなプラットフォームを実現し、セーフティクリティカルな車載制御アプリケーションに適用して、その有効性を実証しようというものである。車載制御システムへのマルチコア/メニーコアシステムの適用は、統合型 ECU(Electronic Control Unit)として知られており、例えば下記のようなヨーロッパのプロジェクトでは、NoC ベースの統合型 ECU を想定している。

- Recomp: Reduced certification costs for trusted multi-core platforms. http://atc.ugr.es/recomp/.

- Race: Robust and reliant automotive computing environment for future ecars. http://projekt-race.de/.

NoC ベースの統合型 ECU では、スケーラブルかつフレキシブルであるという特徴から、冗長性や 負荷分散を実現しやすいという長所を持つ. しかし、カーメーカ等ではチップ全体が故障する可能性を危惧することから、例えチップ内に冗長性を有しても、一つのチップからなる NoC ベースの統合型 ECU は受け入れ難いようである.

本研究の優位性の一つは、チップレベルの冗長性も容易に実現できるように、マルチチップ NoC を提案している点にある。マルチチップ NoC では、チップ内のオンチップネットワークがシームレスにマルチチップネットワークに拡張されるため、ユーザはチップの境界を意識する必要はない。LSIパッケージのピン数の制約から、チップ間リンクは部分的にシリアル化する必要があるが、高速かつ高効率チップ間通信方式を開発することにより、チップを跨ぐことによる効率低下を防げる。

これに加え, 本研究では, 次のように回路レベルから CPU コアレベルまで, それぞれに適した高

ディペンダビリティ実現手法を提案している.

- ●回路レベル:オンチップネットワークを完全非同期式に実現する.これにより,各種環境変動や 局所的な性能劣化に対しても高い耐性を得る.

- ルーティングレベル: 故障チップ, 故障ルータ, 故障リンクを迂回する, ディペンダブルルーティングアルゴリズムを用いる.

- CPU コアレベル:通常は、各タスクを2つの CPU コアで二重実行し、その結果を比較することにより CPU コアの故障を検出する. 不一致が生じた場合には、一時的に三重実行を行い、正しい結果を得るとともに、故障 CPU コアを同定し、二重実行のためのペアを変更する. その後は、通常の二重実行に戻る. なお、ソフトエラー等に基づく一時的故障については、三重実行時に不一致が生じないため、元のペアを使い続ける.

また、自動車メーカ・自動車関連メーカにてソフトウェア開発において多用される Simulink 記述を解析し、そこから自動生成された C コードによるタスクを、NoC 構成された複数のコアにメモリ制約や通信時間などを考慮した上で冗長に割り当てるためのソフトウェア開発支援ツールを開発している。これにより、ユーザは単一系の(冗長化を考慮していない)アプリケーションソフトウェアを開発するのみで、上記ハードウェアプラットフォーム上で、アプリケーションの高ディペンダブル実行を容易に行える。

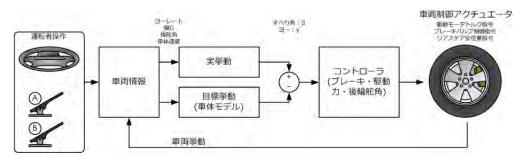

さらに、提案手法を四輪独立制御に基づく統合車体制御という高度な実問題に適用し、HILS(Hardware In the Loop Simulation)システムにより詳細な実証を行う。このアプリケーションは、ドライバの意図に基づいて四輪のトルク、制動力、および後輪の操舵を最適に制御するもので、その機能の喪失はスピン等のドライバの命に関わる事故を招きかねない。そのため、各レベルでの冗長性により高い可用性を有する提案手法の実証に適している。

# ④研究実施方法

1) 本研究チーム運営の方針、研究グループ間の分担・協力関係

下図のように、各種コア・オンチップネットワーク部は主に NII・弘前大グループが担当し、東北大グループは主にチップ間通信技術を担当する。会津大グループは高位合成・タスク割り当て技術を担当する。東工大グループはルータによる高信頼演算手法の適用を担当する。チーム内でのミーティングは月に 1 回程度必ず行っており、すべてのグループが、担当以外の部分についても詳細な設計や結果について把握し、毎回突っ込んだ議論を行っている。また、HILS システムが NII に設置されていることから、これまでの実機での基盤開発は NII グループが中心となって行ってきたが、H24 年度から弘前大にも設置され、現在は各グループの成果を組み込んで、より効率良くNoC プラットフォームの開発・実証に取り組んでいる。

#### 2) 領域外部の企業等との連携

自動車メーカとの年1~2回のミーティングを通して、成果の報告とアドバイスを頂いている。センサ・アクチュエータ等と対応するタスクを実行するコアとの対応関係をフレキシブルにすることの重要性、チップ間通信の必要性、ハイブリッドエンジン制御、四輪独立制御に基づく統合車体制御というアプリケーションの選択、等は自動車メーカとのミーティングにおける議論から得られたものである。

さらに、ハイブリッドエンジン制御、四輪独立制御に基づく統合車体制御の高位モデル(Simulink モデル)をECUメーカと共同開発している。また、非同期式回路実装用ツールをツールメーカと共同開発している。このほか、ユタ大学、南テキサス大学とNoCプラットフォームの形式的検証の可能性について共同研究している。

さらに, 提案プラットフォームの自動車メーカ等への提供可能性について半導体メーカと議論している.

# 3) 領域内他研究チームとの連携関係

梶原チームの大竹グループとは、非同期式回路のテスト技術において連携し、効率の良いスキャン技術を開発している. 大竹グループでは、既に何件か特許出願を行っている.

- (2)新たに追加・修正など変更した研究構想、発展テーマ

- ① 中間報告書§ 6. 今後の研究の進め方、および研究成果の見通しの記載事項に関し、研究を進めた結果について

中間報告書§6で提案した評価キットは順調に開発が行えており、NoC チップ (ASIC) 版ハードウェア、FPGA 版ハードウェア、ソフトウェア開発支援ツール、簡易プラントモデルが、それぞれほぼ完成している。この上で、四輪独立制御に基づく統合車体制御アプリケーションが稼働しており、それが HILS 環境および簡易プラントモデルの双方で実証デモを行える状況である。特に、簡易プラントモデルは、HILS の環境をFPGA 内に実現したもので、HILS 環境を用意することなく、上記アプリケーションを高信頼実行できる様子を容易に体験できる。また、開発支援ツールを使うことにより、タスクの粒度・冗長度等を変更して試すことができるし、Simulink プログラムを変更・開発することで、ユーザ独自の制御アルゴリズムを試みることもできる。

# §3 研究実施体制

- (1)研究チームの体制について

- ① 「NII」グループ

#### 研究参加者

| 氏名                    | 所属          | 役職      | 参加時期        |

|-----------------------|-------------|---------|-------------|

| 米田 友洋                 | 国立情報学研究     | 教授      | H20.10∼     |

|                       | 所           |         |             |

| 王 代涵                  | 同上          | 特任研究員   | H21.4~H24.3 |

| Galle Mannakkarage,   | 同上          | 特任研究員   | H21.4~H25.2 |

| Chammika Mannakkara   |             |         |             |

| Holimath, Vijayakumar | 同上          | 特任研究員   | H21.4~      |

| 市川 淳                  | 同上          | 特任研究員   | H25.2~H25.3 |

| 中井 一貴                 | 同上          | 特任研究員   | H24.6~      |

| 小泉 夢月                 | 道場          | 特任研究員   | H25.4~      |

| 中村 祐一                 | 国立情報学研究     | 客員教授(本務 | H21.5∼      |

|                       | 所(本務は NEC シ | は主幹研究員) |             |

|             | ステム IP コア研 |     |         |

|-------------|------------|-----|---------|

|             | 究所)        |     |         |

| 鯉渕 道紘       | 国立情報学研究    | 准教授 | H23.4∼  |

|             | 所          |     |         |

| Chris Myers | ユタ大        | 教授  | H21.10∼ |

| Hao Zheng   | 南フロリダ大     | 講師  | H21.10∼ |

# 研究項目

- (ア)ルータ, 伝送方式, ネットワークインターフェースの全体設計

- (イ) CPUコア演算部の耐劣化性実現

- (ウ) ハードウェアアクセラレータの実現

# ②「弘前大」グループ

# 研究参加者

| 氏名     | 所属               | 役職    | 参加時期         |

|--------|------------------|-------|--------------|

| 今井 雅   | 東京大学 駒場オープン      | 特任准教授 | H20.10∼      |

|        | ラボラトリー/先端科学技     |       |              |

|        | 術研究センター          |       |              |

|        | (H20.10∼H23.12), |       |              |

|        | 弘前大学大学院 理工学      | 准教授   |              |

|        | 研究科              |       |              |

|        | (H24.01∼)        |       |              |

| 山口 徹   | 東京大学 先端科学技術      | 特任研究員 | H21.4~H23.12 |

|        | 研究センター           |       |              |

| 高田 幸永  | 東京大学大学院 情報理      | 修士学生  | H20.10~H21.3 |

|        | 工学研究科            |       |              |

| 長井 智英  | 同上               | 修士学生  | H20.10~H22.3 |

| 武安 聡   | 同上               | 修士学生  | H21.4~H23.3  |

| 渡辺 千洋  | 同上               | 修士学生  | H21.4~H21.9  |

| 藤岡 悟史  | 弘前大学大学院 理工学      | 研究補助者 | H24.6~H26.2  |

|        | 研究科              |       |              |

| 佐藤 謙介  | 弘前大学大学院 理工学      | 修士学生  | H25.4∼       |

|        | 研究科              |       |              |

| 五十嵐 大将 | 弘前大学             | 学部学生  | H25.4~       |

| 池野 武   | 同上               | 学部学生  | H25.4~       |

| 工藤 三四郎 | 同上               | 学部学生  | H25.4~       |

| 寺山 恭平  | 同上               | 学部学生  | H25.4~       |

# 研究項目

- ・ 非同期式回路設計用セルライブラリの設計・評価,多入力アービタの設計・評価

- NoC ルータの設計・評価

- ・ プロセッサレベル・回路レベルの故障判定・再構築手法の確立

- マルチクロック・デュアルエッジトリガ・フリップフロップの設計・評価

# ③「東北大」グループ

# 研究参加者

| 氏名 | 所属 | 役職 | 参加時期 |

|----|----|----|------|

| 羽生 貴弘 | 東北大学電気通信研究所        | 教授   | H20.10~H.26.3  |

|-------|--------------------|------|----------------|

| 松本 敦  | 東北大学電気通信研究所        | 助教   | H20.10~H.25.3  |

|       | (H20.10∼H.24.9)    |      |                |

|       | 群馬工業高等専門学校         |      |                |

|       | (H24.10∼H.25.3)    |      |                |

| 鬼沢 直哉 | 東北大学電気通信研究所        | 研究員  | H21.4~H.26.3   |

|       | (H20.10~H.23.3)→中略 |      |                |

|       | 東北大学学際科学フォロ        |      |                |

|       | ンティア研究所 助教         |      |                |

|       | (H25.12∼)          |      |                |

| 永井 亮  | 東北大学電気通信研究所        | 修士学生 | H20.10~H.21.3  |

| 大竹 遥  | 同上                 | 修士学生 | H20.10~H.22.3  |

| 松浦 貴史 | 同上                 | 修士学生 | H20.10~H.21.3  |

| 船崎 智義 | 同上                 | 修士学生 | H21.4~H.23.3   |

| 有光 貴志 | 同上                 | 修士学生 | H22.4~H.23.3   |

| 河野 宇朗 | 同上                 | 修士学生 | H22.4~H.24.3   |

| 渡邊 友馬 | 同上                 | 修士学生 | H24.4~H.26.3   |

| 高橋 温  | 同上                 | 研究員  | H24.11~H.24.12 |

| 畠山 孝喜 | 同上                 | 研究員  | H24.12~H.25.3  |

| 白濱 弘勝 | 同上                 | 研究員  | H25.4~H.26.3   |

# 研究項目

- ・ チップ間転送技術の開発

- ・ 高信頼性を有する多値データ転送方式の開発

- 高位評価手法の開発

- ・ 回路コンポーネント実装・評価

# ④「会津大」グループ

# 研究参加者

| 氏名              | 所属         | 役職      | 参加時期         |

|-----------------|------------|---------|--------------|

| 齋藤 寛            | 会津大学       | 上級准教授   | H20.10∼      |

| 山口 亮            | 同上         | 派遣スタッフ  | H23.4~H24.3  |

| 濱田 尚宏           | 同上         | 特別研究支援者 | H20.10~H25.3 |

| 平田 幸介           | 同上         | 修士学生    | H20.10~H22.3 |

| 堀添 裕太           | 同上         | 修士学生    | H21.4~H22.3  |

| 清水 浩之           | 同上         | 修士学生    | H20.10~H22.3 |

| 古川 優也           | 同上         | 修士学生    | H20.10~H22.3 |

| Dmitry Vazhenin | 同上         | 博士学生    | H21.4~H24.3  |

| 広沢 篤則           | 同上         | 修士学生    | H22.4~H23.3  |

| 松浦 光児           | 同上         | 修士学生    | H22.4~H23.3  |

| 方波見 英基          | 同上         | 修士学生    | H23.4~H25.3  |

| 飯塚 成            | 同上         | 修士学生    | H23.4~H24.3  |

| 吉田 英一           | 福島県ハイテクプラザ | 主任研究員   | H22.4∼       |

| 木村 裕彦           | 会津大学       | 派遣スタッフ  | H24.4~H24.9  |

| 宮囿 悟            | 同上         | 修士学生    | H25.4~       |

| 竹内 信一           | 同上         | 派遣スタッフ  | H25.4∼       |

#### 研究項目

- タスクの多重スケジューリング・多重割り当て手法の研究とツールの開発

- ・ 動作合成ツールの開発

- リアルタイム OS の実装と評価

# ⑤「東工大」グループ

# 研究参加者

| 氏名            | 所属        | 役職   | 参加時期         |

|---------------|-----------|------|--------------|

| 吉瀬 謙二         | 東京工業大学大学院 | 准教授  | H24.10~      |

|               | 情報理工学研究科  |      |              |

| 佐藤 真平         | 同上        | 博士学生 | H25.4∼       |

| 藤枝 直輝         | 同上        | 博士学生 | H24.10~H25.3 |

| 高前田 伸也        | 同上        | 博士学生 | H24.10~      |

| 小林 諒平         | 同上        | 博士学生 | H24.10∼      |

| 笹河 良介         | 同上        | 博士学生 | H24.10∼      |

| 池田 貴一         | 同上        | 修士学生 | H24.10~      |

| 五十嵐 俊哉        | 同上        | 修士学生 | H24.10∼      |

| 上野 貴廣         | 同上        | 修士学生 | H24.10∼      |

| 浅野 悠          | 同上        | 修士学生 | H25.4∼       |

| Thiem Van Chu | 同上        | 修士学生 | H25.10∼      |

#### 研究項目

- ・ 3重実行をサポートする高機能 NoC ルータアーキテクチャの開発

- ・ 高機能 NoC ルータアーキテクチャの評価

# §4 研究実施内容及び成果

- 4.1 ディペンダブル・ルーティング・アルゴリズムを有する完全非同期式オンチップネットワーク (NII グループ・弘前大グループ)

- (1)研究実施内容及び成果

# ① 実施方法・実施内容

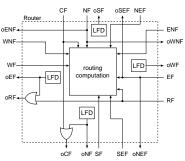

高ディペンダブル・高性能・高アダプタブルな完全非同期式オンチップネットワークを開発した. ディペンダビリティ性としては、単一ルータあるいは単一リンク故障に耐えられるルーティングアルゴリズムを有す(図 4.1-1).

図 4.1-1 故障ノードを避けるディペンダブル・ルーティング・アルゴリズムの開発

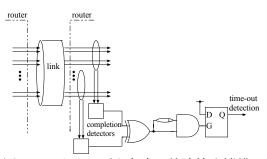

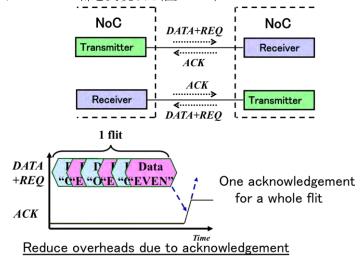

このようなディペンダブル・ルーティング・アルゴリズムを実現するため、フォールト検出機構として図4.1-2に示すタイムアウト方式のフォールト検出機構などを開発した。また、得られたフォールト情報は、図4.1-3に示す回路を用いて、隣接ルータ及び行方向・列方向に伝播させるだけで実現できることを示した。

図 4.1-2 タイムアウト方式の故障検出機構

図 4.1-3 フォールト情報伝播機構

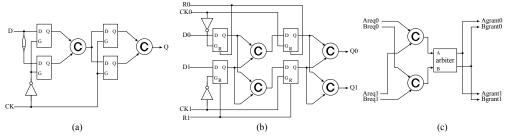

また、制御部二重化によりソフトエラー耐性も持つ. ソフトエラーなどの一過性故障をマスクする方式として、図 4.1-4 (a)に示すような遅延素子を用いてデータ信号(あるいはタイミング信号)を遅らせる方式が提案されているが、非同期式実装において要求一応答ハンドシェイクを制御する回路はデータパスと比較して回路量が小さいため、制御回路全体の二重化を行い、図 4.1-4 (b)に示す様に遅延素子を用いず二重化した信号の比較を行う方式とした。また、このような非同期式回路の二重化では排他制御を行うアービタの実装が困難であることを明らかにし、実装方式を検討した(図 4.1-4 (c)).

図 4.1-4 制御部二重化によるソフトエラー高耐性非同期式回路実装

さらに、設計・実装したオンチップネットワークは完全非同期式回路実現であり、遅延変動や 劣化故障に対して高い耐性を持つ。高性能性としては、リンク部に休止相の不要な2線式符号(Level Encoded Dual Rail: LEDR 符号)を用い(図 4.1-5)、ルータ部にも休止相の不要な 2相式実現を採用している。

図 4.1-5 LEDR 符号によるリンク部実装

アダプタビリティ性としては, 仮想チャネル機構により, トラフィックの混雑部分を自律的に避けてパスを選択するルーティングアルゴリズムを用いている.

#### ② 創造性

オンチップネットワークのディペンダビリティを,回路レベル,および,ルーティングアルゴリズムレベルの両面から向上させている点に創造性がある.

プロセスばらつきや環境変化による遅延変動はプロセステクノロジが進むにつれ大きくなり、 従来のグローバルクロックを分配する同期式回路では、それらに対する耐性を持たせるため には、大きなマージンが必要であった。また、NBTI (Negative Bias Temperature Instability) 等の劣化故障に対しても弱い。非同期式回路実現されたオンチップネットワークでは、正常 時の性能を低下させることなく、遅延が大きくなっても正しい機能を維持し続けることができ る。なお、遅延の増加に伴い処理速度は低下するが、機能として誤ることはないので、アプリ ケーションレベルの制御周期に影響を与えるほど大きな遅延となるまでに検出し、警告する ことが容易である。

また、リンクやルータの故障発生時には、ルーティングアルゴリズムレベルの耐故障性により、オンラインで検出・迂回を行うため、故障が発生した瞬間に伝送されていた1パケットのみが影響を受けるのみであり、後続のパケットは直ちに別経路で目的地まで正しく伝送される. 影響を受けたパケットがネットワーク上に留まると、他のパケットの伝送に悪影響を与える可能性があるが、提案手法では、そのようなパケットを直ちに破棄する手法も実現されている. 一方、破棄されたパケットは、タスクレベルの高信頼化手法である、改良 Pair&Swap 方式(4.2参照)において検出され、一時的三重化実行が行われるため、多数決により正しい計算結果を得ることができ、処理を正常に続行できる.

#### ③ 有用性

同期式オンチップネットワークと比較すると、同じような遅延変動・劣化故障耐性を考えた場合、非同期式オンチップネットワークにおいては、正常時の性能を落とす必要がない点、および、遅延が大きくなっても機能としての正しさを維持できる点が優れている。なお、符号化や制御部2重化による回路量増加は存在するが、ルータ自体の面積が計算コア等に比べて小さいため、大きな問題とはならない。

一方,本方式が採用しているオンラインのディペンダブルルーティングアルゴリズムは,オフラインの方式(テストフェーズを設け,テスト用パケット等を流して故障要素を検出する方式)に比べて,耐えられる故障要素数が小さいが,本研究のようにリアルタイム性が重要な車載制御では,オンライン方式が必須である.提案手法では,前述の通り,ルータに図4.1-3 に示すような少数の信号線を追加し,故障情報を伝搬させる機構を設け,その故障情報を利用することで,無故障時および故障発生時のオーバヘッドを削減している.

# ④ 優位比較

非同期式オンチップネットワークは、LETI等により実チップが製造されている。本研究の試作チップは、プロセスの差を考慮しても、ルータレイテンシはやや大きい。しかし、これはディペンダブルルーティングやアダプタブルルーティング実装のためであり、単純にルータレイテンシを比較することは意味がない。逆に、ディペンダビリティを高める工夫をした非同期式オンチップネットワークは、本研究が初めてと言える。

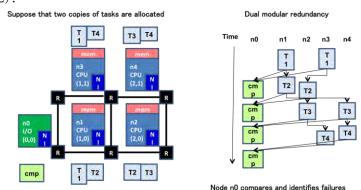

- 4.2 静的冗長タスク割り当てと動的ペア再構成に基づくタスク実行の高信頼化(NII グループ・弘前大グループ)

- (1)研究実施内容及び成果

#### ① 実施方法•実施内容

マルチプロセッサコアシステムにおけるプロセッサレベルのフォールトトレラント技術を開発

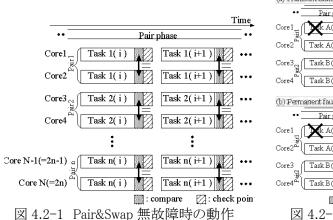

した. CMP(チップマルチプロセッサ)などに代表されるマルチプロセッサコアでは、各プロセッサコアは独立して動作することが可能であり、冗長化による高信頼化を行うことが出来る. 一方で、CMP は故障が発生してもコア単体の修理は出来ないことから、非修理系として扱う必要があり、システムとして漸次縮退を行う必要がある. そこで、プロセスの二重化と結果比較による誤り検出と、プロセスペア対の交換による故障判定と動的再構成を行う故障診断手法 Pair&Swap を提案した.

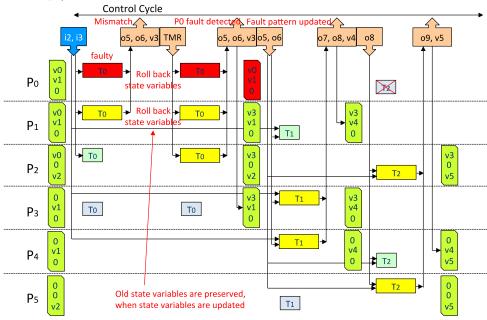

Pair&Swap では、予め静的にタスクを冗長に割り当てておき、与えられたタスクの2つのコピーが2つのプロセッサコアのペア上で実行され、その結果が比較される(図 4.2-1).

Corel G Task A(i) Task A(i) Task A(i+1) Task B(i+1) Task A(i) Core3<sub>⊙</sub> Task B(i) Task B(i+1) ask B(i+2) Core4 Task B(i) Task A(i+1) (b) Permanent fault case Pair phase Swap phase Pair phase Core1 Task A(i) Task A(i) faulty core Task B(i+1) Core2 Task A(i) Core3 Task B(i) Task B(i+1) Task B(i) Task A(i) 🏢 : compare 🔯 : check point 🔳 : rollback (load CP)

図 4.2-2 Pair&Swap 故障発生時の動作

比較結果が不一致となりエラーが検出された場合、ペアの一方のプロセッサコアを他のペアの片方のプロセッサコアと交換し、不一致のタスクを最新のチェックポイントから再実行して再度演算結果を比較することで、発生した故障が一過性故障(過渡故障)か永久故障かを判定する(図 4.2-2). 一過性故障の場合、ペアを交換して再実行した結果は一致するため、そのまま処理を継続させることが出来る(図 4.2-2 上). 一方、発生した故障が永久故障の場合、2 回とも不一致となったタスクペアに属するプロセッサコアに永久故障が生じたと判定できるため、同定した故障したプロセッサコアを隔離し、残りのプロセッサコアを用いてタスクの再割当を行う. これにより、漸次縮退を行うシステムを実現することが出来る.

# ② 創造性

故障モデルとしてシングルコア故障を仮定した場合,故障を完全にマスクする方式として,TMR(Triple Modular Redundancy)による三重化実行と多数決による故障検出と結果判定を行う方式がある.しかしながら,VLSI の故障率は十分小さく,常に三重化実行を行うのは電力などの面でオーバヘッドが大きい.そこで,通常時は二重化による結果比較で故障を検出し,故障が検出された時だけ故障判定を行う方式とした.

ディペンダブル NoC プラットフォーム向けの改良として、センサ・アクチュエータ等を管理する I/O コアがタスクの動的割り当てと演算結果の比較を担当し、故障判定に一時的な三重化を行う改良 Pair&Swap 手法を提案した. 比較において不一致が生じた場合は、3つのプロセッサコアを用いて再実行し、故障プロセッサコアの同定と、ペア再構成を行う. この様子を図 4.2-3 に示す. 一方、ソフトエラー等の一過性故障の場合は、3 重化実行において不一致は生じないため、もとのペアのままでタスク実行を続ける.

また,タスクが内部状態を持つ場合にはペア以外にスタンバイコアを設定し,内部状態情報をスタンバイコアに保持させることにより,故障判定及び再構成を行うことが出来るアルゴリズムを開発した.

#### ③ 有用性

プロセッサレベルのフォールトトレラント技術として、従来手法としてあげられる静的三重化 (TMR: Triple Module Redundancy) 方式と比較して、二重実行で結果を比較して不一致の場合のみ故障判定動作に移る方式をとることで、通常動作時の消費電力を抑えることが出来る。また、スレッドレベルの並列性があるアプリケーションでは複数のタスクを同時実行させることができ、不一致ペアとほかのペアとの間でパートナーを交換することで故障判定を行うことができる本手法は、故障判定に伴うオーバヘッドを小さくすることが出来る。

また、本研究で対象としているエンジン制御などのリアルタイム制約に余裕があるアプリケーションでは、故障判定に一時的な三重化を行う方式をとり、その判定を時間制約内に行うことが出来れば故障判定および永久故障時の動的再割当に伴うオーバヘッドを完全にマスクすることが出来る.

さらに、二重化実行等を隠蔽する API 等を整備することにより、使用者が意識せずに漸次縮退を実現するシステムを実現することが出来る. また、漸次縮退したことを通知する機構を設けることで、使用者はシステムの状態を知ることが出来るため、メンテナンスに関する判断を容易に行うことが出来る.

#### ④ 優位比較

プロセスの二重化と結果比較に関して、ソフトウェアレベルで同様の手順を用いて故障判定を行う手法としてmSWATと呼ばれる手法が提案されている。 ディペンダブル NoC プラットフォーム向けにハードウェアを意識した実装を行うことができ、API として提供することが出来る点が本手法の優位点である.

また、CMP を対象としたプロセッサレベルのフォールトトレラント技術として、DCC(Dynamic Core Coupling)と呼ばれる方式が提案されている。DCC では、本提案方式と同様に複数のペア対で同時にタスクを実行させ、その結果を比較する。不一致だった場合、予備のスペアコアを用いて一時的に TMR を組んで故障判定を行う。DCC はバスアーキテクチャを想定しており、スペアコアではどのタスクでも実行できる。本提案方式では、ディペンダブル NoC プラットフォーム向けに、各コアが持つローカルなメモリに予め冗長的にタスクを割り当てる方式を提案しており、メモリ量が制約された組み込みシステムに適した故障判定・動的再割り当て方式を提案した。

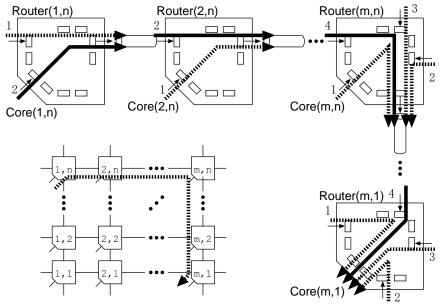

- 4.3 マルチチップ NoC とそのディペンダブルルーティングアルゴリズム(NII グループ・弘前大グループ)

- (1)研究実施内容及び成果

#### ① 実施方法•実施内容

オンチップネットワークを有する複数の LSI チップをチップ間リンクで接続し、オンチップネットワークをシームレスにマルチチップネットワークに拡張できる、マルチチップ NoC の概念を提案した。また、LSI パッケージのピン数に制約がある場合、チップ間リンクの数と1リンク当たりのビット幅はトレードオフの関係になる。2×2の2次元メッシュトポロジを持つベースチップを対象に、車載制御アプリケーションを想定した場合、マルチチップネットワークが実現できる拡張性を考慮すると、チップ当たり5つのチップ間リンクを持つのが有効であることを示した(図 4.3-1(a))。同図(b)、(c)には2チップ構成、および、4チップ構成を示す。このように4チップ構成までは、2次元メッシュ構成を取れるが、それ以上の構成の場合、クラスタ間の接続数が不足し、完全な2次元メッシュを取れない。図 4.3-1(d)に8チップ構成を示す。そこで、不足するリンクを故障リンクと同等に扱い、ルーティングアルゴリズムによりそれらを迂回する手法を提案し、従来手法に基づく方法と比較した。さらに、この方式を適用した、2×2のベースチップを設計・試作した(図 4.3-2)。

# ② 創造性

チップをつなげてオンチップネットワークをマルチチップに拡張するというアイデアは単純であるが、実現の際にはLSIパッケージのピン数制約とチップ間通信バンド幅のトレードオフという問題がある。このため、トポロジに制約を持たせ、ピン数を制限することでバンド幅を確保しつつ、ルーティングアルゴリズムの工夫により、接続可能性を維持するという方針を取った。アプリケーションにもよるが、通信量が多いタスクをクラスタ内に割り当て可能な場合は、性能を落とすことなく、高い拡張性や耐チップ故障性を得られる。このアイデアは特許出願済みである。

#### ③ 有用性

NoC ベースの統合型 ECU では、スケーラブルかつフレキシブルであるという特徴から、冗長性や負荷分散を実現しやすいという長所を持つ.しかし、カーメーカ等ではチップ全体が故障する可能性を危惧することから、例えチップ内に冗長性を有しても、一つのチップからなる NoC ベースの統合型 ECU は受け入れ難いようである.マルチチップ NoC では、安価なベースチップを必要な数だけ接続することで、任意の規模のシステムを自由に構成できる.また、チップレベルの冗長性も容易に実現できる.チップ内のオンチップネットワークがシームレスにマルチチップネットワークに拡張されるため、ユーザはチップの境界を意識する必要はない.LSI パッケージのピン数の制約から、チップ間リンクは部分的にシリアル化する必要があるが、高速かつ高効率チップ間通信方式(4.9参照)を用いることにより、チップを跨

ぐことによる効率低下を防げる.

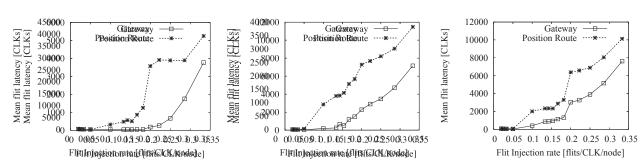

# ④ 優位比較

クラスタ間において不足するリンクを故障リンクとして扱い、ルーティングアルゴリズムにより迂回する方法は、ルーティングテーブル等を書き換えることによるオフラインアルゴリズムでは難しくないが、本研究のように故障に対してリアルタイムに対応する必要があるアプリケーションの場合、採用しにくい、一方、オンラインアルゴリズムでこのような問題に適用出来るものとして[4-1]があるが、2×2のベースチップを想定した場合、提案手法と比較した場合、図4.3-3 に示すように提案手法が、多くの場合[4-1]の手法より高効率であることがわかっている. なお、図中、「Gateway」が提案手法であり、「Position Route」が[4-1]の手法である. また、横軸はネットワークへのパケットの投入量、縦軸はパケットの到着までに要する平均時間を表している. その他、車載アプリケーションにおいては、上述したように、安いコストでチップレベル冗長性を実現できることから、単一のチップを想定した NoC ベースの統合型 ECU よりも優れている.

Fig. 17. Mean flit latency when upper-rigo chip of Clusto 年 知识的 Lip orm-cluster, right pseudo-ECU).

inter-cluster  $(0 \rightarrow 1)$ inter-cluster  $(1 \rightarrow 0)$

制駆動力,機械ブレーキ,後輪操舵量を制御するもめである(図 4.4-1)132.4

: indicates 7-8% of total flit counts.

(0,0)

Fig. 19. Heavy traffic links of Position-Route method in the fault-free and pseudo-ECU traffic case.

of inter-cluster links using different types of base chips as well as more general inter-cluster NoC topologies is one of our future work.

#### **ACKNOWLEDGMENT**

We'd like to thank Dr. Yusuke Fukushima for helping us understand their algorithm. This work is supported by CREST (Core Research for Evolutional Science and Technology) of JST(Japan Science and Technology Agency). This work is also supported partially by VLSI Design and Education

[3] T. Yoneda, M. Imai, N. Onizawa, A. Matsumoto, and T. Hanyu. Multi-chip NoCs for automotive applications. To appear in Proc. of PRDC2012.

5189.7

4222 4

899 9

4419.7

- [4] R. V. Boppana and S. Chalasani. Fault-tolerant wormhole routing algorithms for mesh networks. *IEEE Trans. Comput.*, 44(7):848–864, 1005

- 1995.

[5] S. Chalasani and R. V. Boppana. Communication in multicomputers with nonconvex faults. *IEEE Trans. Comput.*, 46(5):616–622, 1997.

- with nonconvex faults. *IEEE Trans. Comput.*, 46(5):616–622, 1997.

J Duato. A new theory of deadlock-free adaptive routing in wormhole networks. *IEEE Parallel and Distributed Syst.*, 4(12):1320–1331, 1993.

- P. H. Sui and S. D. Wang. Fault-tolerant wormhole routing algorithm for mesh networks. *IEEE Computers and Digital Techniques*, 147(1):9–14, 2000.

- [8] J Wu. A fault-tolerant and deadlock-free routing protocol in 2d meshes based on odd-even turn model. *IEEE Trans. Comput.*, 52(9):1154–1169, 2003.

- [9] J Zhou and F. C. M. Lau. Multi-phase minimal fault-tolerant wormhole routing in meshes. *Parallel Computing*, 30(3):423-442, 2004.

図 4.4-1 車両運動制御アルゴ II ズム車両運動制御概念図

次に、そのアプリケーションにおいて、 冗長化タスク割り当て(4.8参照)と改良 Pair & Swap 里高ケジャ音型ン電点者操名参照上高運動、Y850年動で電子が表して表行可能なラーボ告記を行っ ECUCPR 単前モ& Swent 委式 民の結果をは標準勤で述て対にとおり標準疏が、実際に真切方剣・実現 両挙動や偏差かり駆動のような静郷閣設言機械デンたき(1後輪操焼量は民標学動どの偏端複数が近ればコアに 制が多てられるが、通常時に一重実行されるタスクをアクティブタスク 一時的三重実行に使 ランドローラで各輪の制態動力ドルフ書きを作成するケルコッズムは一般的な均等分配法を用いる われるタスクをスタンバイタスク、その他をインアクティブタスクと呼ぶ、アクティブタスクを実行 している CPU コアが故障と診断された場合は、スタンバイタスクがアクティブタスクに、インア クティブタスクがスタンバイタスクに更新され、スタンバイタスクを保持している CPU コアが故 障と診断された場合には、インアクティブタスクの一つがスタンバイタスクと更新される。(2)ス タンバイタスクは,一時的三重実行が必要となったときに直ちに実行できるように,アクティブ タスクに送られる入力データも同時に受け取り、保持しておく. また、アクティブタスクがその 内部状態を更新した場合は、二つのアクティブタスクからの状態変数が比較され、不一致が 生じなかった場合にはそれを受け取り、自分の状態変数を更新する.(3)一時的三重実行時 は、アクティブタスクは再実行されるわけであるが、自分の状態変数は既に更新してしまって いるので、旧状態変数を保持しておき、それを用いて状態変数のロールバックを行う(4) (二重あるいは三重)実行結果を比較する場合は、タスクの最終出力だけでなく、状態変数 の値も比較対象とする. (5)タスクへの入力値の配布, タスクからの出力値・状態変数値の比 較,一時的三重実行の起動,その結果の多数決等は外部 IO コアが行う. これらの実行例を 図 4.4-2 に示す.

図 4.4-2 改良 Pair & Swap の実行例

この詳細設計を実装し、FPGA を用いたプロトタイプシステムにより、実際にHILS上で動作させ、CPU コアが順次故障していっても、正常に統合車体制御が行われることを実証した.

#### ② 創造性

改良 Pair & Swap の考え方はシンプルであるが、効率よく一時的三重実行を実現するには工夫が必要であった。上記のように、スタンバイタスクは常に入力、および、アクティブタスクが更新する状態変数の値を受け取っているため、一時的三重実行は外部 IO コアからの短い(データを伴わない)パケットにより起動できる。一方、パケットが外部 IO コアに集中することによるオーバヘッドが懸念されるが、外部 IO コアをハードウェアで実現することを検討中である。そのために、外部 IO には故障状況を表す状態テーブル等以外、データを保持する必要がないように設計した。同時に、外部 IO の故障を考慮して、外部 IO の二重化の実装も進めている。なお、パケット集中によるネットワークの混雑については、CPU コアに対してルータは十分早いため、外部 IO コアが (ハードウェア化などで)十分早くパケットを受け取れれば、問題にならないレベルとなると考える。

#### ③ 有用性

上記のアプリケーションは、ドライバの意図に基づいて四輪のトルク、制動力、および後輪の操舵を最適に制御するもので、その機能の喪失はスピン等のドライバの命に関わる事故を招きかねない。そのため、CPUコアが次々と故障していっても、機能を維持し続ける、改良Pair & Swap 方式の統合型 ECU の実証に適している。また、このアプリケーションは評価キットに付属させ、評価キットのユーザが手軽に高度なアプリケーションを高信頼実行して、提案プラットフォームを試す最初のステップとなるようにしている。

#### ④ 優位比較

改良 Pair & Swap 方式を実際に実装し、高度なアプリケーションを HIL シミュレータ上で実時間実行でき、また、故障 CPU に対する処理も実時間で行えていることから、実証という成果は大きいと考える. 再構成を伴わない完全同期二重実行(しばしばロックステップ実行と呼ばれる)は様々なところで既に使われているが、故障の蓄積に耐え、かつ、コピーの数を変更することでその耐性を自由に設定出来る方式は、実証レベルで用いられている例はないと考える.

# 4.5 評価キットの開発(NIIグループ)

(1)研究実施内容及び成果

# ① 実施方法・実施内容

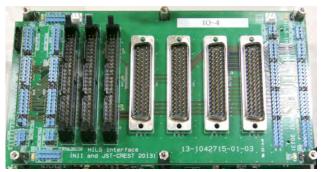

ハードウェアとして、V850E プロセッサ4個を2×2のオンチップネットワークで接続したベースチップを4個搭載して、4×4までのマルチチップネットワークを構築可能な ASIC 版プラットフォーム(図 4.5-1)、および、大規模 FPGA(Vertex 7 XC7VX690T)により任意のトポロジを試せる FPGA 版プラットフォーム(図 4.5-2)を開発した。これらの2つのバージョンは、ボード上の DIP スイッチにより切り替えて使用可能である。 さらに、HIL シミュレーションシステムとのインターフェースボード(図 4.5-3)も開発しており、HIL シミュレーションシステムを直接接続できる。

図 4.5-1 ASIC 版プラットフォーム

図 4.5-2 FPGA 版プラットフォーム

図 4.5-3 HILS インターフェース

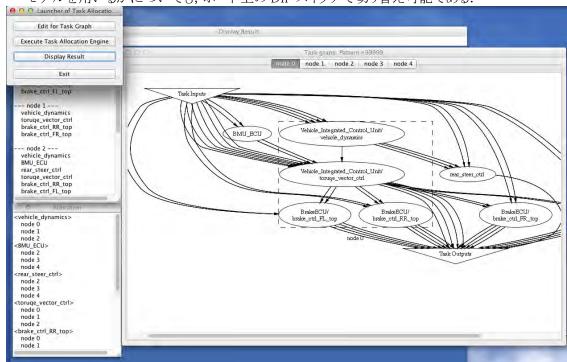

アプリケーションとしては、上記の四輪独立制御に基づく統合車体制御システムが直ちに動作するように、予めタスク分割を行い、コード生成をしたものを用意している。また、4.8で開発した冗長タスク割り当てアルゴリズムを用いた、ソフトウェア支援ツールを開発し、評価キットに付属している(図 4.5-4)。このツールは、ECU 設計者により書かれた単一バージョンのSimulink プログラムを入力し、そのデータフローグラフを表示しながらタスクの粒度を決める支援を行う。そのほか、タスクごとのコード量、実行時間の見積もり、必要なコピー数等をGUI により入力することができる。その後、冗長タスク割り当てアルゴリズムを実行することで、改良 Pair & Swap アルゴリズムを適用するためのコードを生成できる。

さらに、HIL シミュレーション環境を持たないユーザが、手軽に四輪独立制御に基づく統合 車体制御システムを試せるように、簡易プラントモデルを開発した。これは、精度を落として 計算量を減らした車体モデルであり、FPGA 上のソフトプロセッサにより、1ms のステップレー トで車体の挙動を計算できる。本物の HIL シミュレーションシステムを用いるか、簡易プラント モデルを用いるかについても、ボード上の DIP スイッチで切り替え可能である。

図 4.5-4 ソフトウェア支援ツールのスクリーンショット

#### ② 創造性

4チップ構成までのマルチチップ NoC を試せる ASIC 版では、チップ故障に対する耐性や、完全非同期式オンチップネットワークの実現可能性など、提案手法のすべての機能を実証している.一方、FPGA 版では、さらに大きな構成やメッシュ以外のトポロジも試すことができる.また、ECUメーカと開発した本格的なアプリケーションが試せること、および、HIL シミュレーションシステムがなくても機能を確認できる簡易プラントモデルが付属していることなどが、他の同様なキットに対して新しい.

# ③ 有用性

本キットでは、第一段階として、付属のアプリケーションを改良 Pair & Swap 方式で高信頼実行する様子を確認できる。この段階では、タスクの粒度を変えて並列度を変えたり、タスクのコピー数を変えて CPU コア故障に対する耐性を確認できる。第二段階では、付属のアプリケーションを変更して実行までのフローを確認することで、アプリケーション開発の仕組みを試せる。最後に、ユーザが独自のアプリケーションを開発し、評価キット上で高信頼実行の実証が行える。 車体モデルに関するアプリケーションの場合、簡易プラントモデルが付属しているので、HIL シミュレーションシステムを用意することなく、容易に試すことができる。

# ④ 優位比較

ソフトウェア開発支援システムに加えて、実アプリケーションとそのための簡易プラントモデルを付属した開発キットは、他にないと考える. 現段階では、コード生成の部分の自動化割合はまだ低いが、今後スクリプトの充実等により、操作性を向上させる予定である.

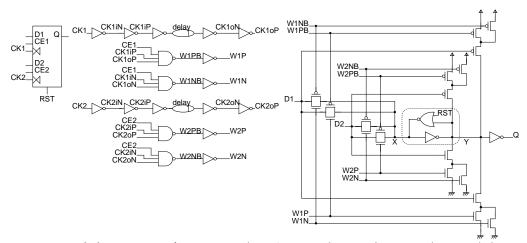

4.6 マルチクロック・デュアルエッジトリガ・フリップフロップの開発(弘前大・NII グループ) (1)研究実施内容及び成果

# ① 実施方法・実施内容

非同期式回路におけるレジスタ間データ転送は要求一応答ハンドシェイクに基づいて動作する.このハンドシェイクを規定するプロトコルには、主に4相(4サイクル)ハンドシェイクプロトコルと2相(2サイクル)ハンドシェイクプロトコルがある.回路の初期化が必要な4相ハンドシェイクプロトコルに対し、2相ハンドシェイクプロトコルは初期化が不要であり、高速な回路を実現しうる.一方、4相ハンドシェイク回路はレベル論理回路であり制御回路の実現が容易なことに対して、2相ハンドシェイク回路は遷移論理回路であり、立ち上がりエッジ、立ち下がりエッジ双方が意味を持つように回路を実現しなければならず、制御回路の実現が困難な場合があった.そこで、2相ハンドシェイク信号を直接扱うことの出来る、マルチクロック・デュアルエッジトリガ・フリップフロップを開発した.

新規開発したダブルクロック・デュアルエッジトリガ・フリップフロップの真理値表を図 4.6-1 に示し、トランジスタレベル回路実現を図 4.6-2 に示す。

| D1               | CE1 | CK1      | D2 | CE2 | CK2      | RST | $Q_n$        |

|------------------|-----|----------|----|-----|----------|-----|--------------|

| a                | 1   | <b>↑</b> | X  | X   | 0/1      | 0   | a            |

| $\boldsymbol{a}$ | 1   | +        | X  | X   | 0/1      | 0   | a            |

| X                | 1   | 0/1      | X  | X   | 0/1      | 0   | $Q_{n-1}$    |

| $\mathbf{X}$     | 0   | X        | X  | X   | 0/1      | 0   | $Q_{n-1}$    |

| X                | X   | 0/1      | b  | 1   | <b>↑</b> | 0   | ь            |

| X                | X   | 0/1      | b  | 1   | +        | 0   | ь            |

| X                | X   | 0/1      | X  | 1   | 0/1      | 0   | $Q_{n-1}$    |

| X                | X   | 0/1      | X  | 0   | X        | 0   | $Q_{n-1}$    |

| X                | X   | X        | X  | X   | X        | 1   | 0            |

| X                | 1   | 1/1      | X  | 1   | 1/4      | 0   | (prohibited) |

図 4.6-1 ダブルクロック・デュアルエッジトリガ・フリップフロップの真理値表

図 4.6-2 ダブルクロック・デュアルエッジトリガ・フリップフロップのトランジスタ回路実現

上図において、CE1、CE2 は各クロック信号のイネーブル入力を表し、イネーブル信号が1のとき、クロック信号 CK1、CK2 の立ち上がりエッジ・立ち下がりエッジの両方で各データ入力 D1、D2 の値が記憶される. また、真理値表の最後に示す通り、イネーブル信号が両方とも1で、2つのクロック信号のエッジが重なることは禁止とする.

また、この素子のバリエーションとして、クロック数を増やしたものや、クロック毎に値を記憶するエッジを変更したものも容易に設計することが出来る。そこで、130nm プロセステクノロジを用いてこれらの素子をダブルハイト・スタンダードセルとして設計した。さらにそれらを用い

てディペンダブル NoC プラットフォームにおける非同期式オンチップネットワークルータを設計・実装し、その有効性を示した.

# ② 創造性

複数の信号の立ち上がりエッジ・立ち下がりエッジに同期してそれぞれデータ入力を取り 込むフリップフロップを新たに提案した。

トランジスタレベルの実装として、ラッチの数は一つとし、トランスファーゲートによりデータ入力信号の書き込みを制御する回路構成とすることで、高速かつ安定した値の更新を行うことが出来るようにした。

また、このフリップフロップは非同期式回路実現だけでは無く、同期式回路において複数のクロック信号を用いる場合にも適用することが出来る。 例えば、90 度位相の異なる2 つのクロック信号を用いる場合、 *X* [GHz]の周波数のクロックを用いれば *4X* [GHz]でのラッチ動作を実現することが出来る。

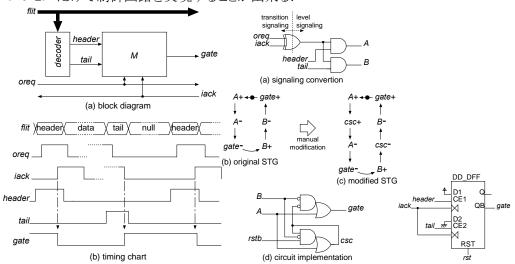

# ③ 有用性

提案マルチクロック・デュアルエッジトリガ・フリップフロップを用いることにより、2 相ハンドシェイクプロトコルに基づく非同期式回路を容易に実現することが出来る. 例として、図 4.6-3 に示す仕様を持った 2 相ハンドシェイクプロトコルに基づく制御回路を設計する場合、従来方式では図4.6-4左に示すように、遷移論理信号(transition signaling)である oreq, iack 信号を XOR ゲートによりレベル論理信号(level signaling)に変更した後、STG(Signal Transition Graph)と呼ばれグラフ表現を用いて仕様を記述し、PETRIFY 等により論理合成しなければならなかった. それに対して提案フリップフロップを用いることで、図 4.6-4 右に示すように一つのセルだけで制御回路を実現することが出来る.

図 4.6-3 制御回路 M の動作仕様

図 4.6-4 従来設計法による回路実現と提案 FF による回路実現

PTM(Predictive Technology Model)デバイスパラメータを用いて図 4.6-4 に示す各回路の遅延と消費エネルギーを比較した結果を表 4.6 に示す. 提案フリップフロップを用いることにより、スタンダードセルを用いた構成よりも高速なシステムを実現することが出来ることが確認できる. 一方、消費エネルギーは約3倍となっている. しかしながら、制御回路はデータパスと比較して回路量が小さく、システム全体で考えればほとんど影響を及ぼさないと考えられる.

#### Delays of circuit M.

| v 1.199.7. v        | Best<br>[ps] | Typical [ps] | Worst<br>[ps] | Average energy<br>@Typical [fJ] |

|---------------------|--------------|--------------|---------------|---------------------------------|

| Standard cell based | 83.4         | 114          | 215           | 12.7                            |

| DD-DFF based        | 80.0         | 107          | 199           | 37.4                            |

表 4.6 回路 M の遅延と消費エネルギー

#### ④ 優位比較

クロック信号が1本の場合,立ち上がりエッジ・立ち下がりエッジ双方で値を記憶するフリップフロップとしては様々な回路構成が提案されており、主に高速メモリとの通信で使用されている.しかしながら、従来手法では複数のクロック信号に対応したものは無く、新しい記憶素子である.

4.7 オンチップネットワークにおける最大レイテンシのモデル化と評価(弘前大・NII グループ) (1)研究実施内容及び成果

# ① 実施方法・実施内容

NoC ノード間の通信にかかるレイテンシは、オンチップネットワーク上のパケットの過密具合に影響を受ける。また、本研究で採用しているワームホールルーティングでは、あるパスを占有したパケットが通過するまで、他のパケットはそのパスを使用することは出来ない。これに対し、従来はシミュレーションにより、NoC ノード間の通信はリアルタイム制約より十分速いことを確認していたが、最悪ケースを想定した場合、レイテンシがどのようになるのか理論的なモデル化がなされておらず、リアルタイム性を理論的に保証することが出来ていなかった。そこで、NoC ノード間の最悪レイテンシをモデル化(定式化)してその評価を行った。図4.7-1にXYルーティングアルゴリズムにおける待ち合わせを行う最大数のモデルを示す。図に示すように、横方向の遷移の場合、阻害パケットの数は最大3となり。各ルータで最大阻害数となる場合が最悪ケースとなる。

図 4.7-1 XY ルーティングアルゴリズムにおける最大待ち合わせ数

# ② 創造性

あるパケットに着目した場合、そのパケットの移動を阻害するパケットはルーティングアルゴ

リズムに応じてその数が異なり、また、阻害パケット自体も他のパケットによりその移動が阻害される可能性がある. 従って、パケットサイズを考慮した再帰的な待ち時間をモデル化した. ルーティングアルゴリズムとして、いずれもデッドロックフリーな、XY ルーティング、ネガティブ・ファースト・ルーティングを仮定し、さらにその後に追加として昨年までに開発したディペンダブル・ルーティングアルゴリズムを仮定してそれぞれモデル化と評価を行った.

また, クロック信号に基づいて動作する同期式回路だけでは無く, 非同期式回路でも適用できるように, クロックサイクルではなく, ルータの各ステージの遅延を用いた汎用的なモデル化を行った.

# ③ 有用性

従来はシミュレーションによる評価のみでリアルタイム性の保証を行ってきたが、上記のモデル化により最悪レイテンシを求めることが出来るため、NoC 構成のシステムはリアルタイムシステムにも適用できることを理論的に保証することが出来る。また、シミュレーションでは完全に再現することが難しい最悪ケースを想定することが出来るため、設計したシステムのリアルタイム性に関するタイミング余裕の評価も行うことが出来る。

#### ④ 優位比較

NoC ノード間の通信レイテンシに関して、システム全体の処理量とデータの供給量のモデル化により、その差分の最大値で最悪遅延のモデル化を行う手法が提案されている. しかしながら、この方式では最悪の状況は表しておらず、理論的最悪値とは言えない. 理論的に最悪遅延のモデル化を行ったものはない.

- 4.8 タスクの多重スケジューリング・多重割り当て手法(会津大グループ)

- (1)研究実施内容及び成果

## ① 実施方法・実施内容

最近の車載アプリケーション開発においては、Simulink を用いてモデリングを行い、シミュレーションを通じて動作検証や評価を行う。その後、自動コード生成ツールを用いて、ECU (コア)にアプリケーションをマッピングする。しかしながら、Simulink モデルの各部品(ここではタスクと呼ぶ)をいつどのタイミングで NoC の各コアで実行させるかを決めるツールがないため、実際は人手による作業が大きい、そこで、Simulink モデルの各タスクを NoC の各コアにマッピングすることを想定したタスクスケジューリング・割り当てツールを開発した(図4.8-1)。

図 4.8-1 開発したツールセット

また、NoC のあるコアが故障しても、残りのコアで動作を継続するために、タスクの多重割り当て手法を提案した。タスクの多重割り当ては、メモリ制約のもと、タスクのコピーを異なるコアに割り当てていく。そのため、あるコアが故障したとしても、そのコアに入っているタスクと同一のタスクが残りのコアに入っていれば、動作を継続することが可能である。また、タスクの多重割り当ては、弘前大グループが中心となって考えた Pair&Swap を実現できるよう、あらかじめ列挙した故障パターンごとにタスクの多重スケジューリングを行うことによって決めていく(図 4-8-2)。

図 4.8-2 二重化実行を考慮したマルチタスクスケジューリング

# ② 創造性

NoC を想定したタスクスケジューリング・割り当て手法は様々なところで研究がおこなわれているが、許容できるコアの故障数を入力とし、故障パターン毎にタスクスケジューリングを行い、タスクの割り当てを決めていく手法は今までの調査で見当たらなかった。そういった意味で本手法は創造的である.

# ③ 有用性

提案手法は、アプリケーションモデルとNoCモデルのほかに、メモリ制約、I/O数、アプリケーションの時間制約を入力とし、タスクの多重割り当てを行っていく、そのため、実際のコアのメモリサイズや I/O 数などを考慮しながらタスクの割り当てを決めていくことはもちろんのこ

と、制約を変えることによって、様々なケースを探索することが可能である。また、タスクの実行時間、タスク間の通信時間、および故障検出のために同一タスクを異なるコアで実行した結果の比較時間を基にタスクスケジューリングを行うので、実際の動作に近いスケジューリングが得られ、時間制約を満足するようなタスク割り当てを得ることができる。そのほかにも、開発したツールには NoC モデルをパラメータとして与えているので、パラメータの与え方を変えれば異なるアーキテクチャモデルにも拡張することが可能である。

# ④ 優位比較

NoC においてコアの故障を想定したタスク割り当て手法はこれまでにもいくつか提案がされてきた。これらの手法は、故障が起こった際にタスクの再割り当てを行う。そのため、故障が起こったとしても残りのコアで動作をさせることが可能である。しかしながら、実際に故障が起こった時にタスク割り当てアルゴリズムを動作させ、その後コードを割り当てるという手法はそれなりの時間オーバヘッドがあり、時間制約がクリティカルなアプリケーションには向いていないと思われる。こうした手法と比較して、提案手法は、あらかじめ許容できる故障コア数の下、想定されるコアの故障パターンを全列挙して、各パターンに対するタスクの多重スケジューリングから、タスクの多重割り当てを決めていく。そのため、故障が起こったとしてもタスク割り当てを再度行う必要がないため、時間オーバヘッドが小さく、時間制約がクリティカルなアプリケーションに向いていると思われる。

# 4.9 高効率チップ間通信技術の開発(東北大グループ)

# (1)研究実施内容及び成果

#### 1 実施方法・実施内容

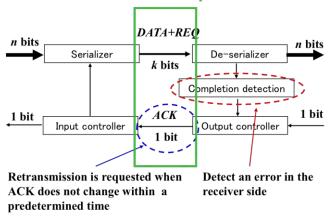

チップ間高速シリアルデータ転送を実現するための非同期式電流モード回路を実現し、その有用性を 130nm CMOS プロセスを用いた試作チップの設計,評価を通して有用性を明らかにした.

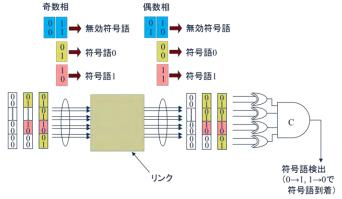

# 2 創造性

まず、LEDR (level-encoded dual-rail) 符号を活用したバーストモード転送を採用することで、チップ間ハンドシェイクの回数を極力削減した.また、電流モードシングルトラック方式を考案し、①少ない配線数で、②高い電流駆動能力を有し、かつ③効率的なパワーゲーティング機能を組み込むことで、高速性、低消費電力性、並びに瞬時停止/起動機能を有するチップ間インターフェース部を実現した(図 4.9-1).

4.9-1 電流モードシングルトラック方式による非同期式バーストモード通信

また, バーストモード転送が正しく行われなかった場合の再送方式についても検討し, 規定数のデータが受信されなかった場合に送信側に再送要求を出す機構についても考案した(図 4.9-2). これは, 前述の LEDR 符号が 1 ビット情報の転送毎に 2 線化された信号線の片方が必ず切り替わる性質を利用している.

#### **Current mode link implementation**

Reliable burst-mode communication by retransmission mechanism

図 4.9-2 バーストモード通信における再送方式

#### 3 有用性

非同期 NoC プラットフォーム, すなわち非同期 NoC チップ同士を複数接続した NiP (Networks-in-Package)による高機能システムでは, オフチップ通信部分のデータ転送速度がオンチップ通信のそれと比較して低速であるため, このオフチップ通信部がシステム性能のボトルネックとなり得る. この部分に, 十分な速度を達成する転送方式を導入することにより, 高いシステム性能を有する非同期 NoC プラットフォームを実現できる.

# 4 優位比較

チップ間転送を想定した非同期転送方式に関しては、いくつかの既存研究が存在する. 具体例としては、アメリカ・コーネル大学より QDI 方式に準拠したチップ間非同期転送方式が提案されている. しかし、これらの方式はハンドシェイクプロトコルに厳密に準拠した方式であるため、通信に必要なステップ数が多く、その結果としてデータ転送速度は低く押さえられる. また、同大学より 1-of-3 コードを用いた非同期バースト転送方式も提案されている. これでは、180nm CMOS プロセスにおいて 3Gbps のデータ転送速度を達成したと報告されており、データ誤送信時の再送方式についても言及している. しかし、評価時にデータ転送速度を大幅に劣化させる伝送路のパラメータが考慮されておらず、実装レベルのデータ転送速度は3Gbps に遠く及ばない上、消費電力が大きく非同期 NoC への適用は難しい. 我々が開発した方式は、130nm CMOS プロセスにおいて実装レベルで 2.8Gbps のデータ転送速度を達成すると共に、非同期 NoC への適用時の消費電力をアメリカ・コーネル大学で提案された手法に比べ約 1/1000 に削減するものである. なお、最先端の 22nm CMOS プロセスでは、約 30Gbps の転送速度が達成される見込みである.

# 4. 10 非同期制御に基づく低消費電力 Content Addressable Memory の構成(東北大グループ) (1)研究実施内容及び成果

# ① 実施方法・実施内容

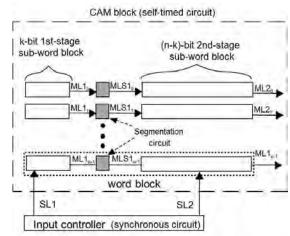

オンチップネットワークルータにおける高速なパケット(フリット)処理が実現可能な、非同期

制御に基づく低消費電力 Content Addressable Memory (CAM)を実現し、その有用性を 90nm CMOS プロセスを用いた試作チップの設計、評価を通して明らかにした.

#### ② 創造性

従来までの同期式 CAM はその速度がフリット長に依存することから、フリット長の増加に伴い、その速度が大幅に低下してしまい、低速な CAM を用いたルータによってチップ間、非同期データ転送速度が律速される問題が生じていた. 提案の CAM では非常にシンプルな前処理を実行することにより、フリット長に律速されない CAM 用高速探索アルゴリズム(Word Overlapped Search)を考案した. また、そのアルゴリズムのハードウェア実現に非同期制御方式を用いることで、従来までの同期式制御で問題となっているクロックに伴う消費電力を大幅に削減できる.

図 4.10-1 Word Overlapped Search (WOS) 手法に基づく CAM のブロック図

#### ③ 有用性

CAM を用いたオンチップルータは耐故障性を持つような複雑なルーティングアルゴリズムをハードウェア実現できる一方,その消費電力は通常の論理ゲート実現によるルータに比べて大きい. 提案 CAM は高並列処理により高速化が達成できるだけではなく,低い電源電圧時でも高速かつ低消費電力で動作ができるため,複雑なルーティングアルゴリズムを採用したオンチップルータを構成した場合でも,全体の消費電力を低く抑えることが可能となる.

## ④ 優位比較

CAM に関しては、いくつかの既存研究が存在する。直近の例としては、台湾・国立交通大学より、65nm CMOS プロセスを用いた検索時間 0.76ns、電力効率 0.11fJ/bit/search の高速かつ低消費電力な CAM が提案されている。我々が開発した CAM は、90nm CMOS プロセスを用いたにも関わらず、検索時間 0.53ns、電力効率 0.10fJ/bit/search とその性能を凌駕するものである。また、幅広い電源電圧に対応しているため、電源電圧を変更することにより、検索時間 0.25ns、電力効率 0.16fJ/bit/search の超高速 CAM や、検索時間 2.1ns、電力効率が 0.06fJ/bit/search の超高電力効率 CAM としての応用も可能である。

# 4.11 メニーコアプロセッサ評価環境の整備とハードウェアの販売(東工大グループ) (1)研究実施内容及び成果

# ① 実施方法・実施内容

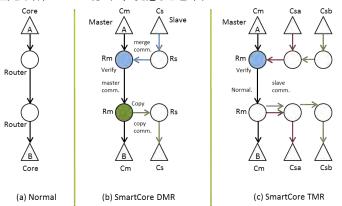

VLSI プロセッサの主流となるマルチコア/メニーコアプロセッサ, またマルチ VLSI チップ によるマルチモジュールシステムにおけるディペンダビリティを飛躍的に向上させるアーキテクチャとして, 超ディペンダビリティ支援の高機能 NoC ルータアーキテクチャおよびそれを活

用する SmartCore システムの研究開発をおこなった. 特に, これまでに開発してきた DMR システムをベースに, エラー検出後も実行を継続できる TMR システムの開発をおこなった. また, それらの成果の普及のために, 開発した FPGAシステムの製品化(東京エレクトロンデバイスから 2012 年 11 月に販売開始), ウェブサイトの充実に取り組んだ.

加えて、これまでに NII と弘前大学のグループを中心に開発をおこなってきた Pair & Swap 方式と東工大グループにて開発をおこなっている SmartCore システムの比較検討を実施し、それらの適用範囲を明確にした(現在、鋭意実施中).

図 4.11-1 SmartCore システムにおける通信の様子(中央は DMR,右は TMR)

図 4.11-2 販売中の FPGA システム ScalableCore

# ② 創造性

本研究は、従来の冗長性を利用して故障を検出するディペンダビリティ技術の発想を大幅に転換させ、来るべきメニーコアプロセッサおよびメニーモジュールシステムの環境を前提として、高機能ルータを核として、動的な要求変更に柔軟に対応する技術、すなわち超ディペンダビリティ支援の高機能 NoC ルータによるディペンダブル VLSI の実現を目指すものである.

従来のディペンダブルシステムで採用されてきた Lockstep の様な固定的な DMR ではなく, SmartCore システムには, 必要に応じて, 冗長実行なし, DMR, TMR を選択できる利点がある. また, 多重実行をおこなうノードの配置を動的に変更できるという利点がある. 加えて, 高機能 NoC ルータによるパケット複製とパケット比較の機能を用いることで, プロセッサコアなどの複雑なモジュールの設計に大幅な修正を施すことなく, 多重実行が可能となる利点がある.

# ③ 有用性

高機能 NoC ルータを用いて柔軟にディペンダビリティのレベルを変更できる SmartCore システムの性能およびハードウェアオーバヘッドの評価をおこない, その有用性を明らかにした.

開発してきた高機能ルータアーキテクチャにおける2重実行の仕組みを拡張し、現実的で

効果的な3 重実行の仕組みを開発した. SmartCore システムでは高機能ルータを用いてパケットの複製および比較をおこなうが, それを実現する現実的な NoC ルータアーキテクチャとそのハードウェア量を定量的に示すとともに, デッドロック回避が実現できることを示した.また, ソフトウェアシミュレーション環境に加えて, 開発した FPGA システムを用いて, 長時間のシステムレベルの評価を実施することで SmartCore システムの有用性を明らかにした.

# ④ 優位比較

汎用プロセッサにおけるディペンダビリティの向上技術としては、冗長性を利用して故障を検出する技術が提案されている。DIVA(Dynamic Implementation Verification Architecture)やIRI(Instruction Re-Issue)などの初期の技術は命令を2回実行して得られた結果を比較することで故障を検出する。素子特性のばらつきや最悪ケースに配慮した設計の限界から典型的ケースを指向して Razor やその改良型のカナリア・フロップフロップといった設計手法も提案されている。これらの技術は汎用プロセッサ内部に多重実行やタイミング調整の仕組みを構築する。

一方,我々は,従来の発想を大幅に転換させ,来るべきメニーコアプロセッサおよびメニーモジュールシステムの環境を前提として,高機能ルータを積極的に利用することで DMR, TMR を含む動的な要求変更に柔軟に対応する技術,すなわち超ディペンダビリティ支援の高機能 NoC ルータとそれを核とする SmartCore システムの実現を目指している.このような研究はこれまでに例がない.

# § 5 成果発表等

(1)原著論文発表 (国内(和文)誌 3件、国際(欧文)誌 46件)【国内】

- 1. 佐野伸太郎, 五十嵐俊哉, 吉瀬謙二: メッシュ/トーラス接続型スーパコンピュータに適した高性能タスク配置手法, 信学論, Vol. J96-D, No. 2, pp. 269-279, (2013. 2)

- 2. 松本敦,河野宇朗,鬼沢直哉,羽生貴弘:制御情報共有化に基づく非同期細粒度パワーゲーティング技術とそのオンチップルータへの応用,電子情報通信学会論文誌 C,vol.J96-C,no.5,pp.73-84,(2013.5)

- 3. 小林諒平, 吉瀬謙二: 多数の小容量 FPGA を用いたスケーラブルなステンシル 計算機, 情報処理学会論文誌コンピューティングシステム, Vol. 6, No. 4, pp. 1-13 (2013. 7)

# 【国際】

- 1. Frederic Beal, Tomohiro Yoneda, Chris Myers: Hazard Checking of Timed Asynchronous Circuits Revisited, Fundamenta Informaticae, Vol.88, No.4, pp.411-435, Bratislava, Slovak Republic, (Dec., 2008). DOI:10.1109/ACSD.2007.52

- 2. D. Walter, S. Little, C. Myers, N. Seegmiller, T. Yoneda: Verification of Analog/Mixed-Signal Circuits Using Symbolic Methods, IEEE Trans. of Computer-Aided Design of Integrated Circuits and Systems, Vol.27, No.12, pp. 2223-2235, (Dec., 2008). DOI:10.1109/TCAD.2008.2006159

- 3. Naoya Onizawa and Takahiro Hanyu: Robust Multiple-Valued Current-Mode Circuit Components Based on Adaptive Reference-Voltage Control, Proc. 39th IEEE International Symposium on Multiple-Valued Logic, Okinawa, Japan, (May, 2009). DOI:10.1109/ISMVL.2009.44

- 4. Yo Ohtake, Naoya Onizawa, and Takahiro Hanyu: High-Performance Asynchronous Intra-Chip Communication Link Based on a Multiple-Valued Current-Mode Single-Track Scheme, Proc. 2009 IEEE International Symposium on Circuits and Systems, Taipei,

- Taiwan, (May, 2009). DOI:10.1109/ISCAS.2009.5117927

- Masashi Imai, Kouei Takada, and Takashi Nanya: Fine-grain Leakage Power Reduction Method for m-out-of-n Encoded Circuits Using Multi-Threshold-Voltage Transistors, Proc. Async 2009, pp.209-216, Chapel Hill, NC, USA, (May, 2009). DOI:10.1109/ASYNC.2009.11

- 6. T. Yoneda, M Imai, H. Saito, A. Matsumoto: Achieving degradation tolerance in a hardware accelerator with parallel functional units, Proc. of Third Workshop on Dependable and Secure Nanocomputing (WDSN 2009), pp. 28-33, Lisbon, Portugal, (Jun., 2009). DOI:none

- Masashi Imai, Tomohiro Yoneda, Takashi Nanya: N-way Ring and Square Arbiters, Proc. of ICCD, pp.125-130, Lake Taohe, CA, USA, (Oct., 2009). DOI:10.1109/ICCD.2009.5413164

- 8. H. Zheng, H. Yao, T. Yoneda: Modular Model Checking of Large Asynchronous Designs with Efficient Abstraction Refinement, IEEE Transactions on Computers, Vol. 59, No. 4, pp. 561-573, (Apr., 2010). DOI: 10.1109/TC.2009.187

- 9. Naoya Onizawa, V. C. Gaudet and Takahiro Hanyu: Low-Energy Asynchronous Interleaver for Clockless Fully-Parallel LDPC Decoding, IEEE Trans. on Circuits and Syst. I Reg. Paper, IEEE Transactions on Computers, Vol. 59, No. 4, pp. 561-573, (Apr., 2010). DOI: 10.1109/TCSI.2011.2107271

- Hiroshi Saito, Naohiro Hamada, Tomohiro Yoneda, and Takashi Nanya: A Floorplan Method for Asynchronous Circuits with Bundled-data Implementation on FPGAs, Proc. of 2010 IEEE International Symposium on Circuits and Systems, pp925-928, (May, 2010). DOI: 10.1109/ISCAS.2010.5537402

- Naoya Onizawa and Takahiro Hanyu: A High-Throughput Protocol Converter Based on an Independent Encoding/Decoding Scheme for Asynchronous Network-on-Chip, Proc. 43rd International Symposium on Circuits and Systems, pp.157-160, (May, 2010). DOI: 10.1109/ISCAS.2010.5538027

- 12. Atsushi Matsumoto, Naoya Onizawa and Takahiro Hanyu: One-Color Two-Phase Asynchronous Communication Links Based on Multiple-Valued Simultaneous Control, Proc. 40th IEEE International Symposium on Multiple-Valued Logic, Vol.40, pp.211-216, (May, 2010). DOI: 10.1109/ISMVL.2010.47

- 13. Masashi Imai, Tomohide Nagai, Takashi Nanya: Pair and Swap: An approach to Graceful Degradation for Dependable Chip Multiprocessors, WDSN2010, Chicago (USA), (Jun., 2010). DOI:10.1109/DSNW.2010.5542608

- 14. Naoya Onizawa, Tomoyoshi Funazaki, Atsushi Matsumoto and Takahiro Hanyu: Accurate Asynchronous Network-on-Chip Simulation Based on a Delay-Aware Model, Proc. IEEE Computer Society Annual Symposium on VLSI 2010, pp.357-362, (Jul., 2010). DOI: 10.1109/ISVLSI.2010.45

- 15. Chammika Mannakkara , Tomohiro Yoneda : Asynchronous Pipeline Controller Based on Early Acknowledgement Protocol, IEICE Trans. Vol.E93-D,No.8, pp.2145-2161, (Aug., 2010). DOI: 10.1587/transinf.E93.D.2145

- 16. Naoya Onizawa, and Takahiro Hanyu: Highly Reliable Multiple-Valued One-Phase Signalling for an Asynchronous On-Chiip Communication Link, IEICE Trans. Inform., pp.2089-2099, (Aug., 2010). DOI: 10.1587/transinf.E93.D.2089

- 17. James Weston, Masashi Imai, Tomohide Nagai, Takashi Nanya: An Efficient Decision Unit for the Pair and Swap Methodology within Chip Multiprocessors, Proc. PRDC2010, pp.62-69, PRDC2010, National Institute of Informatics (Tokyo), (Dec., 2010). DOI: 10.1109/PRDC.2010.43

- 18. Naoya Onizawa, Atsushi Matsumoto, and Takahiro Hanyu: Interconnect-Fault-Resilient Delay-Insensitive Asynchronous Communication Link Based on Current-Flow Monitoring, Proc. Design Automation Test in Europe (DATE), pp.776-781, (Mar, 2011). DOI:none

- 19. Masashi Imai and Tomohiro Yoneda: Improving Dependability and Performance of Fully Asynchronous On-chip Networks, Proc. IEEE Int. Symp. Asynchronous Circuits and Systems 2011, pp.65-76, (Apr., 2011). DOI:10.1109/ASYNC.2011.15

- 20. Scott Little, David Walter, Chris Myers, Robert Thacker, Satish Batchu, Tomohiro Yoneda: Verification of Analog/Mixed-Signal Circuits Using Labeled Hybrid Petri Nets, IEEE Trans. on Computer-Aided Design of Integrated Circuits and Systems, Vol 30, No. 4, pp. 617-630, (Apr., 2011). DOI: 10.1109/TCAD.2010.2097450

- 21. Takao Kawano, Naoya Onizawa, Atsushi Matsumoto, and Takahiro Hanyu : Adjacent-State Monitoring Based Fine-Grained Power-Gating Scheme for a Low-Power Asynchronous Pipelined System, Proc. IEEE Int. Symp. Circuits and Systems 2011, (May, 2011). DOI:10.1109/ISCAS.2011.5938004

- 22. Atsushi Matsumoto, Naoya Onizawa and Takahiro Hanyu: Complementary Multiple-Valued Encoding Scheme for Interconnect-Fault-Resilient Bidirectional Asynchronous Links, Proc. 41th IEEE International Symposium on Multiple-Valued Logic, pp.236-241, (May, 2011). DOI:10.1109/ISMVL.2011.30

- 23. Naohiro Hamada and Hiroshi Saito: Integration of Behavioral Synthesis and Floorplanning for Asynchronous Circuits with Bundled-data Implementation, Proc. ACM Great Lakes Symposium on VLSI 2011, Campus Lausanne, Switzerland, (May, 2011). DOI:10.1145/1973009.1973042

- 24. Masashi Imai and Tomohiro Yoneda: Duplicated Execution Method for NoC-based Multiple Processer Systems with Restricted Private Memories, Proc. DFT2011, Vancouver, Canada, (Oct., 2011). DOI:10.1109/DFT.2011.38

- 25. Naohiro Hamada and Hiroshi Saito : Integration of Behavioral Synthesis and Floorplanning for Asynchronous Circuits with Bundled-Data Implementation", IEICE Transaction, Volume E95-C No.4, pp.506–515 (Apr., 2012). DOI:10.1587/transele.E95.C.506

- 26. Naoya Onizawa, Shoun Matsunaga, Vincent C. Gaudet, and Takahiro Hanyu: High-Throughput Low-Energy Content-Addressable Memory Based on Self-Timed Overlapped Search Mechanism, Proc. International Symposium on Asynchronous Circuits and Systems (ASYNC), pp.41-48 (May, 2012). DOI:10.1109/ASYNC.2012.25

- 27. Atsushi Matsumoto, Naoya Onizawa, and Takahiro Hanyu: Systematic Coding Schemes for Low-Power Multiple-Valued Current-Mode Asynchronous Communication Links, 42nd IEEE International Symposium on Multiple-Valued Logic, pp.13-18, (May, 2012). DOI:10.1109/ISMVL.2012.51

- 28. Naoya Onizawa, Atsushi Matsumoto, and Takahiro Hanyu: Long-Range Asynchronous On-Chip Link Based on Multiple-Valued Single-Track Signaling, IEICE Transactions on Fundamentals, E95-A(6), pp.1018-1029 (Jun., 2012). DOI:10.1587/transfun.E95.A.1018

- 29. Hiroshi Saito, Tomohiro Yoneda, Yuichi Nakamura : An ILP-based Multiple Task Allocation Method for Fault Tolerance Networks-on-Chip, Proc. of MCSoC2012, pp. 100-106 (Sep., 2012). DOI:10.1109/MCSoC.2012.23

- 30. Tomohiro Yoneda and Masashi Imai: Dependable Routing in Multi-Chip NoC Platforms for Automotive Applications, Proc. of DFT2012, pp. 217-224 (Oct., 2012). DOI:10.1109/DFT.2012.6378227

- 31. Tomohiro Yoneda, Masashi Imai, Naoya Onizawa, Atsushi Matsumoto, Takahiro Hanyu : Multi-Chip NoCs for Automotive Applications, Proc. of PRDC2012, pp. 105-110 (Nov., 2012). DOI:10.1109/PRDC.2012.20

- 32. Masashi Imai and Tomohiro Yoneda: Performance Modeling and Analysis of On-chip Networks for Real-time Applications, Proc. of PRDC2012, pp. 111-120 (Nov., 2012). DOI:10.1109/PRDC.2012.18

- 33. Ryohei Kobayashi, Shinya Takamaeda-Yamazaki, Kenji Kise: Towards a Low-Power Accelerator of Many FPGAs for Stencil Computations, Proc. of ICNC2012, pp.343-349 (Dec., 2012), DOI:10.1109/ICNC.2012.67

- 34. Naoya Onizawa, Shoun Matsunaga, Vincent C. Gaudet, Warren J. Gross, and Takahiro Hanyu: High-Throughput CAM Based on a Synchronous Overlapped Search Scheme, IEICE Electronics Express (ELEX), Vol.10, No.7, pp.20130148, (Apr., 2013). DOI:10.1587/elex.10.20130148

- 35. Naoya Onizawa, Atsushi Matsumoto, Tomoyoshi Funazaki, and Takahiro Hanyu:

- High-Throughput Compact Delay-Insensitive Asynchronous NoC Router, Computers, IEEE Trans. on, vol. PP, pp.1. (Apr. 2013). DOI:10.1109/TC.2013.81

- 36. Yuichiro Tanaka, Shimpei Sato, Kenji Kise: The Ultrasmall Soft Processor, International Symposium on Highly Efficient Accelerators and Reconfigurable Technologies (HEART2013), pp.63-68, (Jun., 2013).

- 37. Masashi Imai, Tomohiro Yoneda: Fault Diagnosis and Reconfiguration Method for Network-on-Chip Based Multiple Processor Systems with Restricted Private Memories, IEICE Trans on Inf.&Syst., Vol.E96-D, No.9, pp.1914-1925, (Sep., 2013).

- 38. Naoya Onizawa, Atsushi Matsumoto, and Takahiro Hanyu: Open-Fault Resilient Multiple-Valued Codes for Reliable Asynchronous Global Communication Links, IEICE Trans. on Information and Systems, Vol.E96-D, No.9, pp.1952-1961, (Sep., 2013).

- 39. Shimpei Sato, Kenji Kise: ArchHDL: A New Hardware Description Language for High-Speed Architectural Evaluation, Proc. of MCSoC2013, pp.107-112, (Sep., 2013)

- 40. Hideki Katabami, Hiroshi Saito, and Tomohiro Yoneda: Design of a GALS-NoC using Soft-cores on FPGAs, Proc. of MCSoC2013, pp.31—36, (Sep., 2013).

- 41. Naoya Onizawa, Shoun Matsunaga, Vincent C. Gaudet, Warren J. Gross, and Takahiro Hanyu, High-Throughput Low-Energy Self-Timed CAM Based on Reordered Overlapped Search Mechanism, Circuits and Systems I: Reg. Paper, IEEE Trans. on, vol. 61, pp.865-876. (Mar., 2014)

- 42. Takakazu Ikeda, Kenji Kise: Application Aware DRAM Bank Partitioning in CMP, Proc. of ICPADS, pp.349-365. (Dec., 2013)

- 43. N. Onizawa, A.Mochizuki, H. Shirahama, M. Imai, T. Yoneda, and T. Hanyu: High-Throughput Partially Parallel Inter-Chip Link Architecture for Asyncronous Multi-Chip NoCs, IEICE Trans. on Trans. on Information and Systems, (2014). (in press)

- 44. A. Mochizuki, H. Shirahama, and T. Hanyu: Design of a Quaternary Single-Ended Current-Mode Circuit for an Energy-Efficient Inter-Chip Asynchronous Communication Link, IEEE International Symposium on Multiple-Valued Logic, (May, 2014). (to appear)

- 45. H. Shirahama, A. Mochizuki, Y. Watanabe, and T. Hanyu: Energy-Aware Current-Mode Inter-Chip Link for a Dependable GALS NoC Platform, Proc. IEEE International Symposium on Circuits and Systems (ISCAS2014), (Jun., 2014). (to appear)

- 46. Masashi Imai, Tomohiro Yoneda: Multiple-Clock Multiple-Edge-Triggered Multiple-bit Flip-Flops for Two-Phase Handshaking Asynchronous Circuits, Proc. IEEE International Symposium on Circuits and Systems (ISCAS2014), (Jun., 2014). (to appear)

## (2)その他の著作物(総説、書籍など)

- Naoya Onizawa, Tomoyoshi Funazaki, Atsushi Matsumoto and Takahiro Hanyu: Accurate Asynchronous Network-on-Chip Simulation Based on a Delay-Aware Model, Chapter in Book: Designing Very Large Scale Integration Systems: Emerging Trends & Challenges, editors N. Voros, A. Mukherjee, N. Sklavos, K. Masselos, M. Huebner, Springer ISBN: 978-94-007-1487-8, 2011.

- 2. 米田友洋, 今井雅: 非同期式ネットワークオンチップ, 日本信頼性学会誌 特集「ディペンダブル VLSI システム」, Vol.35, No.8, pp.482, (Dec., 2013)

- 3. 吉瀬謙二: 高機能 NoC ルータアーキテクチャ, 日本信頼性学会誌 特集「ディペンダブル VLSI システム」, Vol.35, No.8, pp.483, (Dec., 2013)

- 4. 今井雅, 米田友洋: 多重化 CPUコアの故障検出と再構成手法, 日本信頼性学会誌 特集「ディペンダブル VLSI システム」、Vol.35、No.8、pp.514、(Dec., 2013)

# (3)国際学会発表及び主要な国内学会発表

① 招待講演 (国内会議 6件、国際会議 4件)

# 【国内】

1. 米田(NII): 最近の非同期式設計技術, 第 61 回 FTC 研究会, 奥伊勢フォレストピア(三重県松阪市), 2009.7.17.

- 2. 今井(東京大学): 非同期式設計技術の基礎, 第 61 回 FTC 研究会, 奥伊勢フォレストピア (三重県松阪市), 2009.7.17

- 3. T. Yoneda(NII): Recent Asynchronous Circuit Design Technologies, SOIM-GCOE09, 東北大学, 2009.10.28

- 4. 米田(NII): 非同期式計算に基づくディペンダビリティ向上へのアプローチ, CPSY/DC 研究会招待講演, 電子情報通信学会技術研究報告, CPSY/DC-2010, [1], pp 1-1, 東京工業大学(東京), 2010.4.13

- 5. 今井雅(東京大学):DSN2010報告, DC研究会招待講演,電子情報通信学会技術研究報告, DC2010-23, pp.31-34,機械振興会館(東京), 2010.10.14

- 6. 齋藤寛(会津大学):高信頼なネットワークオンチップ実現のための設計支援環境の 構築,組込み産業地域交流プラザ 2013 in 宮城,エルパーク仙台(仙台市), 2013.7.31

# 【国際】

- 1. T. Yoneda (NII): Asynchronous Network-on-Chip and its potential, ACSD invited talk, 2011.06.22, Newcastle UK

- 2. T. Yoneda (NII): Dependability Techniques for Networks on Chips, IFIP WG 10.4 invited talk, 2011.07.02, Taoyuan, Taiwan.

- 3. Kenji Kise (東工大), SmartCore System for Future Many-Module Era, The International Conference on Information and Communication Technology for Embedded Systems(IC-ICTES2013), Samutsongkhram, Thailand, 2013.1.24

- 4. Takahiro Hanyu: Challenge of MTJ-Based Nonvolatile Logic-in-Memory Architecture Towards Dar-Silicon Logic LSI, Workshop on Network on Chip between HKUST and CREST-DVLSI, Dec.9, 2013.

# ② 口頭発表 (国内会議 57件、国際会議 2件)

# 【国内】

- 1. 高田幸永,今井雅,中村宏,南谷崇(東京大学):マルチ閾値電圧トランジスタを用いた2線2相式非同期式回路のリーク電力削減手法,デザインガイア,電子情報通信学会技術研究報告 VLD-2008-90 ,pp.183-188,北九州学園研究都市,2008.11.19

- 2. 白濱弘勝, 永井 亮, 羽生貴弘 (東北大学): 高信頼電流モード多値集積回路技術とその応用, 電子情報通信学会「第 22 回多値論理とその応用研究会」, 群馬大学, 2009.1.10-11

- 3. 松本 敦, 羽生貴弘 (東北大学): 多値データ転送に基づく高性能 NoC の構成, 電子情報通信学会「第 22 回多値論理とその応用研究会」, 群馬大学, 2009.1.10-11

- 4. 米田友洋(NII),今井 雅(東京大学),齋藤 寛(会津大学),松本 敦(東北大学): ディペンダブル NOC への挑戦,「電子情報通信学会総合大会」,愛媛大学, 2009.3.18

- 5. 齋藤寛(会津大学),米田友洋(NII),南谷崇(東京大学):FPGA 実装を対象とした東データ方式による非同期式回路の遅延調整手法の評価,第22回軽井沢ワークショップ,pp.201-206,長野県軽井沢町,2009.4.21

- 6. 鬼沢 直哉, 松本 敦, 羽生 貴弘(東北大学), 米田友洋(NII): 高信頼オンチップ 非同期データ転送技術に関する一検討, 電子情報通信学会技術研究報告, vol. 109, no. 169, pp.1-6, SWoPP2009, フォレスト仙台(宮城県仙台市), 2009.8.5

- 7. 船崎智義,鬼沢直哉,松本敦,羽生貴弘(東北大学):非同期式ネットワークオンチップに基づくLSI設計環境の構築,平成21年度電気関係学会東北支部連合大会講演論文集,1D06,p.106,電気関係学会東北支部連合大会,東北文化学園

- 大学(宮城県仙台市), 2009.8.22

- 8. 松本 敦, 船崎 智義, 鬼沢 直哉, 羽生 貴弘(東北大学): 非同期式ネットワーク オンチップの回路レベル検証環境の構築, 第8回情報科学技術フォーラム講演論 文集第1分冊,519-520, FIT 2009,東北工業大学(宮城県仙台市), 2009.9.4

- 9. 松本 敦,鬼沢 直哉,羽生 貴弘(東北大学): 多値1色2線符号に基づく非同期 データ転送方式とその応用,多値論理研究ノート第32巻,1-1~1-5,北海道大学 (北海道札幌市),2009.9.9

- 10. 長井智英, 今井雅, 南谷崇(東京大学): プロセス二重化とプロセス対交換による チップマルチプロセッサの高信頼化手法, 電子情報通信学会技術研究報告, VLD2009-51, DC2009-38, pp.67-72, デザインガイア, (高知県高知市文化プラザ), 2009.12.3

- 11. 齋藤寛, 濱田尚宏(会津大学), 米田友洋(NII), 南谷崇(東京大学): FPGA 実装 を想定した東データ方式による非同期式回路のフロアプラン手法の検討, デザインガイア, (高知県高知市文化プラザ), 2009.12.4

- 12. 武安聡, 今井雅, 中村宏 (東京大学): パケット転送経路の偏りに着目した高性能 非同期式ネットワークオンチップの検討, 電子情報通信学会技術研究報告, VLD2010-66, pp.67-72, デザインガイア, 九州大学医学部(福岡), 2010.11.30

- 13. 濱田尚宏, 齋藤寛(会津大学): 東データ方式による非同期式回路を対象とした 動作合成とフロアプランの統合, 情報処理学会研究報告, vol.2010-SLDM-147 No.26, pp.137-142, デザインガイア, 九州大学医学部(福岡), 2010.12.1

- 14. 船崎智義,鬼沢直哉,松本敦,羽生貴弘(東北大学): リアクティブ遅延モデルに基づく高精度非同期ネットワークオンチップシミュレーション手法,電子情報通信学会技術研究報告,110-2,pp.9-14,東京工業大学(東京都目黒区),2010.4

- 15. 松本敦,鬼沢直哉,羽生貴弘(東北大学): リンク故障リカバリ機能を有する多値非同期転送方式,電子情報通信学会技術研究報告 110-8, pp. 284-289, 金沢市文化ホール(石川県金沢市), 2010.8

- 16. 河野宇朗,鬼沢直哉,松本敦,羽生貴弘(東北大学): 非同期細粒度パワーゲーティング手法,平成22年度電気関係学会東北支部連合大会講演論文集,110-2,pp.9-14,ニューウェルシティ宮崎(宮崎県宮崎市),2010.11

- 17. 松本敦,鬼沢直哉,羽生貴弘(東北大学): 多値1色符号に基づく非同期通信方式とそのネットワークオンチップへの応用,第9回情報科学技術フォーラム講演論文集,第1分冊,pp.385-386,九州大学(福岡県福岡市),2010.8

- 18. 鬼沢直哉,羽生貴弘(東北大学): 非同期式チップ間リンク速度の定量的評価手法,電子情報通信学会ソサイエティ大会, C-12-10, p. 71,大阪府立大学(大阪府堺市),2010.9

- 19. Chammika Mannakkara, Daihan WANG, Vijay HOLIMATH, Tomohiro YONEDA (NII), A Case Study on Dependable Network-on-Chip Platform for Automotive Applications, 電子情報通信学会技術研究報告, CPSY/DC-2011, [3], pp. 11-16, 2011.

- 20. Daihan Wang, Chammika Mannakkara, Vijay Holimath, Tomohiro Yoneda (NII), An Online Routing Mechanism with Higher Fault-Tolerance for Network-on-Chip, 電子情報通信学会技術研究報告, DC-2011, 2011

- 21. 渡邉友馬, 松本敦, 羽生貴弘(東北大学):遅延情報データベースに基づく高速・高精度非同期 NoC 設計・検証 CAD に関する一考察, 平成 24 年度電気関係学会東北支部連合大会講演論文集, 2H17, 会津大学(福島県会津若松市), 2012.8.

- 22. 今井雅(弘前大学), 米田友洋(NII):遅延制約を考慮した高性能非同期式回路配置 配線方式の検討,電気学会電子・情報・システム部門大会,弘前大学,2012.9.5

- 23. Masashi Imai(Hirosaki University), Tomohiro Yoneda(NII), "Floorplan Method for

- SDI-model-based Asynchronous Circuits to Achieve High Robustness against Delay Variations," IEEE/ACM Workshop on CAD for Multi-Synchronous and Asynchronous Circuits and Systems 2012, oral session, San Jose, 2012.11.08

- 24. Shinya Takamaeda, Naoki Fujieda, Kenji Kise(東工大): Network Performance of Multifunction On-chip Router Architectures, 電子情報通信学会研究報告 CPSY2012-52, 九州大学百年講堂, 2012.11.27

- 25. 笹河良介, 藤枝直輝, 高前田伸也, 吉瀬謙二(東工大): ネットワークオンチップに おける仮想チャネル利用法の再考, 電子情報通信学会研究報告 CPSY2012-51, 九州大学百年講堂, 2012.11.27

- 26. Ryohei Kobayashi, Shinya Takamaeda, Kenji Kise(東工大): Towards a Low-Power Accelerator of Many FPGAs for Stencil Computations, Third International Conference on Networking and Computing(ICNC2012), pp.343-349, Okinawa Gender Equality Center, 2012.12.7

- 27. 方波見英基, 齋藤寛(会津大学): Altera FPGA における GALS-NoC とその設計手法, 電子情報通信学会技術研究報告 RECONF, 慶應大学, 2013.1.16

- 28. 小林諒平, 高前田伸也, 吉瀬謙二(東工大):メッシュ接続 FPGA アレーを用いた 高性能ステンシル計算機の設計と実装, 電子情報通信学会研究報告 RECONF2013, pp. 159-164, 慶応義塾大学日吉キャンパス, 2013.1.17

- 29. 齋藤寛(会津大学),米田友洋(NII),中村祐一(NEC):高信頼なネットワークオンチップ実現のためのマルチタスクのスケジューリングとアロケーション,電子情報通信学会技術研究報告 VLD,沖縄青年会館,2013.3.5

- 30. 中井一貴, Chammika MANNAKKARA, Vijay HOLIMATH, 米田友洋(NII):ディペンダブルネットワークオンチッププラットフォームによる車載制御の実証に向けて, 電子情報通信学会技術研究報告 DC2012-103, 対馬市交流センター, 2013.3.14

- 31. 高前田伸也, 吉瀬謙二(東工大): FPGA ベースアクセラレータ向けメモリプリフェッチ機構の検討, 情報処理学会第 75 回全国大会, 東北大学 川内キャンパス, 2013.3.6

- 32. 浅野悠, 吉瀬謙二(東工大): メッシュ/トーラス接続型スーパーコンピュータ 向けタスク配置手法 MOPT の高速化, 情報処理学会第 75 回全国大会, 東北大 学 川内キャンパス, 2013.3.6

- 33. Ryohei Kobayashi, Shinya Takamaeda, Kenji Kise(東工大): Design of Synchronization Mechanism to Conquer the Clock Oscillator Variation for High Performance Stencil Computation Accelerator, 情報処理学会第75回全国大会,東北大学 川内キャンパス,2013.3.7

- 34. 笹河良介, 佐藤真平, 吉瀬謙二(東工大): NoC におけるロングエッジファースト(LEF)ルーティングの提案, 情報処理学会第75回全国大会, 東北大学 川内キャンパス, 2013.3.8

- 35. Takakazu Ikeda, Kenji Kise(東工大): A write request issue approach considering bank level request frequency with bank partitioning, 情報 処理学会第75回全国大会,東北大学 川内キャンパス, 2013.3.8

- 36. Shunya Igarashi, Ryosuke Sasakawa, Kenji Kise(東工大): On-Chip Router Architecture for Detecting Soft Errors, 情報処理学会第75回全国大会, 東北大学 川内キャンパス, 2013.3.8

- 37. 田中雄一郎, 笹河良介, 佐藤真平, 吉瀬謙二(東工大): 世界最小ソフトプロセッサの設計と応用, 情報処理学会研究報告 2013-EMB-28, No. 26, pp. 1-6, 対馬市交流センター, 2013. 3. 14

- 38. 吉瀬謙二(東工大): ウルトラスモールソフトプロセッサを用いたメニーコア プロセッサ, 情報処理学会研究報告 2013-ARC-204, NO. 3, pp. 1-3, 和歌山県 立情報交流センターBig・U, 2013. 3. 26

- 39. 高前田伸也, 吉瀬謙二(東工大): RTL 静的解析による FPGA アクセラレータ向 けアプリケーション特化メモリプリフェッチャー, 情報処理学会研究報告 2013-ARC-204, No. 1, pp. 1-5, 和歌山県立情報交流センターBig, 2013. 3. 26

- 40. 佐藤真平, 吉瀬謙二(東工大): C++をベースとする新しいハードウェア記述の検討, 情報処理学会研究報告 2013-ARC-205, No.7, pp.1-7, 那覇市 IT 創造館. 2013.4.26

- 41. 浅野悠, 吉瀬謙二(東工大):10000 タスクに対応するタスク配置手法 SFMOPT の提案と評価, 先進的計算基盤システムシンポジウム SACSIS2013 論文集, pp.38-46, 仙台国際センター, 2013.5.22

- 42. 笹河良介, 藤枝直輝, 高前田伸也, 吉瀬謙二(東工大): ネットワークオンチップに おける仮想チャネル利用法の再考と評価, 先進的計算基盤システムシンポジウム SACSIS2013 論文集, pp.170-178, 仙台国際センター, 2013.5.24

- 43. 小林諒平, 高前田伸也, 吉瀬謙二(東工大): 多数の小容量 FPGA を用いたスケーラブルなステンシル計算機の開発, 先進的計算基盤システムシンポジウム SACSIS2013 論文集, pp.179-187, 仙台国際センター, 2013.5.24

- 44. 田中雄一郎, 笹河良介, 吉瀬謙二(東工大): 世界最小ソフトプロセッサの設計と実装, 先進的計算基盤システムシンポジウム SACSIS2013 論文集, pp.188-196, 仙台国際センター, 2013.5.24

- 45. 笹河良介, 吉瀬謙二(東工大): NoC のためのロングエッジファーストルーティング の提案と評価, 情報処理学会研究報告 2013-ARC-206, No.13, pp.1-8, 北九州国際会議場, 2013.7.31

- 46. 金子達哉, 佐藤真平, 吉瀬謙二(東工大): ArchHDL で記述したハードウェアの論理シミュレーションの高速化, 情報処理学会研究報告 2013-ARC-206, No.25, pp.1-8, 北九州国際会議場, 2013.8.1

- 47. 佐藤謙介, 今井雅(弘前大学): 多ビット記憶素子を用いた高性能非同期式回路設計方式, 電気学会 電子・情報・システム部門大会, pp.864-869, 北見工業大学, 2013.09.05

- 48. 今井雅(弘前大学), 米田友洋(NII):マルチクロック・デュアルエッジトリガフリップフロップを用いたヘテロタイミング回路設計, 電気学会 電子・情報・システム部門大会, pp.870-875, 北見工業大学, 2013.09.05

- 49. 高前田伸也, 吉瀬謙二(東工大): FPGA プロトタイピング向けメモリ管理フレームワークの開発, 電子情報通信学会研究報告 RECONF2013-35, pp.1-6, 北陸先端科学技術大学院大学, 2013.9.19

- 50. 羽生貴弘, 白濱弘勝, 渡邉友馬, 望月明(東北大学): 非同期 NoC プラットフォーム 向け高効率電流モードチップ間データ転送回路の構成, 多値論理研究ノート第 36 巻, 姫路市市民会館(兵庫県姫路市), 2013.9.

- 51. 笹河良介, 佐藤真平, 吉瀬謙二(東工大): 高信頼メニーコアシステム Smart Core における TMR 実行の提案と評価, 電子情報通信学会研究報告 CPSY2013, 幕張メッセ 国際会議場、2013、10.3

- 52. 佐藤真平, 吉瀬謙二(東工大): ハードウェアモデリング言語 ArchHDL から Verilog HDL へのトランスレータの設計, 電子情報通信学会研究報告 CPSY2013, 幕張メッセ 国際会議場, 2013.10.3

- 53. 今井雅(弘前大学),米田友洋(NII):2 相ハンドシェイクプロトコル非同期式回路向けマルチクロック・マルチエッジトリガ・フリップフロップの提案,電子情報通信学会技術研究報告 VLD,弘前大学,2013.10.07

- 54. 宮囿悟, 斎藤寛(会津大学): シングルコア向けのコードを NoC に実装するため のコード分割ツールの検討, 情報処理学会研究報告, 2013-SLDM-163, no. 21, pp. 1-6, 鹿児島県文化センター (鹿児島市), 2013. 11. 28

- 55. 佐藤真平, 吉瀬謙二(東工大): ArchHDL によるハードウェア記述の実践, 情報処

- 理学会研究報告 2014-ARC-208, No.21, pp.1-8, 東工大大岡山キャンパス, 2014 1.24

- 56. 中井一貴, 小泉夢月, 米田友洋(NII): 車載制御用ディペンダブル NoC プラットフォームの評価キット構築,電子情報通信学会技術研究報告 DC2013-92, pp.133-138, ICT 文化ホール(沖縄県石垣市), 2014.03.15

- 57. 寺山恭平, 今井雅(弘前大学): MOUSETRAP パイプライン回路のスキャンテスト, 電子情報通信学会 2014 年総合大会,新潟大学, 2014.03.21

# 【国際】

- 1. Yuma Watanabe, Hirokatsu Shirahama, Akira Mochizuki and Takahiro Hanyu: Design of an Energy-Efficient Inter-Chip Data Transmission Circuit for an Asynchronous NoC Platform, 2013 International Workshop on Emerging ICT, Oct. 2013.

- 2. A. Mochizuki, H. Shirahama, and T. Hanyu: Energy-Aware Current-Mode Inter-Chip Link for an Asynchronous NoC Platform, Workshop on Network on Chip between HKUST and CREST-DVLSI, Dec.9, 2013.

# ③ ポスター発表 (国内会議 2件、国際会議 7件)

# 【国内】

- 1. 長井智英, 今井雅, 南谷崇(東京大学):プロセス二重化とプロセス対交換によるチップマルチプロセッサの高信頼化手法, デザインガイア, (高知県高知市文化プラザ), 2009.12.3

- 2. 武安聡, 今井雅, 中村宏 (東京大学): パケット転送経路の偏りに着目した高性能 非同期式ネットワークオンチップの検討, デザインガイア, 九州大学医学部(福岡), 2010.11.30

# 【国際】

- 1. Masashi Imai, Tomohiro Yoneda: Evaluation of Delay Variations and Soft-Error Hardness in Asynchronous Pipeline Circuits, IEEE/ACM Workshop on Variability Modeling and Characterization, San Jose, CA (USA), 2010.11.11

- 2. Shi Yuan, Atsushi Matsumoto, Naoya Onizawa, and Takahiro Hanyu: Low-Energy Asynchronous Single-Track Data Transmission and Its Application, Japan-China-Korea Conference on Electronics & Communications 2010

- 3. Atsushi Araki, Tomoyoshi Funazaki, Atsushi Matsumoto, and Takahiro Hanyu: Accurate Simulation Environment for Asynchronous Network-on-Chip Design, Japan-China-Korea Conference on Electronics & Communications 2010

- 4. Daihan Wang, Michihiro Koibuchi, Tomohiro Yoneda, Hiroki Matsutani, Hideharu Amano: Dynamic Link-Width Optimization for Network-on-Chip, CPSNA'11, 2011

- 5. Masashi Imai, Tomohiro Yoneda, "Floorplan Method for SDI-model-based Asynchronous Circuits to Achieve High Robustness against Delay Variations," IEEE/ACM Workshop on CAD for Multi-Synchronous and Asynchronous Circuits and Systems 2012, poster session, San Jose, 2012.11.08

- 6. Hiroshi Saito, Tomohiro Yoneda, Yuichi Nakamura, "A Multi-Task Scheduling and Allocation Method for Reliable Network-on-Chip", Work-in-progress session, DAC13, 2013.

- 7. Masashi Imai, Tomohiro Yoneda, "Variability Evaluation and Characterization of Multi-clock Dual-Edge-Triggered FlipFlops," IEEE/ACM Workshop on Variability Modeling and Characterization (VMC2013), poster session, San Jose, 2013.11.21

# (4)知財出願

① 国内出願(7件)

- 出願番号:特願 2009-085925, 発明者:米田友洋 発明の名称「自律式並列演算回路」

出願人:情報・システム研究機構, 出願日:2009 年 3 月 31 日

- 出願番号:特願 2010-190330, 発明者:米田友洋 発明の名称「LSI 演算装置及びその故障検出方法」 出願人:情報・システム研究機構, 出願日:2010 年8月27日

- 3. 出願番号:特願 2010-123609, 発明者:羽生貴弘,鬼沢直哉 発明の名称「非同期プロトコル変換装置」 出願人:国立大学法人東北大学,出願日:2010 年 5 月 28 日

- 4. 出願番号: 特願 2011-548651, 発明者: 羽生貴弘, 鬼沢直哉, 松本敦 発明の名称「遅延・配線故障耐性を有する非同期データ転送装置」 出願人: 国立大学法人東北大学, 出願日: 2011 年 3 月 12 日

- 5. 出願番号:特願 2012-105558, 発明者:羽生貴弘, 他3名 発明の名称「半導体記憶装置及びその駆動方法」 出願人:国立大学法人東北大学、出願日:2012 年5月6日

- 6. 出願番号: 特願 2013-60616, 発明者: 米田友洋 発明の名称「半導体チップ、半導体チップ接続システム」 出願人: 情報・システム研究機構, 出願日: 2013 年 3 月 22 日

- 7. 出願番号:特願 2013-134719, 発明者:米田友洋, 今井雅 発明の名称「フリップフロップ回路」 出願人:情報・システム研究機構, 出願日:2013 年 6 月 27 日

# ② 海外出願 (1件)

1. 出願番号:PCT/JP2013/62791, 発明者:羽生貴弘, 他3名 発明の名称「半導体記憶装置」 出願人:国立大学法人東北大学, 出願日:2013年5月3日

# (5)受賞・報道等

# ① 受賞

- 1. Naoya Onizawa, Tomoyoshi Funazaki, Atsushi Matsumoto, Takahiro Hanyu: IEEE Computer Society Annual Symposium on VLSI Best Paper Award, 2010

- 2. 松本 敦: FIT2009 ヤングリサーチャー賞, 第9回情報科学技術フォーラム, 2010

- 3. 笹河良介:情報処理学会第75回全国大会 学生奨励賞「NoC におけるロングエッジファースト(LEF)ルーティングの提案」,2013.3

- 4. 浅野悠: 先進的計算基盤システムシンポジウム SACSIS2013 優秀若手研究賞 「10000 タスクに対応するタスク配置手法 SFMOPT の提案と評価」, 2013.5

- 5. 佐藤真平: 計算機アーキテクチャ研究会若手奨励賞「ArchHDL によるハードウェア 記述の実践」, 2014. 3.

# §6 最後に

本チームは、高ディペンダブル・高性能・高アダプタブルなプラットフォームを開発し、車載アプリケーションにより実証を行うことを目標とし、モノ作りに軸足を置いて、ハードウェアと開発支援ツール、および、実証用の高度な車載アプリケーションを開発してきた。それらを、簡易プラントモデルまで組み込んだ状態で開発キットという形にまとめ上げることができたということで、ほぼ目標を達成できたと考えている。カーメーカからの助言を早い段階から得ていたため、出口戦略的にも良い方向に進めたと考えている。期間内に具体的な実用化の目処を立てることはできなかったが、そのた

めの話し合いは進んでおり、もう少し時間をかけて、詰めていきたいと考えている. 要素技術である 非同期式回路技術の応用に関する発展テーマも始まりかけており、この方向でも企業との共同研 究へと発展させていきたい.

プロジェクト運営については、当初からの4グループは、それぞれの要素技術を開発するとともに、数多くの打合せを通して車載制御実証システムを構築するという一つの方向に集中することができ、非常にまとまりのよりチームであったと考える。東工大グループは途中から加わった形であるが、打合せを通して早い段階から相乗効果が現れ、既存グループもいくつかの新しい考え方を得られたことはチーム全体にとって大きなメリットであった。

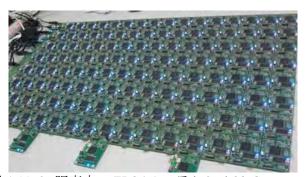

実験設備の一部(NIIグループ)

研究室メンバ(NII グループ)