「素材・デバイス・システム融合による革新的ナノエレクトロニクスの創成」 平成26年度採択研究代表者 H27 年度 実績報告書

## 橋本 昌官

## 大阪大学 大学院情報科学研究科 准教授

# ビアスイッチの実現によるアルゴリズム・処理機構融合型 コンピューティングの創出

## § 1. 研究実施体制

- (1)「テスト」グループ

- ① 研究代表者:橋本 昌宜(大阪大学大学院情報科学研究科、准教授)

- ② 研究項目

- ・クロスバーの性能評価

- (2)「ビアスイッチ・動作合成」グループ

- ① 主たる共同研究者:杉林 直彦 (日本電気株式会社 グリーンプラットフォーム研究所、シニアマネージャー)

- ② 研究項目

- ・ビアスイッチの研究開発

- ・簡単なベンチマークアプリケーションの準備と動作合成に求められる機能の予備調査

- (3)「アーキテクチャ」グループ

- ① 主たる共同研究者:密山 幸男 (高知工科大学システム工学群、准教授)

- ② 研究項目

- ・配線構造検討のための評価環境の構築

- ・機械学習向けアクセラレータのアーキテクチャ検討

- (4) 「回路」グループ

- ① 主たる共同研究者:小野寺 秀俊 (京都大学大学院情報学研究科、教授)

- ② 研究項目

・目標エネルギー効率実現性評価

## (5)「マッピング」グループ

- ① 主たる共同研究者:越智 裕之 (立命館大学情報理工学部、教授)

- ② 研究項目

- ・ツール開発に必要な課題の抽出、特にビアスイッチが敷き詰められる BEOL 層とトランジスタが敷き詰められる FEOL 層の面積が共に最大限有効活用されるための条件の予備検討

- ・混合粒度再構成可能アーキテクチャのための初期配置アルゴリズムの改良

- ・ビアスイッチを用いた細粒度プログラマブルロジックに特化したテクノロジマッピングアルゴリズムの開発

## § 2. 研究実施の概要

本研究では、IoT(Internet of Things)に代表される組み込み用途において、専用ハードウェア化による高いエネルギー効率、ソフトウェア実装と同等の設計生産性、低い NRE (Non-recurring Expense)コストのすべてを実現する新たなアルゴリズム・処理機構融合型コンピューティングを創出し、その実現に不可欠な新ナノデバイスとしてビアスイッチを開発する。

上記の目的の実現に向け、平成27年度はビアスイッチの実現可能性の実証とアーキテクチャの基本設計に注力し、以下の研究項目を実施した。

## ビアスイッチデバイスの開発

- Sneak Path 問題の検証 (ビアスイッチ、テスト Gr)

- Si/SiN/a-Si バリスタと 2V1CAS ビアスイッチの試作(ビアスイッチ Gr)

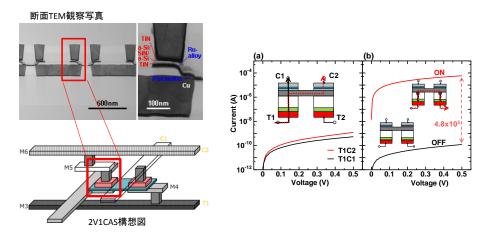

ビアスイッチの実現可能性を実証した[1]。試作デバイスの断面図と特性を図 1 に示す。

図 1

- ビアスイッチを活用した高密度再構成可能アーキテクチャの基本設計

- クロスバー構造の提案(全 Gr)

- o 性能評価 (テスト、ビアスイッチ Gr)

- o ロジックアーキテクチャ(マッピング、高位合成 Gr) ビアスイッチの特徴を活かし面積効率を高めた LUT を提案すると共に、そのため のマッピングアルゴリズムを開発し、これらの有用性を示した[2]。

- o 回路アーキテクチャ(回路 Gr) 基板バイアス制御ならびに低電圧ラッチ回路の動作安定性について検討し、低電圧動作によるエネルギー効率の改善効果を示した[3,4]。

- 目標エネルギー効率実現性評価(回路、高位合成 Gr)

- 研究進捗図(回路、高位合成 Gr)

- 機械学習向けアクセラレータの基本設計(アーキテクチャ Gr)

#### ○代表的な論文

- [1] N. Banno, M.Tada, K. Okamoto, N. Iguchi, T. Sakamoto, M. Miyamura, Y. Tsuji, H. Hada, H. Ochi, H. Onodera, M. Hashimoto, and T. Sugibayashi, ``A Novel Two-Varistors (a-Si/SiN/a-Si) Selected Complementary Atom Switch (2V-1CAS) for Nonvolatile Crossbar Switch with Multiple Fan-Outs," Dig. of IEDM, pp. 32-35, 2015.

- [2] T. Higashi, H. Ochi, "Area-efficient LUT-like Programmable Logic Using Atom Switch and Its Mapping Algorithm," Proc. of ISCIT, pp.201-204, 2015.

- [3] A.K.M. M. Islam and H. Onodera, "On-chip Monitoring and Compensation Scheme with Fine-grain Body Biasing for Robust and Energy-Efficient Operations", Proc. of ASP-DAC, pp. 403 409, 2016.

- [4] T. Kamakari, J. Shiomi, T. Ishihara, H. Onodera, "A Closed-Form Stability Model for Cross-Coupled Inverters Operating in Sub-Threshold Voltage Region", Proc. of ASP-DAC, pp. 691 696, 2016.