「次世代エレクトロニクスデバイスの創出に資する革新材料・プロセス研究」 平成20年度採択研究代表者

H22 年度 実績報告

# 鳥海 明

# 東京大学大学院工学系研究科・教授

Ge High-k CMOS に向けた固相界面の理解と制御技術の開発

# §1. 研究実施の概要

高性能 Ge CMOS の開発を目指して、ゲートスタック界面、ソース/ドレイン接合界面の理解および制御の手法の研究をすすめている。特に今年度は、 $Ge/GeO_2$ ゲートスタックからの GeO の脱離に関して、その起源、影響に関して実験的に詳細に調べ、脱離のモデル化を進めた。その結果、 $GeO_2$  中の酸素空孔拡散の重要性が示された。また、GeMOSFET のモビリティに関しては、電子および正孔の両方に対して現在報告されている中では最も高いピーク移動度が実験的に示された。これは SiMOSFET の結果を大きく超えるものであり、GeCMOS の可能性が実証的に示されたと言える。Ge/Metal 界面の Fermi-level Pinning に関しては、絶縁膜挿入による pinning への効果に関して絶縁膜種類の影響、膜厚の関係について研究を進め、数ナノメートルの長距離にわたって Schottky Barrier Height が変化することが示された。

## § 2. 研究実施体制

- (1)「鳥海」グループ(研究機関別)

- ①研究分担グループ長:鳥海 明 (東京大学大学院工学系研究科、教授)(研究代表者)

## ②研究項目

- 1. Ge/GeO<sub>2</sub>界面の研究

- 2. Ge/High-k 界面の研究

- 3. Ge/Metal 界面の研究

- 4. Ge MISFET のモビリティの研究

# §3. 研究実施内容

ゲートスタック界面、ソース/ドレイン接合界面の理解および制御の手法の研究開発をすすめ、その理解に基づいて高性能 Ge CMOS の実証を目指している。特に今年度は、 $Ge/GeO_2$ からの GeO の脱離の詳細研究、その理解に基づく FET 作製および高モビリティの実現に関して大きな 進捗が示すことができた。さらに新しい Ge MOSFET の可能性として、高濃度 Ge 薄膜を用いた Depletion 型の MOSFET (junctionless FET)の基礎特性、その可能性について評価解析を進めた。

### 1. Ge/GeO2 界面の研究

$Ge/GeO_2$ スタックからの GeO の脱離に関して、本年もさらに注力し新たな実験結果を含めて脱離のモデル化、その  $GeO_2$  に及ぼす効果などに関して明らかにすることができた。昨年度の酸素同位体を用いた拡散機構の研究に加えて、Ge 同位体を使うことで GeO の脱離の Kinetics がより明瞭になった。その結果に従うと、GeO 脱離の開始は  $Ge/GeO_2$  界面における反応であるが、GeO の脱離に関しては、界面から GeO が拡散して脱離するのではなく、初期的には  $GeO_2$  表面から GeO が GeO として脱離すると結論された Fo このことは界面から表面に向かって拡散するのは酸素空孔であり、それが表面からの Fo の脱離に導くとモデル化される。このような機構が脱離を促進しているとすると、Fo の 中に欠陥を誘起することは容易に想像される。これは酸化あるい

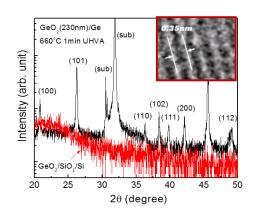

は酸素アニール条件を変えることで作製された  $GeO_2$  膜に関する ESR の結果(K. Kita et al., IEDM(2009))とも一致する。ただし、酸素空孔の拡散は赤外吸収にあまり影響を与えていないことも示され、全体のネットワーク構造にはあまり影響していない。以上の結果は、我々が行ってきた高圧酸化という手法の熱力学的有用性を裏付けるものである。さらに脱離が促進されると、図1に示すように  $GeO_2$  が結晶化するという新たな結果が実験的に観測された。この事実も酸素空孔に起因したものとして説明できる。

図1 Ge 上の GeO<sub>2</sub>を真空アニールした 場合の GeO<sub>2</sub> の結晶化。SiO2 上の場 合にはアモルファスのままである。

#### 2. Ge/High-k 界面の研究

本年も High-k 材料としては LaLuO $_3$ (LLO) および Y $_2$ O $_3$ を取り上げた。 Y $_2$ O $_3$ に高圧酸素アニールを施すことによって、 $GeO_2$ の時よりもさらに良好な CV 特性を得ることができた。 LLO に関してはすでに既報 (T. Tabata *et al.*, *ECS Trans.* 16 (2008))であるが、これらは  $GeO_2$  中の僅かな希土類酸化物は  $GeO_2$  をより安定化させていることを意味している。 我々はこれを Valency Passivation と名付けた  $^2$ 0。 Valency が本質かどうかに関しては、さらに微視的に調べる必要があ

るが、 $GeO_2$  が本来的にもつ不安定性を  $Y_2O_3$  の導入が解消していることは間違いない。これらの理解に基づいて高圧酸素アニールを使わずともかなりよい CV 特性が実現されている。一方、希土類酸化物中に僅かな  $GeO_2$  を導入すると欠陥が形成されているように見える  $^3$ 。今後、High-k/Ge 界面を制御していく上で、High-k 膜中への Ge の up-diffusion をどのように抑制していくかが重要と考えられる。

#### 3. Ge/Metal 界面の研究

GeとMetal のコンタクト特性は Ge MOSFET 技術の懸念事項の一つである。GeとMetal の間に絶縁膜を挿入すると Schottky Barrier Height (SBH)が変化することは既報 (T. Nishimura et al., APEX(2008))。これは Ge の Fermi-level Pinning (FLP)を調べる上できわめて重要な事実である。今年度はコンタクト特性を向上するために、バンド不連続量が小さい材料でかつ SBH が変調される材料を選択することが重要になると考え、伝導帯端にほとんど障壁を持たない絶縁膜として  $TiO_2$ を選び SBH 特性を調べたところ、 $TiO_2$ を挿入しても完全に FLP は解けない。また絶縁膜の挿入効果は 2nm 以上まで効いており長距離にわたる緩和過程が関わっていることがわかった。

### 4. Ge MISFET モビリティの研究

FET として、今年度から多数キャリア FET の検討も始めた。これはいわゆる薄膜 SOI 上の Junctionless FET として Tyndall のグループから H21 年度末に報告されたものである(J. P. Colinge et al., Nature Nanotech. 5 (2010) 225)。我々はこの動作機構・制御機構を考えたとき に高ドープしたバルク半導体においてもキャリアモビリティは Ge の方が Si 比べて圧倒的に高い点 に着目し、Si よりも Ge がより適していると考え GeOI 基板上において検討を始めた。今年度は、上記のことを長チャネル p-MOSFET において実証できた  $^{7}$ 。

通常の MOSFET に関して、界面特性の改善にしたがってそのモビリティは急激に向上すること

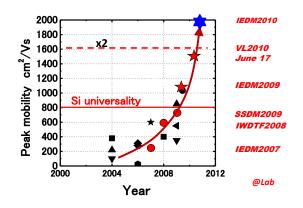

を示すことができた。特に面方位に注目し、1 で述べた界面からの GeO の脱離の面方位依存性を調べた結果、(111)面の熱的安定性が実験的に示されが、結果として FET のモビリティも(111)面の良好性が電子に対して示された。ピークモビリティは 1,500cm²/Vsec という値を 6 月に開催された VLSI シンポジウムで発表 2)、12 月には IEDM においてほぼ 2,000cm²/Vsec という値を報告することができた(図 2)%。この値は Ge のバルクモビリティのほぼ 50%に対応し、Si のバルクモビリティとユニバーサルモビリティとの関係と同様のレ

図 2 Ge NMOSFET における電子のピークモビリティの年次推移(赤、青シンボル)。黒シンボルは他機関からの文献値。

ベルに達したと言える。一方、正孔モビリティに関しては Si を超える値が従来から報告されていた ため昨年度は試みなかったが、本年度は電子と同様の手法によって作製、評価した。その結果、正孔においても従来報告されているどの値よりも高い値を実証できた(~720cm²/Vsec)6。モビリティが向上された結果、その温度依存性はようやく通常の半導体の振る舞い(温度低下とともにモビリティが上昇)を示すようになり、ようやく散乱機構の解析に踏み込める。またサブスレッショールドファクタも室温で 80mV/dec を実証し6、Ge MOSFET の潜在的可能性を実証したと言える。

# §4. 成果発表等

## (4-1) 原著論文発表

#### ●論文詳細情報

- A. Toriumi, S.K. Wang, C.H. Lee, M. Yoshida, K. Kita, T. Nishimura and K. Nagashio, "Oxidation, Diffusion and Desorption in Ge/GeO<sub>2</sub> System, " ECS Trans., 28 (2), pp.171-180 (2010). (DOI: 10.1149/1.3372573)

- T. Nishimura, C.H. Lee, S.K. Wang, T. Tabata, K. Kita, K. Nagashio, and A. Toriumi, "Electron Mobility in High-k Ge MISFETs Goes up to Higher," 2010 Symposium on VLSI Technology, Digest of Technical papers,p.209, (Jun. 17, 2010, Honolulu). (DOI: 10.1109/VLSIT.2010.5556230)

- 3. T. Tabata, C. H. Lee, K. Kita, and A. Toriumi, "Direct LaLuO<sub>3</sub>/Ge Gate Stack Formation by Interface Scavenging and Subsequent Low Temperature O<sub>2</sub> Annealing," ECS Trans. **33**(3) 375-382(2010). (DOI: 10.1149/1.3481626)

- 4. A. Toriumi, C. H. Lee, T. Nishimura, K. Kita, S. K. Wang, M. Yoshida, and K. Nagashio, "Feasibility of Ge CMOS for Beyond Si-CMOS, ECS Trans. **33** (6) 33-46 (2010). (DOI: 10.1149/1.3487532)

- S. K. Wang, K. Kita, C.H. Lee, T. Tabata, T. Nishimura, K. Nagashio and A. Toriumi, "Desorption kinetics of GeO from GeO<sub>2</sub>/Ge structure," Journal of Applied Physics, 108, 054104 (2010). (DOI: 10.1063/1.3475990)

- C.H. Lee, T. Nishimura, T. Tabata, S.K. Wang, K. Nagashio, K. Kita and A. Toriumi, "Ge MOSFETs Performance: Impact of Ge Interface Passivation",

2010IEEE International Electron Device Meeting (IEDM2010), pp.416-419 (Dec. 7, 2010, San Francisco). (DOI: 10.1109/IEDM.2010.5703384)

- DD. Zhao, T. Nishimura, C. H Lee, K. Nagashio, K. Kita, and A. Toriumi, "Junctionless Ge p-Channel Metal—Oxide—Semiconductor Field-Effect Transistors Fabricated on Ultrathin Ge-on-Insulator Substrate," Applied Physics Express 4 (2011) 031302. (DOI: 10.1143/APEX.4.031302)