「次世代エレクトロニクスデバイスの創出に資する革新材料・プロセス研究」 平成20年度採択研究代表者

H22 年度 実績報告

# 遠藤 哲郎

国立大学法人東北大学 学際科学国際高等研究センター・教授

縦型ボディーチャネル MOSFET とその集積プロセスの開発

# §1. 研究実施の概要

本研究は、次世代エレクトロニクスデバイスの創出に資する革新材料・プロセス技術・デバイス技術の開拓のために、デバイスのボディー領域全体を電流駆動領域とする新概念の縦型構造トランジスタのデバイス技術に加えて、その回路設計・材料・プロセス技術までを一貫して開発するものである。これにより、平面型 MOSFET と比較して、駆動電流特性、リーク電流特性、集積密度を大幅に向上させた半導体 LSI の新しいユニバーサル技術プラットフォームを提供する。

平成 22 年度は、縦型ボディーチャネル MOSFET による基本集積回路及び集積化プロセス技 術の開発を推進した。具体的には、第1の研究項目(デバイス技術)として、試作した縦型ボディー チャネル MOSFET のデバイス特性を取得し、その評価結果を踏まえて、当該デバイスのチャネル 不純物分布に対する設計技術の高精度化を行ない、その知見を DRAM セルへの展開を図り、縦 型 MOSFET からなる  $4F^2$  セルを実現できる 1Tr-DRAM セルを提案し、その優位性を示した。さら に、10nm 以降の世代における縦型ボディーチャネル MOSFET の設計指針を探索するために、 チャネルピラー中の電荷の伝導領域に対する、チャネル不純物分布の関係を解明した。 第2の研 究項目(回路技術・設計技術)として、昨年度に構築した縦型ボディーチャネル MOSFET による 集積回路の高効率な回路ネットワークの合成とレイアウトパターンの生成技術を実際の小規模集 積回路のレイアウトパターンに適用し、平面型 MOSFET ベースのパターンレイアウトを、縦型ボデ ィーチャネル MOSFET ベースのパターンレイアウトに自動変換できるレベルまでの高度化に成功 した。さらに、縦型 MOSFET 固有の特徴を生かしてリード動作に対する SNM と書き込み動作に 対する SNM の両方に優れる新しい SRAM セルを開発した。さらに、縦型ボディーチャネル MOSFET の高い駆動能力と基板バイアス効果フリーの特徴を生かした縦型ボディーチャネル MOSFET による高性能昇圧回路を開発した。第 3 の研究項目(材料・プロセス技術)として、 3Xnm 世代のシリコン 3 次元加工技術、並びに、様々な面方位を有する微細シリコンピラー側面の 均一な酸化技術の開発をさらに推し進めると共に、米国 Albany に拠点を置くTEL テクノロジーセ ンターアメリカでの新しい試作環境を構築した。そして、この新しい試作環境を活用し、High-k ゲ ート絶縁膜/金属ゲート電極膜を適用した縦型 MOSFET 向けの材料・プロセス開発を行い、縦型 MOSキャパシタを試作するレベルまで到達した。

なお、平成 23 年 3 月 11 日に発生した東日本大震災により、本研究の拠点となっている東北大学は大きく被災した。しかし、幸いにして人的被害はなく、その後の参加メンバーの献身的な努力と皆様からの温かいサポートにより、復興への歩みを着実に進めてきている。引き続き、皆の英知、新しく平成 23 年度から新規に参加するメンバーの力と皆様からのサポートを結集して、現在予想されている 2~4 カ月程度の遅れを圧縮していく所存である。そして、平成 23 年度は、縦型ボディーチャネル MOSFET のデバイス技術、回路技術、設計技術、材料プロセス技術の研究を推進すると共に、これまでの研究成果を統合化することで、縦型ボディーチャネル MOSFET に基づく回路構成技術とその設計技術の実用化に向けた問題点を抽出し、この結果を受けて、縦型ボディーチャネル MOSFET に基づく集積回路の研究に着手する。

# § 2. 研究実施体制

- (1)「東北大学 遠藤」グループ

- ①研究分担グループ長:遠藤 哲郎 (東北大学 学際科学国際高等研究センター、教授)

- ②研究項目

- ・ 縦型ボディーチャネル MOSFET のデバイス技術の構築

- ・ 縦型ボディーチャネル MOSFET に基づく回路技術と設計技術の構築

- ・ 縦型ボディーチャネル MOSFET による CMOS 集積回路の集積プロセス技術の構築

- (2)「東北大学 小池」グループ

- ①研究分担グループ長:小池 淳一 (東北大学 大学院工学研究科、教授)

- ②研究項目

- ・ 縦型ボディーチャネル MOSFET のメタル拡散層形成技術の開発

- (3)「東京エレクトロン株式会社 塚本」グループ

- ①研究分担グループ長:塚本雄二(東京エレクトロン株式会社 開発企画室、室長)

- ②研究項目

- ・ 縦型ボディーチャネル MOSFET による CMOS 集積回路の材料・プロセス技術の構築

#### § 3. 研究実施内容

(文中に番号がある場合は(4-1)に対応する)

本研究は、次世代エレクトロニクスデバイスの創出に資する革新材料・プロセス技術・デバイス技術の開拓のために、デバイスのボディー領域全体を電流駆動領域とする新概念の縦型構造トランジスタのデバイス技術に加えて、その回路設計・材料・プロセス技術までを一貫して開発し、それにより半導体 LSI における新しいユニバーサル技術プラットフォームの実現に挑むものであり、以下の3つの主要課題から構成される。

- ① 縦型ボディーチャネル MOSFET のデバイス技術の構築

- ② 縦型ボディーチャネルデバイスに基づく回路技術とその設計技術の構築

- ③ 縦型ボディーチャネル MOSFET による CMOS 集積回路の材料・プロセス技術の構築

#### ① 縦型ボディーチャネル MOSFET のデバイス技術の構築

縦型ボディーチャネル MOSFET のデバイス技術の構築に関しては、研究代表者の遠藤 Gr (東北大学)が実施した。hp32nm 世代のデバイスを精度よく試作することは困難であるため、例えば 65nm 世代での試作サンプルによる実験的手法と 32nm 世代以降の微細デバイスに対するデバイスシミュレーションによる理論的解析手法を組み合わせることで、hp32nm 世代以降における縦型ボディーチャネル MOSFET のデバイス設計理論の確立を目指した。

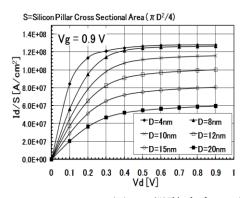

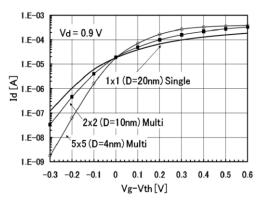

平成 22 年度は、試作した縦型ボディーチャネル MOSFET のデバイス特性を取得し、その評価結果を踏まえて、当該デバイスのチャネル不純物分布に対する設計技術の高精度化を行い、カットオフ特性を向上(図 1)させつつ、効率よく駆動電流をピラー中央に流すようにできるチャネル不純物分布と拡散層構造を提案した(学術論文に採択決定)。さらに、これらの知見をDRAM セルへと展開し、縦型 MOSFET からなる 4F² セルを実現できる 1Tr-DRAM セルと、1Tr-DRAM セルの課題であったリテンション特性を大幅に改善する縦型 MOSFET 型セル固有の動作法とセルアレイ構成を提案した(図 2)。さらに、10nm 以降の世代における縦型ボディーチャネル MOSFET の設計指針を探索するために、チャネル不純物分布がチャネルピラー中の電荷の伝導特性に与える影響を理論的に解明し、本提案のピラーの中央にも駆動電流を流す縦型ボディーチャネル MOSFET が、ON 状態におけるチャネルインピーダンスを最も低くできることを発見した(図 3)。(原著論文:1、2、3、4、6、7、10)

図 1 縦型ボディーチャネル MOSFET の特性

図 2 縦型 MOSFET からなる 1Tr-DRAM セル 図 3 ピラーチャネル中の電子伝導の挙動 (4F<sup>2</sup>セル)と、その動作原理

#### ② 縦型ボディーチャネルデバイスに基づく回路技術とその設計技術の構築

縦型ボディーチャネルデバイスに基づく回路技術とその設計技術の構築に関しては、研究 代表者の遠藤 Gr(東北大学)が実施した。

平成 22 年度は、昨年度に構築した縦型ボディーチャネル MOSFET による集積回路の高効率な回路ネットワークの合成とレイアウトパターンの生成技術を実際の小規模集積回路のレイアウトパターンに適用し、さらに、4 色グラフ理論を SPICE のネットリストへの直接適用の手法を開発することで、平面型 MOSFET ベースのパターンレイアウトを、縦型ボディーチャネル MOSFET ベースのパターンレイアウトに自動変換できるレベルまでの高度化に成功した。

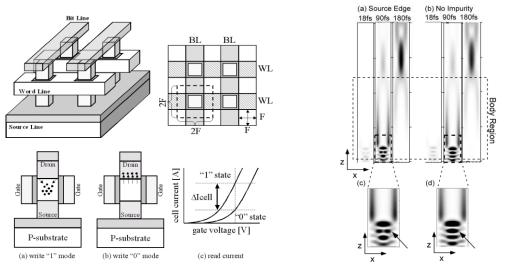

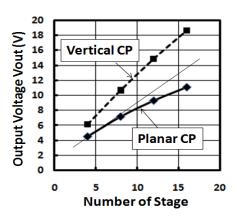

さらに、縦型MOSFET 固有の特徴を生かした新しいSRAM セルを提案した。そして、提案したSRAM セルが、リード動作に対するSNMと書き込み動作に対するSNMの両方に優れていること、及び、セルサイズが、既存の平面型MOSFETベースのSRAM セルに対して約60%にまで縮小できることを示すなど、縦型ボディーチャネル MOSFET で構成された本提案のSRAM セルの優位性を定量的に示した(図4)。さらに、縦型ボディーチャネル MOSFET の高い駆動能力と基板バイアス効果フリーの特徴を生かした縦型ボディーチャネル MOSFET による高性能昇圧回路を開発した(図5)。これにより現在のNAND型メモリのチップ面積を10%程度縮小することが可能となり、工業的にも大きなインパクトがあると考える。(原著論文:5、8、9)

図 4 提案した縦型 SRAM と SNM 特性の向上

図 5 提案した縦型 MOSFET による 昇圧回路特性の向上

③ 縦型ボディーチャネル MOSFET による CMOS 集積回路の材料・プロセス技術の構築 縦型ボディーチャネル MOSFET による CMOS 集積回路の材料・プロセス技術の構築に関 しては、研究分担者の小池 Gr(東北大学)と塚本 Gr(東京エレクトロン㈱)と研究代表者の遠藤 Gr(東北大学)が実施した。hp32nm 世代以降における単体の CMOS 縦型ボディーチャネル MOSFETの製造に必要となる基本ユニットプロセス技術の開発を行うと共に、プロセスインテグ レーション技術の開発を進めた。

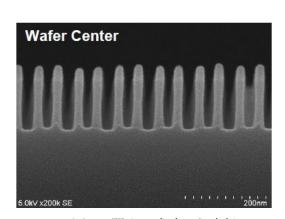

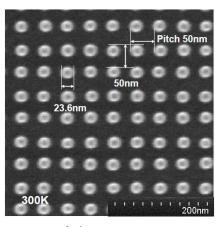

平成22年度は、塚本 Gr は、遠藤 Gr と連携して、3Xnm 世代のシリコン3次元加工技術の開発と、様々な面方位を有する微細シリコンピラー側面の均一な酸化技術の開発を推し進めることで、世界最小・最高密度となるhp50nmでのシリコンピラーのアレイ製造に成功した(図6)。

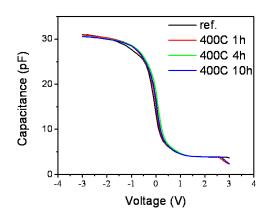

さらに、縦型ボディーチャネル MOSFET に適用する High-k/メタルゲートプロセス開発を目指して、米国 Albany に拠点を置く TEL テクノロジーセンターアメリカでの新しい試作環境を構築した。具体的には、hp32nm 世代以降の縦型ボディーチャネル MOSFET においては、被覆段差性の優れた High-k/メタル電極のプロセス技術が重要となるため、TEL 米国拠点にある原子層成長 (ALD: Atomic Layer Deposition)装置を用いた条件だしから実施し、実用化に優れたインテグレーション技術開発を行った。High-k 膜としては、高誘電率・酸化ハフニウム (HfO2) 膜に注力し、成膜プロセスの最適化や2段階プロセス技術を適用することにより、従来技術と比較してリーク電流密度が1桁以上低減することができた。この開発したプロセス技術は、従来技術と比較しても大差ないシンプルな技術であるため、研究目的である製造性に優れたシンプルなプロセスインテグレーション技術開発を実現できた。

さらに、昨年度開発した極微細シリコンピラー(Φ50nm、高さ150nm)を用いて、上記の本年開発の High-k/メタル電極のプロセス技術の適用を行った。試作設備の不備などのため、時間は掛かっているが、年度内にはシリコンピラーによるキャパシタ評価を行い、集積化プロセス技術の基本的問題点を抽出できる予定である。さらに、来期よりつくばイノベーションアリーナ(TIA)施設が活用できるため、最適化された High-k/メタル電極プロセス技術を用いたトランジスタ開発を行う予定である。

また、東北大学小池 Gr では、CMOS 縦型ボディーチャネルの基本ユニットしてのゲート、ソース、ドレイン電極の形成方法の確立を目指して研究を遂行し、シリサイドをプラズマ酸化してシリサイド表面に薄い SiO2 層を形成した後に、CVD 法による MnOx を形成することによって、シリサイドとCuコンタクトプラグ間の良好なバリア・コンタクト材料となる目処がついた。しかし、SiO2 に含まれる物理吸着水や化学吸着水が前駆体と反応することによって、MnOx の結晶性と膜厚に影響があることが判明した(図7)。従って22年度の研究は、吸着水分の影響に注目して MnOx の形成機構を明らかにすることを目的とした。

図 6 開発に成功した直径 23.6nm、hp25nm、高さ 120nm の シリコンピラーアレイの SEM 写真

図 7 Cu/MnOx/SiO2/Si 試料の熱処理後の C-V 曲線

#### § 4. 成果発表等

# (4-1) 原著論文発表

- ●論文詳細情報

- 1 T. Endoh, K. Sakui, Y. Yasuda," Design of 30nm FinFETs and Double Gate MOSFETs with Halo Structure", IEICE Transacions on Electronics, Vol.E93-C, No.5, pp.534-539, May, 2010

- 2 M. Muraguchi, T. Endoh, "Study on Quantum Electro-Dynamics in Vertical MOSFET", IEICE Transacions on Electronics, Vol.E93-C, No.5, pp.552-556, May, 2010

- 3 T. Endoh, K. Sakui, Y. Yasuda, "Sub-10nm Multi-Nano Pillar Type Vertical MOSFET", IEICE Transacions on Electronics, Vol.E93-C, No.5, pp.557-562, May, 2010

- 4 M. Muraguchi, Y. Takada, S. Nomura, T. Endoh, Kenji Shiraishi, "Importance of the Electronic State on the Electrode in Electron Tunneling Processes between the Electrode and the Quantum Dot", IEICE Transacions on Electronics, Vol.E93-C, No.5, pp.563-568, May, 2010

- 5 Koji Sakui and Tetsuo Endoh, "A Compact Space and Efficient Drain Current Design for Multi-Pillar Vertical MOSFETs", IEEE Transaction on Electron Devices, Vol.57, No.8, pp.1768-1773, August, 2010

- 6 M. Muraguchi, T. Endoh, Y. Takada, Y. Sakurai, S. Nomura, K. Shiraishi, M. Ikeda, K. Makihara, S. Miyazaki, Y. Shigeta, "Importance of Electronic State of Two-Dimensional Electron Gas for Electron Injection Process in Nano-Electronic Devices", Physica E, Vol.42, Issue10, pp.2602-2605, September, 2010

- 7 Y. Takada, M. Muraguchi, T. Endoh, S. Nomura, K. Shiraishi, "Proposal of a new physical model for Ohmic contacts", Physica E, Vol.42, Issue10, pp.2837-2840, September, 2010

- 8 K. Sakui and T. Endoh," High Efficient, Low Power, and Compact Charge Pump by Vertical MOSFET's", Solid-State Electronics, Vol.54, Issue10, pp.1192-1196, October, 2010

- 9 K. Sakui and T. Endoh,"A new vertical MOSFET "Vertical Logic Circuit (VLC) MOSFET" suppressing asymmetric characteristics and realizing an ultra compact and robust logic circuit", Solid-State Electronics, Vol.54, Issue11, pp.1457-1462, November, 2010

- 10 Vipul Singh, Hiroshi Inokawa, Tetsuo Endoh, and Hiroaki Satoh, "Fabrication Method of Sub-100nm Metal–Oxide–Semiconductor Field-Effect Transistor with Thick Gate Oxide", Japanese Journal of Applied Physics, Vol.49, No.12, pp.128002-1-128002-2, December, 2010

# (4-2) 知財出願

- ① 平成22年度特許出願件数(国内0件)

- ② CREST 研究期間累積件数(国内 4件)