「次世代エレクトロニクスデバイスの創出に資する革新材料・プロセス研究」 平成19年度採択研究代表者

H22 年度 実績報告

## 菅原 聡

## 東京工業大学像情報工学研究所•准教授

## ハーフメタル強磁性体を用いたスピン機能 MOSFET の開発

## §1. 研究実施の概要

本研究課題は、従来のエレクトロニクスの分野で用いられることのなかったキャリアのスピンや材料の磁性に関する自由度・機能を MOSFET に導入し、スピンの自由度を用いた新しいシリコン集積回路技術を構築するための基礎体系を創出することを目的としている。本研究課題は、①ハーフメタル強磁性体ソース/ドレイン・スピン MOSFET の開発、②強磁性トンネル接合(MTJ)を用いた擬似スピン MOSFET の開発(フルホイスラー合金 MTJ の開発を含む)、③スピン機能MOSFET(スピン MOSFET, 擬似スピン MOSFET)を用いた高機能集積回路の開発に関する3つの研究項目から構成される。

「ハーフメタル強磁性体ソース/ドレイン・スピン MOSFET の開発」ではスピン MOSFET 実現の要であるハーフメタルソース/ドレインの形成技術について研究開発を行った。ハーフメタル強磁性体であるフルホイスラー合金 Co<sub>2</sub>FeSi や Co<sub>2</sub>FeSi<sub>1-x</sub>Al<sub>x</sub>を CMOS プロセスに整合できる RTA によるシリサイド化反応を用いて形成することに成功した。さらに、フルホイスラー合金のハーフメタル性に重要な規則度の評価方法を新たに提案・確立して、本方法によって、RTA によって形成したフルホイスラー合金が極めて高い規則度を有することを明らかにした。また、この RTA 法はドーパントの界面偏析現象を用いたバリアハイト制御、フルホイスラー合金を強磁性電極とした Si へのトンネルコンタクト構造の形成、フルホイスラー合金のフェルミレベル制御にも応用できることを明らかにした。今後、以上の成果を用いて、ハーフメタルをソース/ドレインとするスピン MOSFET の実現を目指す。

「MTJを用いた擬似スピンMOSFETの開発(フルホイスラー合金MTJの開発を含む)」では通常の MOSFET と MTJ を回路的に組み合わせ、スピン MOSFET と同等の動作を実現できる (MRAM 技術で実現できる) 擬似スピン MOSFET を提案し、研究開発を行った。 MTJ の高精度な SPICE モデルを開発して、擬似スピン MOSFET の性能予測・設計法を確立した。 また、非晶質 SiO2 上にフルホイスラー合金を電極とする高性能な MTJ の形成技術を確立し、MTJ と MOSFET を集積化することによって、擬似スピン MOSFET の機能実証を行った。 また、フルホイスラー合金を用いた MTJ の革新的な高性能化(高 TMR 化、高 Vhalf 化)を実現し、さらにはフルホイスラー合金を用いた CPP・GMR デバイスによって、ホイスラー合金を用いることによるスピン注入磁化反転の低閾値電流化の可能性を実証した。 今後、これらの開発技術の集約を行い擬似スピン MOSFET の基盤技術を確立する.

「スピン機能 MOSFET を用いた高機能集積回路」では、擬似スピン MOSFET を用いた不揮発性 SRAM と不揮発性フリップフロップを提案し、研究開発を行った。開発を行った擬似スピン MOFET のシミュレーション技術を駆使して、これらの回路の動作検証・性能評価を行った。特に、Break-even time を用いたパワーゲーティング・システムへの適合性の評価方法を提案・確立し、提案した不揮発性 SRAM と不揮発性フリップロフロップが十分にパワーゲーティングに応用可能な性能を有していることを明らかにした。この不揮発性 SRAM と不揮発性フリップロフロップを用いた不揮発性パワーゲーティング・システム(マイクロプロセッサおよび FPGA)の提案を行った。

## § 2. 研究実施体制

- (1)「東工大」グループ(研究機関別)

- ①研究分担グループ長:菅原 聡 (東京工業大学、准教授)

- ②研究項目

RTA によるハーフメタル・フルホイスラー合金の形成とその S-MOSFET への応用 PS-MOSFET の性能評価と機能実証 PS-MOSFET, S-MOSFET を用いた高機能ロジックの提案・設計と性能予測

- (2)「NIMS」グループ(研究機関別)

- ①研究分担グループ長:猪俣 浩一郎 ((独)物質・材料研究機構、名誉フェロー)

- ②研究項目

巨大 TMR 比ハーフメタル MTJ の作製, MR 比の大きい CPP-GMR 素子の作製および低電流スピン注入磁化反転技術開発

PS-MOSFET の作製と機能実証

PS-MOSFET を用いた高機能ロジックの作製と評価

- (3)「東大」グループ(研究機関別)

- ①研究分担グループ長:田中 雅明 (東京大学、教授)

- ②研究項目

PS-MOSFET の作製と機能実証

PS-MOSFET を用いた高機能ロジックの作製と評価

#### § 3. 研究実施内容

本研究課題は、以下の3項目から構成される.以下、スピンMOSFETをS-MOSFET、擬似スピンMOSFET(Pseudo-spin-MOSFET)をPS-MOSFETと略す.研究項目は①ハーフメタル強磁性体ソース/ドレインS-MOSFETの開発、②強磁性トンネル接合(MTJ)を用いたPS-MOSFETの開発(フルホイスラー合金 MTJ の開発を含む)、③スピン機能 MOSFET(S-MOSFET, PS-MOSFET)を用いた高機能集積回路の機能実証の3つである.それぞれの研究項目について、研究計画と成果を示す.

## ①ハーフメタル強磁性体ソース/ドレイン S-MOSFET の開発 【研究のねらい】

スピン MOSFET を実現するための重要課題は、ハーフメタル強磁性体(HMF)による強磁性ソース/ドレイン(S/D)技術の開発である。スピン MOSFET はそのデバイス構造から近年注目を集めているメタル S/D MOSFET の一種であると考えられるが、CMOS プロセスに整合できる HMF メタル S/D の形成と HMF/Si 接合におけるバリアハイト制御が重要な課題になる。そこで、RTA によるシリサイデーションを用いたフルホイスラー合金の形成方法を確立し、この方法によって高品質のフルホイスラー合金が形成できることを示す。このために重要となるフルホイスラー合金の規則構造の評価方法についても合わせて開発を行う。また、HMF/Si 接合におけるバリアハイトの制御が重要な課題になるが、これについても CMOS 技術で検討されている方法を適応する。すなわち、ショットキー接合におけるドーパントの界面偏析と、薄いトンネル膜を用いたデピン構造を採用してバリアハイトの制御を行う。(複数の方法でバリア高さ制御を行うのは、この系がこれまでにない新しいものであることから探索的アプローチが必要な状況にあるためである。)次に、これらの接合構造を用いて、Si 中へのスピン注入を行い、Si チャネル内でのスピン伝導の精密な評価を行う。このためのスピン注入/伝導の評価方法も確立する。最終的には、これらの接合構造を S/D としたスピン MOSFET の動作実証を行う。

## ①-1 RTA によるハーフメタル・フルフルホイスラー合金の形成(東工大) 【研究計画と実施方法】

CMOS プロセスに整合する手法でハーフメタル強磁性体を形成する. SOI(Si-on-insulator)基板を用いて、Rapid thermal annealing (RTA)によるシリサイド化反応を利用することによって、HMF となる L21 構造フルホイスラー合金(図 1 参照)の構造制御・物性制御などを行う. RTA による L21 構造フルホイスラー合金  $Co_2FeSi(CFS)$ の形成法をベースとして、(i)フルホイスラー合金のハーフメタル性に重要な規則度の評価方法を確立する. (ii)CFS に含まれるIV族元素 Siの一部を III族元素である Al などに変えることによって( $Co_2FeSi_xAl_{1-x}$ ; CFSA)、フェルミ準位の制御を行う。また、ショットキー接合のデピンニングのため、(iii)薄い絶縁膜上に CFS、CFSA を形成する. このために、非晶質絶縁体上に形成したアモルファス Si を用いて、上記と同様の手法によってフルホイスラー合金を形成する方法を確立する.

## \*重要マイルストーン:RTAを用いたSOI基板上,非晶質絶縁膜上へのフルホイスラー合金の形成技術の確立および規則度の評価技術の確立 【研究成果】

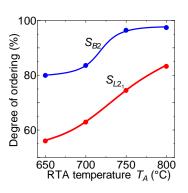

(100)面 SOI(Si-on-insulator)基板上に CoとFeを堆積して、RTAによるシリサイド化によって CFS 薄膜を形成した。この RTAによって形成した CFS 薄膜の構造評価を詳細に行った。 XRD、 SIMS、RBS、PIXIE、TEM の詳細な評価から、RTAによって形成した CFSは、(110)面に完全 に配向したテクスチャ構造をとり、また、ハーフメタルとなることが予測される L21 構造を持つことなどがわかった。フルホイスラー合金のハーフメタル性はその規則度に強く依存しているため、フルホイスラー合金の規則度の評価技術を新たに確立した。 従来用いられてきた Webster による方法の問題点を指摘し、これを修正した解析モデルを提案し、このモデルを用いて RTAによって作製した CFS 薄膜の規則度を定量的に評価することに成功した。 RTAによって形成した Co2FeSi 薄膜の規則度の RTA 温度の依存性などを明らかにして、この薄膜がバルクと同程度の極めて高い

規則度を有することを明らかにした(図 2). また、フルホイスラー合金の L21 構造には通常の X 線回折では評価できない DO3 構造と呼ばれるディスオーダーが存在することが近年明らかになってきた(評価には NMR やシンクロトロン放射光などの大掛かりな装置が必要). DO3 不規則化構造は A2 構造と呼ばれる不規則化の一種であるためフルホイスラー合金のハーフメタル性を大きく劣化させるが、通常の X 線回折では検出できない. そこで、Co 線源 X 線回折を用いた DO3 不規則化の新しい評価方法を提案した. 本手法は Co 線源 X 線による Fe と Co の原子散乱因子の大きさの違いに着目した方法で、DO3 不規則化を定量評価できる. RTA によって作製した CFS 薄膜の DO3 不規則化は RTA 温度とともに減少し、RTA 温度では RTA 温度では RTA 温度できることを明らかにした(図 3).

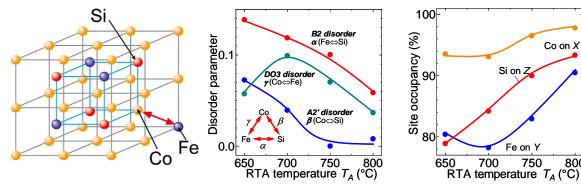

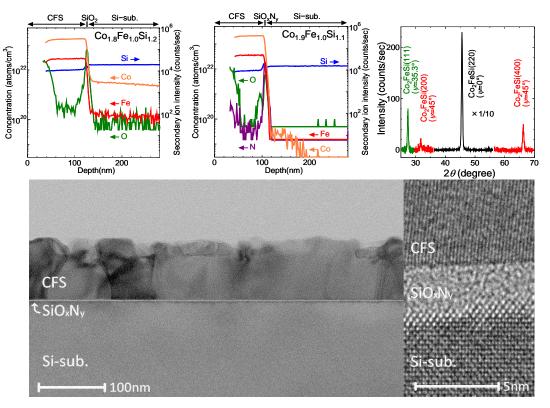

以上のフルホイスラー合金の形成方法は、フルホイスラー合金とSiのショットキー接合に応用できる。次節で述べるドーパントの界面偏析を用いたバリアハイト制御に応用できる。一方、ショットキー接合の界面に薄いトンネル膜を挟み込んで接合のデピンニングを行いバリアハイト制御を行う方法では薄い絶縁体薄膜(トンネルバリア)上に直接フルホイスラー合金を作製する必要がある。そこで、非晶質絶縁体上に堆積したアモルファス Si を用いて、RTA によってフルホイスラー合金を形成する方法を提案し、実際にこの方法を用いれば絶縁膜(SiO2)上に直接 L21 構造の規則度の高い CFS が形成できることを明らかにした。この結果は厚い SiO2 上のものであるが、次に薄いSiO2、SiNを用いてトンネルコンタクトの形成を試みた。まず、2nm 程度の薄い熱酸化膜の場合、RTA によって Co、Fe は熱酸化膜を透過して Si 基板中の奥深くまで拡散してしまうこと明らかにして、密度が緻密で遷移金属の透過抑止能力に優れた SiN をトンネルバリアに用いることを提案した。この場合では、Co、Fe の透過は大きく抑止され、また、形成した CFS は薄いトンネルバリア上であっても規則度の高い高品質の CFS が形成できることを示した(図 4)。

次いで、フェルミレベルを制御できる  $Co_2FeSi_{1-x}Al_x(CFSA)$ の RTA による形成の検討を行った。 CFSA は Al の組成によって、そのフェルミレベルをマイノリティギャップの中心近傍に配置させることが可能なため、スピン注入に適したハーフメタル材料である。 本研究課題では CFS の開発によって得られた知見を CFSA にフィードバックして、より高性能なスピン MOSFET の実現を目指す。 まず、RTA による CFS の形成と同様の方法によって CFSA の形成を試みた。 Co、Fe、Al、SOI の多層膜を RTA した場合、膜は激しいラフニングを起こして高品質の CFSA が得られないことを明らかにした。 また、CFSA の  $SiO_2$  上への直接スパッタでは、アニールを行っても規則構造は得られないことを示した。 そこで、 SOI 上に Co-Fe-Al 合金( $Co_2FeAl_{0.5}$ )をスパッタ堆積し、RTA によってシリサイド化する方法を提案した。 この場合では、 $L2_1$  構造の CFSA が形成できることを明らかにした。

#### \*重要マイルストーン:クリア

- ①-2 フルフルホイスラー合金/Si 接合の形成とバリアハイト制御(東工大)

- ①-3 フルホイスラー合金メタル・ソース/ドレイン MOSFET の試作とそのトランジスタ性能評価 (東工大)

[同時に行う項目のため,以下にまとめて記述する]

#### 【研究計画と実施方法】

強磁性体から半導体へのスピン注入では、強磁性体/半導体接合におけるバリアハイトの制御が重要になる。本研究課題ではフルホイスラー合金/シリコン界面に形成されるショットキー障壁を制御するため、(i)シリサイド化反応におけるドーパントの偏析現象を利用する。低エネルギーのイオン注入などによって Si 表面にドーパントを導入してから、RTA によるシリサイド化反応によってフルホイスラー合金を形成する。このとき、高濃度のドーパントがフルホイスラー合金とシリコンとの接合界面の非常に狭い範囲内に偏析する。この高濃度に偏析したドーパントの効果によってショットキー障壁高さを下げる(または障壁幅を極端に薄くする)。また、(ii)フルホイスラー合金と Si の界面に非常に薄い絶縁膜を導入してデピンニングを行い、仕事関数制御によるバリアハイト制御を試みる。さらに、(iii)N+ソース/ドレイン領域へフルホイスラー合金のシリサイド化(または直接形成)を行い、フルホイスラー合金による N+領域へのトンネルコンタクトの検証を行う。

CFS, CFSAを S/D とした MOSFET を作製し、この電気特性から CFS, CFSA/Si 接合に関連する評価を行う。プロセスが容易であることとプロセス温度の低温化が容易であることから、トランジスタ構造としては SOI 基板を用いたボトムゲート構造とする。このデバイスのオン特性およびオフ特性から CFSA/Si 接合に関する諸特性および接合のバリアハイト制御の効果を検証する。

\*重要マイルストーン: CFS メタル S/D 構造にドーパントの界面偏析効果を応用し, バリアハイト減少を確認

#### 【研究成果】

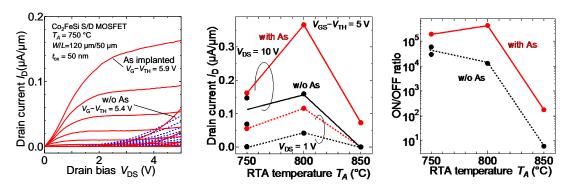

SOI 基板を用いた RTA による CFS の形成技術を利用して、CFS をメタル・ソース/ドレインとしたスピン MOSFET の試作を行った。CFS のフェルミレベルが Si のギャップ中の深い位置にピンニングされ、電流駆動能力は低いが、両極性動作となるがトランジスタ特性を確認することができた。次に、ドーパント不純物の界面偏析現象を利用してバリアハイトの低減技術の検討を試みた。エネルギー10keV、ドーズ量 1×10<sup>15</sup> cm<sup>-2</sup>で As のイオン注入をソース/ドレイン領域に行い、この領域に Fe と Co を堆積して、RTA によるシリサイド化を行い CFS を形成した。この場合では MOSFET のオン電流が大きく増大して、As の界面偏析によると考えられるバリアハイトの低減が確認された(図 5)。このドーパントの界面偏析現象によるバリアハイト制御を MOSFET の電気特性から詳細に評価した(図 5)。As の界面偏析を行うことで、電流駆動能力は大きく改善された。また、As の界面偏析によって、オン/オフ比は増大し、S ファクタおよび閾値は減少した。ドーパントの界面偏析技術がフルホイスラー合金/Si ショットキーバリアにも適応できることを明らかにした。

また、薄い絶縁膜を用いたデピン構造に関しては、 $\hat{\mathbb{O}}-1$  に述べた。SiN を用いれば、遷移金属の拡散を抑止し、高品質の CFS 電極となる CFS/SiN/Si 接合が形成できることを明らかにした。 CFS のデバイス応用可能な界面偏析ショットキーコンタクト (CFS/As/Si) とトンネルコンタクト (CFS/SiN/Si) について目処をつけることができた。

#### \*重要マイルストーン:クリア

## ①-4 フルホイスラー合金/Si 接合によるスピン注入とスピン伝導の実現(東工大) 【研究計画と実施方法】

CFS,CFSA/Si 接合を S/D としたスピン注入/スピン伝導の評価デバイスを作製し、スピンバルブ効果, Hanle 効果などから、スピン注入/スピン伝導を評価する. 高効率のスピン注入を実現できるフルホイスラー合金/Si 接合の構造や、CFSA のフェルミエネルギー制御の最適化を行う.

\* 最重要マイルストーン:フルホイスラー合金による Si 中へのスピン注入とスピン伝導による信号 検出.

## 【研究成果】

非局所/局所配置マルチターミナルデバイスを設計し、デバイス作製プロセスの確立した. テストデバイスにおいて非局所配置におけるスピンバルブ効果を観測した. 正確にスピン注入/スピン伝導の評価を行うためには Hanle 効果に基づく評価が必要不可欠であるため、スピン注入・スピン伝導を的確に評価できる新構造磁気伝導評価デバイスを提案・設計した. また、この提案デバイスの作製プロセスも確立した. 今後、本デバイスを作製して、スピン注入/スピン伝導の評価を行う.

#### \*最重要マイルストーン:次年度内でクリアの予定

## ①-5 フルホイスラー合金メタル・ソース/ドレイン スピン MOSFET の作製・評価(東工大) 【研究計画と実施方法】

本研究項目が、本研究課題全体における基礎研究部分の最終目標となる重要課題となる. (本研究項目の結果を受け、スピンMOSFETを実際に集積回路に応用する際の重要目標として次項目 $\mathbb{Q}-6$ を行う。)上記 $\mathbb{Q}-1$ から $\mathbb{Q}-4$ の結果から最適なスピンMOSFETのデバイス構造を決定し、試作・評価を行う。スピンMOSFETにおけるスピン依存伝達特性を実現して、その機能実証を行う。

\*重要マイルストーン:スピン MOSFET の動作確認(磁化状態依存出力特性の実証) 【研究成果】 ①-4と同時に進行中、プロトタイプデバイスの設計終了、現在デバイスの作製中、

\*重要マイルストーン:今後の本 CREST のメインテーマである. 期間内に達成予定

## ①-6 スピン MOSFET へのスピン注入磁化反転の導入(東工大・NIMS)

#### 【研究計画と実施方法】

スピン MOSFET を集積回路上で有効に用いるために必要となるスピン注入磁化反転をスピン MOSFET に応用する. 下記②-2 で開発するフルホイスラー合金を用いた CPP-GMR 構造のスピン注入磁化反転を, スピン MOSFET のソースまたはドレインに適応させて, スピン注入磁化反転可能なスピン MOSFET を実現する.

\*重要マイルストーン:フルホイスラー合金を用いた CPP-GMR 構造におけるスピン注入磁化反転の機能実証

#### 【研究成果】

2-1 に記載.

\*重要マイルストーン:クリア

## ②比強磁性トンネル接合を用いた PS-MOSFET の開発

#### 【研究のねらい】

本研究項目ではMTJと通常のMOSFETを組み合わせたPS-MOSFETを作製し、機能実証を行う.PS-MOSFET は既存のMRAM 技術を利用してスピントランジスタによる集積エレクトロニクスを展開する基盤技術となる.PS-MOSFET は究極的にはスピン MOSFET に及ばないが、これを用いれば、"スピントランジスタ"を早期にしかも比較的に容易にCMOS に取り込むことが可能となる.PS-MOSFET によってスピンの自由度を用いた新しいSi集積エレクトロニクスの基礎体系を創出することができることを示す。CMOS集積回路への応用を念頭においた高性能MTJを含むPS-MOSFET技術の開発を行う。

## ②-1 巨大 TMR 比ハーフメタル MTJ の作製(NIMS)

#### 【研究計画と実施方法】

これまでフルホイスラー合金を用いた高TMR比のMTJはすべて単結晶のMgO(100)基板上に作製されてきたが、MOSFETとの集積化を試みるため、 $SiO_2$  (熱酸化膜上または層間絶縁膜)上に高TMR比のMTJを作製する技術開発を行う。方法としてまず、 $SiO_2$ 上に(100)配向したフルホイスラー合金を作製するためのバッファー層の検討を行うとともに、最適熱処理条件を探る。その結果を受けて、TMRの大きいMTJを $SiO_2$ 基板上に作製する技術を開発する。フルホイスラー合金としてはまずは100%のTMRを得ることを目途に、開発済みの $Co_2$ FeAl<sub>0.5</sub>Si<sub>0.5</sub>(CFAS)を使用する。その後、プロセス改善とともにフルホイスラー合金の組成を検討し、TMRの向上を目指す。

## \*マイルストーン:第一段階:1 年後, TMR 比 100%, 第二段階:3 年後, 室温で TMR 比 300% 【研究成果】

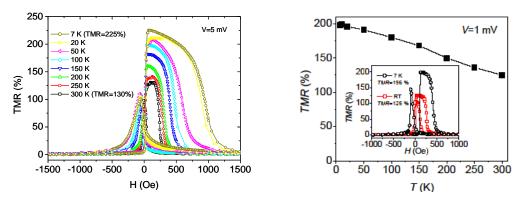

SiO<sub>2</sub> 基板上に MgO バッファを形成し熱処理温度を検討した結果,高度に(100)配向した CFAS フルホイスラー合金薄膜を作製することができた.この結果に基づき,Ta/IrMn/CoFe/CFAS/MgO/CFAS/MgO バッファ/SiO<sub>2</sub>/Si MTJ を作製した. CFAS に対する熱処理温度を最適化することで、室温において 130%という、期初目標(100%)を上回る高い TMR 比を得ることができた(図 6). 熱酸化 Si 基板上にフルホイスラー合金を用いて作製した MTJ は世界でこれが初めてである。開発した CFAS が実際ハーフメタルであるか否かの検証実験を行うため、コヒーレントトンネル効果による TMR のエンハンスが除外される AlOx バリアを用いて CoFe/Mg/AlOx/CFAS MTJを MgO(100)基板上に作製し、TMR の温度変化とともに微分コンダクタンス dI/dV のバイアス電圧依存性を測定した. その結果、低温(26 K)で 162%、室温で 102%の TMR を得た. Julliere モデルから TMR = 162%はスピン分極率 P = 0.93 に相当し(P (CoFe) = 0.5)、CFAS はハーフメタルであることを実証した. 尚、室温 TMR = 102%は P = 0.75 に相当

し、この値はこれまでの全ての磁性材料の中で最大である。一方、dI/dV のバイアス電圧依存性から CFAS は室温でもハーフメタルギャップを有することを確認した。室温でのハーフメタルギャップ の観測は世界初である。さらに TMR の温度変化を解析した結果、P の温度変化が  $T^{3/2}$ (スピン波理論)に従うことで完全に説明できることを明らかにした。これにより如何にすれば室温 TMR を増大できるかの指針を得た。この指針に基づき室温で巨大 TMR を実現すべく組成の検討を行い,ホイスラー合金として  $Co_2FeAl(CFA)$  を用い,スパッタ法により IrMn/CoFe/CFA/CoFe/MgO/CFA/Cr/MgO(100) スピンバルブ MTJ を作製し,10 K で 785%,室温で 360%の巨大 TMR を得た(図 7)。この室温 TMR はスピンバルブ型 MTJ として世界最高値である。現在, $SiO_2$  基板上にこの MTJ を作製することを行っている。

## \*重要マイルストーン:クリア

## ②-2 低電流スピン注入磁化反転技術の開発(NIMS) 【研究計画と実施方法】

本研究課題ではフルホイスラー合金に対して、スピントランスファートルク(STT)に基づくスピン注入磁化反転(Current-induced magnetization switching: CIMS)を実現する。CIMSはナノ磁性体の磁化反転のスケーリングを可能にするスピントロニクスの革新的な技術であるが、一般にスイッチングのための臨界電流密度が $10^7 A/cm^2$ 程度と大きいことが課題である。本研究は、(a)開発したフルホイスラー合金を用いてMR比の大きいCPP-GMR材料を開発、その微小素子に対してCIMSの低電流密度化を実現し、S-MOSFETへの適用をはかる。(b)開発したフルホイスラー合金を用いて低抵抗でTMR比の大きいMTJ素子を作製し、CIMSを実現してPS-MOSFETへの適用化をはかる。

## \* 重要マイルストーン:スピン注入磁化反転電流密度:5×10<sup>6</sup> A/cm<sup>2</sup> 以下(MTJ 素子) 【研究成果】

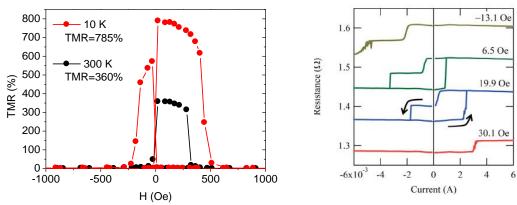

まず、CIMS を観測するための微細加工技術および評価装置・技術を立ち上げた、次に、従来の Cu に代えて Ag スペーサを用いた CoFe/CFAS/Ag/CFAS/Cr/MgO(100)スピンバルブ型 CPP-GMR 微小素子を作製し、熱処理条件を最適化することで、室温で 12.5%の大きな GMR 比を得た、従来の CoFe フリー層を用いた場合の CPP-GMR 比が 1%未満であることを考えれば、この値は非常に大きな値である。このときのフリー層 CFAS の厚さは 30 nm であった。CIMS を観測するため、この厚さを 2.5 nm に薄くした素子を作製した結果、この場合も 9%の大きな CPP-GMR を得た。この結果を受けて、微細加工技術を用いて上記構造からなる楕円形 (250×190 nm)のナルプラーを作製し、明瞭な CIMS を観測した (図 8)。磁化反転電流の分布から CIMS の臨界電流密度  $J_{co}$  を評価した結果、 $J_{co}$  =  $9.3\times10^6$  A/cm² であった。この  $J_{co}$  は従来の Co/Cu/Co CPP-GMR 素子に対する値の 20%という非常に小さな値である。これにより、CFAS フルホイスラー合金は CIMS の低電流密度化に有効であることを実証した。ホイスラー合金を用いて CIMS を観測したのはこれが世界初である。尚、CPP-GMR 比はその後、室温で 36%まで向上している。現在、MTJ 素子に対する CIMS の観測を研究中であり、厚さ 2.5 nm の CFAS を用いた低抵抗  $(5\Omega\cdot\mu m^2)$  MTJ を作製し、TMR > 100%を実現している。低電硫密度化が期待される。

## \*重要マイルストーン:次年度内でクリアの予定

## ②-3 PS-MOSFET の作製と機能実証(東工大・NIMS・東大) 【研究計画と実施方法】

MTJと MOSFET を組み合わせた PS-MOSFET を作製し、機能実証を行う. デバイスデザインには本研究課題で開発するシミュレータを用いる(③-1 参照). MTJ の開発段階にあわせて、PS-MOSFET を試作し、機能評価を行う. まずは、TMR のみに着目して機能実証を行う. その後、スピン注入磁化反転による機能実証を目指す.

はじめに、SOI 基板を用いたボトムゲート構造 MOSFET を用いて MTJ との集積化を行い、基本的な機能実証を行う. 次いでトップゲート構造 MOSFET を用いた構造に変更する. このトップゲート構造 MOSFET は外注ベンダーによる CMOS プロセスを用いる

## \*最重要マイルストーン:ボトムゲート構造の PS-MOSFET を作製およびそのスピントランジスタ 動作の実証

## 【研究成果】

SOI 基板を用いたボトムゲート MOSFET に関しては、As をソース/ドレイン領域のドーパントに用いて、良好な特性を有するボトムゲート MOSFET を実現した。実効移動度の実効電界依存性はユニバーサルカーブにほぼ一致し、また、サブスレショルド・スロープも100mV/decade以下と急峻な値となることを確認した

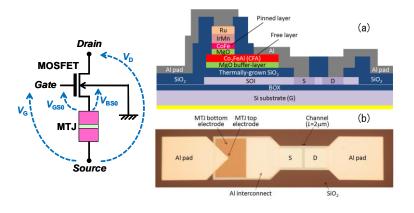

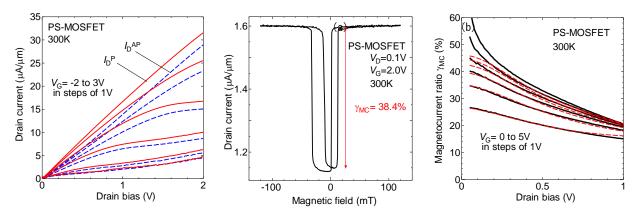

このボトムゲート構造MOSFETとフルホイスラー合金を用いた交換バイアス型のMTJを集積化して、PS-MOSFET の動作を検証した。MgO (10nm)/Co<sub>2</sub>FeAl (30nm)/Mg (0.5nm)/MgO (1.5nm)/CoFe (5nm)/IrMn (12nm)/Ru (7nm)の構造からなるMTJを原子スケールで平坦な熱酸化シリコン膜上に形成してMOSFETとの集積化を行った(図 9). 作製したPS-MOSFETの出力特性は、MTJ の磁化状態に依存して電流駆動能力が変化するスピン依存伝達特性が明瞭に観測され、PS-MOSFETがスピントランジスタとして動作できることを実証した。MTJの電気特性を我々の開発したSPICEのマクロモデルで再現し、PS-MOSFETの出力特性をシミュレーションして実験結果と比較を行った。その結果、シミュレーション結果と実験結果とよく一致し、疑似スピンMOSFETの動作実証ができた。45%の比較的大きな磁気電流比を観測することができた(図 10)。

#### \*最重要マイルストーン:クリア

## ②-4 PS-MOSFET 作製のためのプロセス技術の開発(東大)

#### 【研究計画と実施方法】

はじめに、SOI基板を用いたボトムゲート構造MOSFETとMTJの集積化によるPS-MOSFETの作製プロセスを開発する。東大・Gで作製するボトムゲート構造MOSFET上にNIMS・GでMTJを成膜して、再び東大・Gで加工を行いPS-MOSFETを作製する。デバイスの設計は東工大・Gで行う。特に、電子線リソグラフィーを用いた高精度な位置合わせ技術の確立をおこなう。

次に、外注ベンダーによる数百ナノメートルのプロセスによるCMOS基板にMTJを集積化して、より高精度な機能の実証(スピン注入を含む)をおこなう。この目的のために、外注ベンダーのCMOS基板表面の平坦化、およびこのCMOS基板上での高精度な位置あわせ技術などの確立をおこなう。また、スピン注入磁化反転をCMOS基板上で実現するために、MTJの微細加工技術を確立する.

#### 【研究成果】

ボトムゲート構造の PS-MOSFET に関しては、デバイス作製加工技術(EB 描画装置による高精度な位置あわせ、表面絶縁膜の堆積、コンタクトホールのエッチングによる形成、電極間配線の形成)を確立し、デバイスプロセスの確立を行った.

外注ベンダーCMOS 基板にMTJを集積化して実現するトップゲート構造 PS-MOSFETでは、 外注ベンダーCMOS 基板の表面平坦性に関する以下の様な問題が明らかとなった:1) 外注ベン ダーCMOS 基板の表面ラフネスは RMS 数 nm 程度であり、MTJ の TMR を著しく減少させる. 2) 外注ベンダーCMOS 基板は、本研究課題の該当集積回路チップ部の周辺領域の全てがレー ザーにより焼き切られている状態であるため(コスト面からシャトルプロセスを用いているため、本研 究で用いる回路チップの周りは他の相乗り回路チップ部である)、この領域内での表面ラフネスは 非常に大きく、また、このラフネスはチップ間によって大きくばらつく。(この周辺領域は回路動作に はもちろん不要であるが、プロセス上の必要なサンプルの大きさを確保するために必要である。)

外注ベンダーCMOS 基板における表面ラフネスの RMS を前記ボトムゲート構造の PS-MOSFET の場合と同程度( $\sim 0.2 \mathrm{nm}$ )にするために、CMP による表面平坦化プロセスを行った. 集積回路のコンタクトパッドを保護するために、表面に  $100 \mathrm{nm}$  の  $\mathrm{SiO}_2$ をスパッタにより堆積し、中性スラリーを用い圧力と研磨時間を条件として CMP をおこなった. 結果として、研磨中の圧力がある一定値以上では、RMS0.2 $\mathrm{nm}$  程度の表面が得られた. しかしながら、周辺領域(レーザ

一加工によって配線構造を焼き切っている他の相乗り回路チップ部)からの研磨屑の再付着や再現性が取り辛いことが問題として残った。これは上記問題点2)に起因していると考えられる。そこで、はじめに周辺領域を手研磨により荒削りを行い、次に CMP をおこなった。研磨屑の再付着や再現性の問題点は完全には解決していない。現在は、厚い  $SiO_2$ を用いる方法や、CMP 時に厚さの同じ数枚のダミー基板を用いることなどにより、問題の解決に取り組んでいる。

微細加工に必要な「電子線描画による 100nm 程度のパターン描画技術」に関しては、ダミー基板により技術を確立する見通しがたった.

## <u>③スピン機能 MOSFET(PS-MOSFET, S-MOSFET)を用いた高機能ロジックの開発</u> 【研究のねらい】

S-MOSFET および PS-MOSFET による"不揮発な情報の保持"と"再構成可能な出力"といった新たな自由度を用いた新概念のアーキテクチャによる高性能・多機能集積回路を創出する. 特に、ロジックシステムの低消費電力化に極めて有効なパワーゲーティング・システムにおいて最も重要となる不揮発性 SRAM(NV-SRAM)や不揮発性フリップ・フロップ(NV-FF)に注目して回路技術の開発を行う. マイクロプロセッサと FPGA をパワーゲーティングの具体的な対象として、PS-MOSFET を中心とした技術開発を行う.

## ③−1 PS-MOSFET と S-MOSFET を用いた回路シミュレータの開発(東工大) 【研究計画と実施方法】

MTJ の TMR 比, Vhalf, 面積抵抗積(RA), スピン注入磁化反転のダイナミクスを取り込んだ MTJ の SPICE モデルを開発する. フルホイスラー合金系 MTJ やその他 CoFeB 系などの MTJ の諸特性や, スピン注入磁化反転なども実験結果と精度よくフィットできるモデルを開発する. この MTJ モデルを用いて PS-MOSFET の性能予測と設計指針の確立を行う. 本研究課題で開発するシミュレーション技術を回路設計のみならずデバイス設計・材料設計に反映させる.

## \*重要マイルストーン: MTJ の SPICE モデルを構築し, PS-MOSFET の設計・性能予測を行う. 【研究成果】

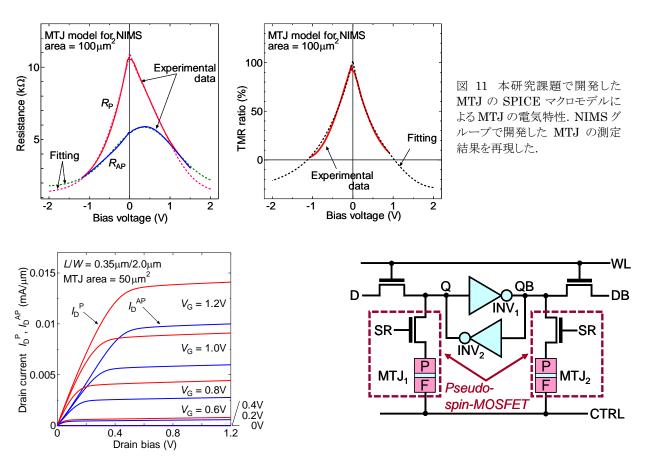

MTJ の TMR 比, Vhalf 依存性, RA, スピン注入磁化反転などを取り込んだ現実的な SPICE モデルを開発した。この SPICE モデルは NIMS グループによって開発した非晶質絶縁膜(SiO2) 上に作製したフルホイスラー合金 MTJ の電気特性を完全にフィットできる(図 11). (CoFeB 系の MTJ に関しても精度良くフィットできる)この MTJ の SPICE モデルを用いて、PS-MOSFET の機能予測を行い、設計指針を得た。まず、PS-MOSFET がスピン MOSFET として機能できることを確認した。また、MTJ の TMR 比、RA などから所望の磁気電流比を実現するための、設計指針を得た。ここで得られた知見をもとに、実際に作製する PS-MOSFET のデバイスデザインを行った(試作結果は②・3 に記載)。また、試作を予定している 350nm のベンダーCMOS プロセスによる PS-MOSFET の動作検証・性能評価を行い、試作のためのデバイス・回路設計も行った(図 12). \*重要マイルストーン: クリア

## ③-2 PS-MOSFET, S-MOSFET を用いた高機能ロジックの提案・設計と性能予測(東工大) 【研究計画と実施方法】

PS-MOSFET (または S-MOSFET) をインバータ・ループによる双安定回路の記憶ノードに接続すれば、NV-SRAM、NV-FF などのパワーゲーティングに重要な不揮発性記憶回路を構成できる. はじめに PS-MOSFET を用いた NV-SRAM、NV-FF の性能予測を行うともに、回路設計技術の確立する. また、PS-MOSFET を用いた NV-SRAM、NV-FF のパワーゲーティング・システムへの適応性の評価を行い、具体的なマイクロプロセッサや FPGA への応用について検討を行う. さらに、NV-SRAM、NV-FF 試作のためのデバイス・回路設計を行う.

PS-MOSFET (またはS-MOSFET)を用いてCMOSインバータを構成すると、その論理閾値を磁化状態で変化させることができる.この論理閾値可変インバータの設計と回路性能評価を本研究課題で開発するシミュレータを用いて行う.また、このような論理閾値可変インバータの応用につ

いても検討する.

\*最重要マイルストーン:提案した PS-MOSFET を用いた不揮発性 SRAM, 不揮発性フリップ・フロップの動作検証・性能予測技術の確立およびパワーゲーティング・システムへの適応性の評価方法を提案・確立.

#### 【研究成果】

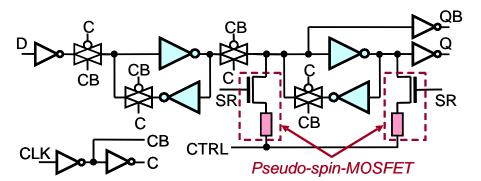

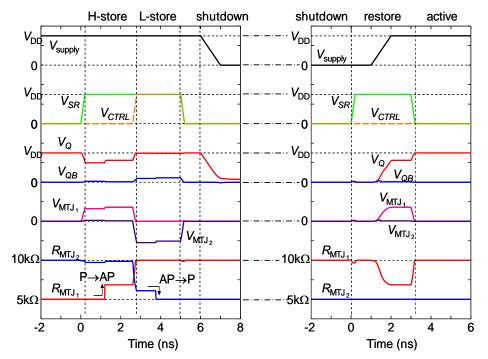

PS-MOSFET を用いた NV-SRAM と NV-FF を提案した(図 13, 14). また, 我々の開発した MTJ の SPICE モデルを用いたシミュレーションから, 提案した NV-SRAM, NV-FF の動作確認 を行うとともにその性能予測を行った(図 15). 特に, Break-even time (BET)を用いたパワーゲーティング・システムへの適合性の評価方法を提案・確立した.

NV-SRAM に関してはストア、リストア動作に与える MTJ 特性の影響から NV-SRAM の設計について検証し、MTJ の TMR や Vhalf などのデバイスパラメータはかなりロバストに設計できることを明らかにした(大きな TMR 比や Vhalf は不可欠ではない). また、BET によるパワーゲーティングへの適合性の検証を行い、提案した NV-SRAM が通常のマイクロプロセッサ等のパワーゲーティングに適応可能な BET を有していることを明らかにした. また、より細粒度のパワーゲーティングの実現を目指し BET の効果的な削減方法を提案し、PS-MOSFET のプロセスを変更せずに(関値制御などを行わずに)バイアスのみでも BETを大きく減少させることができる NV-SRAM の駆動方法を見出した. また、通常動作の検証ではスタティックノイズマージンの検証を行った. PS-MOSFET を用いれば、MTJ とインバータループを分離できるため、通常の 6T-SRAM と同じノイズマージンを有することを明らかにした. さらに、PS-MOSFET の付加によるスタティックリークの増大に関しては、PS-MOSFET の閾値制御を行わずに、6T-SRAM 程度にリーク電流を削減できる駆動方法を提案した. 以上の提案した方法を用いれば既存の 6T-SRAM の設計をベースとしても BET およびリーク電流を大きく削減できる NV-SRAM セルを構成することができる.

NV-FF に関しても、SPICE シミュレーションによる動作検証・回路解析・性能評価を行いその設計方法を示した。BET とリーク電流に関しては NV-FF では NV-SRAM とは異なり、バイアス変調による駆動の導入はあまり好ましくないことから、PS-MOSFET の W/L 比から BET とリーク電流を大幅に削減できる方法を示した。また、NV-FF は通常の FF としての性能も重要である。通常動作時における各種ディレイタイムなどの性能を通常の FF やその他のリテンション FF (バルーン FF) と比較を行い、通常の FF に比べて性能劣化はわずか数%であることを明らかにした。これはバルーン FF と同程度であり(より正確にはバルーン FF より軽微であった)、実用上の問題がないことを明らかにした。

また、プロセッサ内における NV-FF と NV-SRAM の効果的な使用方法を提案して、これらを用いた不揮発性パワーゲーティング・プロセッサの提案した.

#### \*最重要マイルストーン:クリア

# ③-3 PS-MOSFET, S-MOSFET を用いた高機能ロジックの試作と評価(東大・NIMS・東工大)

#### 【研究計画と実施方法】

ベンダーCMOS チップを利用して PS-MOSFET や NV-SRAM セルなどを作製し機能評価を行う.機能評価のポイントは、(i)PS-MOSFET によるストア・リストア動作の原理実証、(ii)NV-SRAM セルなどの基本動作実証である. S-MOSFET でも開発状況によっては同様に進めることが可能となるが、S-MOSFET そのものの開発が本研究課題では重要となるため、PS-MOSFET による回路機能の実証が中心になる. PS-MOSFET によるロジック回路の検討結果を将来の S-MOSFET によるロジック回路への応用に効果的にフィードバックできるように開発を進める.

#### 【研究成果】

外注 CMOS (350nm プロセス)の SPICE パラメータと NIMS グループで作製した MTJ から抽出したデバイスパラータを用いて、試作を行う NV-SRAM セルの動作検証および設計を行い、実際に CMOS チップを作製した.この基板上に MTJ を集積化して、問題点の検討を行った.最も

重要となるのは CMOS 基板表面の平坦化である. チップ表面のラフネスによってチップ上に形成した MTJ の TMR は非常に小さくなることがわかった. そこで, チップ表面の平坦化に着手した(上記②-4項目参照). この平坦化を難しくしているのは外注ベンダーの CMOS チップが所謂シャトルプロセスのため, 該当チップ領域以外の部分をレーザーアブレーションによって焼切っていることに起因する. この領域のランダムな極めて大きなラフネスのため, 再現性よく平坦化を行うことが難しい. このため, 今年から新規に開始された他チップ領域にレーザーアブレーションを行わない他のベンダーによるシャトルプロセスも同時に検討を行うこととした.

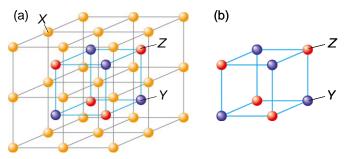

図 1(a)フルホイスラー合金 X<sub>2</sub>YZ の L2<sub>1</sub> 構造.(b)L2<sub>1</sub> 構造(図(a))に おける内側の副格子(YZ 格子). 内側の副格子にディスオーダーが 入ると B2 構造となる. また外側の副格子(X 格子)にディスオーダー が入ると A2 構造となる.

図2 CFS 薄膜のB2 規則度とL21規則度のRTA 温 度依存性. バルクと同程度の高い規則度が得られた.

Si on Z

Fe on Y

Co on X

800

図 3 左図: FeとCoの置換によるDO3不規則化. 中央図: 本研究課題で開発した方法による各種不規則化パラメータのRTA 温度依存性の評価. DO3 不規則化は一般的に用い得られる Webster モデルでは評価できない. 右図:サイト占有率の RTA 温度依存性. 各元素 90%以上のサイト占有率となる理想的な L21 構造を実現できた.

図 4 上段左図: CFS/SiO2(2.2nm)/Si トンネル接合の SIMS 測定結果. RTA により, Co, Fe がトンネルバリアを透過して Si 基板の奥深くまで拡散している. 上段中央図: CFS/SiON(2.3nm)/Si トンネル接合の SIMS 測定結果. Fe, Co の透過が大 きく抑止された. ピュアな SiN によってこの抑止効果はさらに増大すると考えられる. 上段右図:薄い SiON 上に形成した CFS の X 線回折パターン. (111), (200)規則格子線が観測され, L21 構造であることがわかる. 下段図: CFS/SiON(2.3nm)/Siト ンネル接合の断面 TEM 像. SiON にピンホールなどの欠陥は生じず, また, CFS は界面層を形成することなく SiON 上に形 成されている. 高効率のスピン注入が期待できる.

図 5 左図: As の界面偏析を利用した CFS/Si 接合をソース/ドレインとする MOSFET の出力特性. 中央図: オン電流の RTA 温度依存性. 右図: オン/オフ比の RTA 温度依存性. CFS/Si 接合においてもドーパントの界面偏析技術を利用して、バリアハイト制御ができることを示した.

図 6 左図: 熱酸化 Si 基板上の MTJ 素子の各種温度における TMR 曲線. 右図: 熱酸化 Si 基板上に作製した MTJ 素子の TMR の温度変化

図 7 CFAS を用いた MTJ の  $10~\rm K$  および室温における TMR 曲線. 低温で 785%, 室温においても 360%の非常に高い TMR 比を示している.

図8 CFAS を用いた CPP-GMR 素子のスピン注入磁化反転特性. ハーフメタル・フルホイスラー合金でスピン注入磁化反転が初めて観測された.

図 9 左図: 疑似スピン MOSFET の回路構成. 右 上図: 作製した疑似スピン MOSFET の断面模式図. SOI 基板を用いたボトムゲート型 MOSFET にフルホイスラー合金 MTJ(TMR 比70%)を集積化して作製した. 右下図: 作製した疑似スピン MOSFET の表面写真.

図 10 左図:作製した疑似スピン MOSFET の出力特性. 実線が MTJ の磁化状態が平行磁化の場合, 破線が反平行磁化の場合である. 磁化状態に応じて電流駆動野力が変調されている. 中央図:ドレイン電流の磁場依存性. 交換バイアス型の MTJ の特性を反映したヒステリシスが得られた. 右図:磁気電流比(平行磁化, 反平行磁化におけるドレイン電流の変化率)のドレインバイアス依存性. 実測値(黒線)は我々の開発した MTJ の SPICE モデルを用いたシミュレーションと良く一致し(低い Vd と高い Vg を除く), MOSFET のソースに接続した MTJ によるフィードバック効果を確認できた. シミュレーションからのズレはゲートリークによる. 最大で 45%の磁気電流比を確認できた.

図 12 本研究課題で開発を行う擬似スピン MOSFET のシミュレーション結果. MOSFET のパラメータは TSMC350nmプロセス, MTJ のパラメータは NIMS グループの MTJ から抽出した

図 13 提案した不揮発性 SRAM のセル構造. 擬似スピン MOSFET を通常の 6T-SRAM の記憶ノードに接続することによって実現できる. 擬似スピン MOSFET によって通常の SRAM 動作と不揮発動作を分離できる.

図 14 提案した不揮発性 DFF の回路図. 不揮発性 SRAM と同様に擬似スピン MOSFET によって通常の DFF 動作と不揮発動作を分離できる. このため,通常の DFF 動作をほとんど劣化させずに不揮発化の機能を持ち込める.

図15 不揮発性 SRAM のシミュレーション結果. インバー タループから PS-MOSFET の ス ト r 動 作 は , PS-MOSFET を導通後, CTRL ラインにパルス信号を 加えるだけで実現できる. PS-MOSFET からインバー タループへのリストア動作は PS-MOSFET を導通後,インバータループの電源を引き上げるだけで実現できる.

#### § 4. 成果発表等

#### (4-1) 原著論文発表

#### ●論文詳細情報

- (1) S. Yamamoto and Satoshi Sugahara, "Nonvolatile Delay Flip-Flop Based on Spin-Transistor Architecture and Its Power-Gating Applications", Jpn. J. Appl. Phys., vol. 49, no. 9, 2010, pp. 090204/1-3.

- (2) Y. Takamura, R. Nakane, and S. Sugahara, "Quantitative analysis of atomic disorders in full-Heusler Co<sub>2</sub>FeSi alloy thin films using x-ray diffraction with Co *Ka* and Cu *Ka* sources", J. Appl. Phys., vol. **107**, no. 9, pp.09B111/1-3, 2010.

- (3) K. Hayashi, Y. Takamura, R. Nakane, and S. Sugahara, "Formation of Co<sub>2</sub>FeSi/SiO<sub>x</sub>N<sub>y</sub>/Si tunnel junctions for Si-based spin transistors", J. Appl. Phys. vol. **107**, no. 9, pp. 09B1041/1-3, 2010.

- (4) Shuu'ichirou Yamamoto, Yusuke Shuto, and Satoshi Sugahara; "Nonvolatile SRAM (NV-SRAM) Using Resistive Switching Devices: Variable-Transconductance MOSFET Approach," Jpn. J. Appl. Phys., vol. 49, no. 4, 2010, pp. 040209/1-3.

- (5) H. Sukegawa, H. Xiu, T. Ohkubo, T. Furubayashi, T. Niizeki, W. H. Wang, S. Kasai, S. Mitani, K. Inomata and K. Hono, Appl. Phys. Lett. 96, 212505 (2010). "Tunnel magnetoreistance with improved bias voltage dependence in lattice-matched Fe/spinel MgAl<sub>2</sub>O<sub>4</sub>/Fe (001) junctions"

- (6) Wenhong Wang, Enke Liu, Masaya Kozuka, Hiroaki Sukegawa, Marec Wojcik, Eva Jedryka, G. H. Wu, Koichiro Inomata, Seiji Mitani and Kazuhiro Hono, "Coherent tunneling and giant tunneling magnetoresistance in Co<sub>2</sub>FeAl/MgO/CoFe magnetic tunneling junctions", Phys. Rev. B 81, 140402(R)-1-140402(R)-4 (2010)

- (7) Wenhong Wang, Hiroaki Sukegawa and Koichiro Inomata, "Temperature dependence of tunneling magnetoresistance in epitaxial magnetic tunnel junctions using a Co<sub>2</sub>FeAl Heusler alloy electrode", Phys. Rev. B **82**, 092402-1-092402-4 (2010).

- (8) Hiroaki Sukegawa, Shinya Kasai, Takao Furubayashi, Seiji Mitani, and Koichiro Inomata Appl. Phys. Lett. **96**, 042508 (2010). "Spin transfer switching in an epitaxial spin-valve nanopillar with a full-Heusler Co<sub>2</sub>FeAl<sub>0.5</sub>Si<sub>0.5</sub> alloy".

- (9) Y. Shuto, R. Nakane, W. H. Wang, H. Sukegawa, S. Yamamoto, M. Tanaka, K. Inomata, and S. Sugahara, "A New Spin-Functional Metal-Oxide-Semiconductor Field-Effect Transistor Based on Magnetic Tunnel Junction Technology: Pseudo-Spin-MOSFET", Appl. Phys. Exp., vol.3, no.1, pp. 013003/1-3, 2010.

- (10) T. Furubayashi, K. Kodama, T. M. Nakatani, H. Sukegawa, Y. K. Takahashi, K. Inomata and K. Hono, "Structure and transport properties of current-perpendicular-to-plane spin valves using Co<sub>2</sub>FeAl<sub>0.5</sub>Si<sub>0.5</sub> and Co<sub>2</sub>MnSi Heusler alloys electrodes", J. Appl. Phys. **107**, 113917-1-113917-7 (2010).

#### (4-2) 知財出願

- ① 平成22年度特許出願件数(国内 0件)

- ② CREST 研究期間累積件数(国内 3件)