「ディペンダブル VLSI システムの基盤技術」 平成21年度採択研究代表者

H22 年度 実績報告

#### 小柳 光正

東北大学 未来科学技術共同研究センター・教授

自己修復機能を有する3次元 VLSI システムの創製

## §1. 研究実施の概要

本研究プロジェクトでは、3 次元集積化技術の導入によって VLSI の高性能化とディペン ダビリティの向上を図るとともに、ディペンダブル3次元VLSIを用いた車載用の画像処理 システムの実現を目指して研究を行っている。このような積層型画像処理システムのディ ペンダビリティについて、画像処理・認識のディペンダビリティ、システムソフトウェア に関わるディペンダビリティ、システムハードウェアに関わるディペンダビリティという3 つの視点から検討を行った。プロジェクト終了までに、耐故障性・障害性に優れたジョブ 実行を実現するハードウェア・ソフトウェア協調型ディペンダブルシステムの実現を目指 す. また、抽象化モデルによるシステム・シミュレータと FPGA 実装ボードを開発して全 体システムの機能と性能を確認するとともに、ディペンダブル積層型画像処理プロセッ サ・テストチップを試作して、ハードウェア基本機能と性能の確認を行う。本年度は、ま ず、運転支援・画像処理システムのための画像処理の高性能化を目指して、位相限定相関 法に基づく超高精度ステレオビジョンのための基本アルゴリズムを開発した.このアルゴ リズムをターゲットアプリに設定し、3次元ビジョン用アーキテクチャの概念設計・詳細設 計を行った.Out of Order ベクトル ISA 処理機構,および 3 次元積層型チップマルチベク トルアーキテクチャについて検討するとともに、共有メモリを有するマルチコアプロセッ サにおいてディペンダブルかつ、エネルギ効率の高いジョブ実行環境構築のためのオンラ インモニタリング・評価によるジョブスケジューリングアルゴリズムについて検討した。 また、ヘテロジニアスマルチコアアーキテクチャのためのチェックポイント・リスタート 機構の基本設計を行った.マルチコア画像処理プロセッサのスレッドスケジューリング・ マイグレーション機能や自己診断・修復機能を制御するための SVP (Supervisor Processor) をマルチコア画像処理プロセッサに搭載して、システムのデベンダビリティを高める方法 についても検討した。

#### § 2. 研究実施体制

- (1)「東北大学 小柳」グループ

- ①研究分担グループ長:小柳光正 (東北大学未来科学技術共同研究センター、教授)(研究 代表者)

- ②研究項目

自己修復機能を有する3次元 VLSI システムの全体設計および性能評価

- ディペンダブル 3 次元積層型画像処理プロセッサのシステム性能評価

- プロトタイプ 3 次元積層型画像処理プロセッサの設計・試作

- 3次元LSIテスト回路の設計、試作および3次元LSIの信頼性評価

- ディペンダブルメモリの設計、試作、評価

#### (2)「東北大学 小林」グループ

- ①研究分担グループ長:小林広明 (東北大学サイバーサイエンスセンター、教授)(主たる共同研究者)

- ②研究項目

- ・ アプリケーションの特性を考慮した 3 次元 VLSI ハードウェアの構成技術の研究開発

- 青木グループ3次元ビジョン用アルゴリズムコードのプロファイリング,これに基づく本アルゴリズム用チップの基本アーキテクチャ設計

- ショートベクトルのための OoO ベクトル ISA 実行機構の設計

- 3 次元マルチベクトルコアプロセッサアーキテクチャ設計, 3 次元積層型キャッシュメモリ設計

- ・ ディペンダブルなアプリケーションスケジューリング機構の研究開発

- ディペンダブルプログラム実行機構のためのオンラインモニタ・評価に基づくスレッド実行制御

- ◆ ヘテロジニアスコンピューティングプラットフォームのためのチェックポイント・ リスタート機構の基本設計

#### (3)「東北大学 青木」グループ

①研究分担グループ長:青木孝文(東北大学大学院情報科学研究科、教授)(主たる共同研究者)

#### ②研究項目

● 位相限定相関法に基づく超高精度ステレオビジョンのためのアルゴリズム開発

- 上記アルゴリズムのソフトウェア実装および性能評価

- 上記アルゴリズムの GPU への実装および性能評価

- (4)「熊本大学 末吉」グループ

- ① 研究分担グループ長:末吉敏則 (熊本大学大学院自然科学研究科、教授)(主たる共同研究者)

- ②研究項目

- 不良救済技術およびメモリ・ソフトエラー検出救済技術の検討・評価

- 3次元リコンフィギャラブルロジックおよび CAD ツールの検討・評価

- (5)「デンソー 鎌田」グループ

- ① 研究分担グループ長:鎌田忠 (㈱デンソー半導体開発部、担当部長)(主たる共同研究者)

- ② 研究項目

車載用画像処理システムの概念設計と高頼化技術の検討

- 誤認識(測位誤差)の問題から見た性能目標の検討

- ディペンダビリィティの目標値を達成する方式の評価方法の検討

- (6)「ザイキューブ 元吉」グループ

- ① 研究分担グループ長:元吉真 (㈱ザイキューブ、取締役社長)(主たる共同研究者)

- ② 研究項目

自己修復機能を有する3次元LSIテスト回路の試作および評価

- メモリ・ソフトエラー検出・救済手法の確定と自己修復機能を有する3次元 LSI テスト回路設計および評価

- 3次元 LSI テスト回路、プロトタイプ 3次元積層型画像処理プロセッサ試作用 3次元 LSI 技術のプロセス条件の確定。

#### §3. 研究実施内容

(文中に番号がある場合は(4-1)に対応する)

本研究プロジェクトでは、3次元集積化技術の導入によってVLSIの高性能化とディペンダビリティの向上を図るとともに、ディペンダブル3次元VLSIを用いた車載用の画像処理システムの実現を目指す。このような車載用3次元積層型画像処理システムのディペンダビリティについて、画像処理・認識のディペンダビリティ、システムソフトウェアに関わるディペンダビリティ、システムハードウェアに関わるディペンダビリティという3つの視点から検討を行う。プロジェクト終了までに、抽象化モデルによるシステム・シミュレータとFPGA実装ボードを開発して全体システムの機能と性能を確認するとともに、ディペンダブル3次元積層型画像処理プロセッサ・テストチップを試作して、ハードウェア基本機能と性能の確認を行う。以下に、本年度の研究実施内容と成果についてまとめる。

#### 1) 画像処理システムの高性能化と全体設計に関する研究

運転支援システムとしての画像処理システムのデベンダビリティ向上を、画像処理・認識の高性能化による測距制度の向上と、ソフトウェア/ハードウェア協調による自己診断・修復機能の搭載によって実現することを目指して、システム性能、コストの点から目標仕様の詳細検討を行った。その結果として、ASIL=C(故障率〈80FIT・SPFM〉97%・LFM〉80%)の信頼性を確保しながら、上位言語(C, Open-CL など)対応も含め普及に必要なシステム性能(1Tflops)を達成することを目標として設定した。

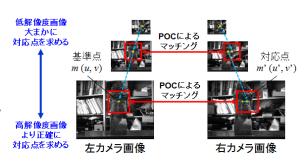

運転支援・画像処理システムのための画像処理の高性能化を目指して、位相限定相関法に基づく超高精度ステレオビジョンのための基本アルゴリズムを開発した<sup>5),6)</sup>。MATLAB などの高水準

モデリング環境を用いて,車載向けのステレオビジョンシステムで重要になるサブピクセル画像対応付けアルゴリズムを開発した 10)-12). 具体的には,位相限定相関法の高精度化手法として,窓関数の適用,スペクトル重み付け,相関ピークモデルのフィッティング,高速化手法として,位相限定相関法の 1 次元化,対応付けのロバスト化手法として,3 階層程度の階層探索を用いることを検討し,ステレオ画像の

対応点を 1/10~1/20 ピクセル程度の画像分解能で検出することを確認した. 昨年度に引き続き, 1 次元位相限定相関法に基づく対応付けアルゴリズムの開発を行い, 本アルゴリズムの応用として, 車載カメラのみならず各種のマシンビジョン応用(監視カメラ, 物体認識, FA, 生体認証など)を検討し

図 1. 位相限定相関法 (POC) に基づく超高 精度ステレオビジョンのためのアルゴリズム

表 1. ステレオ画像の対応付け 処理時間評価結果

| 基準点数                | 1,000   | 5,000   | 10,000  | 50,000    |

|---------------------|---------|---------|---------|-----------|

| CPU<br>(1コア)        | 53.7ms  | 222.9ms | 433.7ms | 1,647.0ms |

| CPU<br>(4コア, 8スレッド) | 23.1 ms | 68.5ms  | 121.6ms | 555.1 ms  |

| GPU                 | 6.7ms   | 202ms   | 32.5ms  | 139.9ms   |

- CPU: Intel Core i7 975 Extreme (3.33GHz)

- GPU: NVIDIA GeForce GTX 480 (SP: 480基)

- 画像サイズ: 1,280×960 画素

- 探索ウィンドウ: 64×9 画素

- 階層数: 4

た. また、図 1 に示すような位相限定相関法に基づく超高精度ステレオビジョンのための基本アルゴリズムおよびサブピクセル画像対応付けアルゴリズムを GPU へ実装するとともに、実際に自動車に搭載したステレオビジョンシステムで性能を評価した. 評価結果を表 1 にまとめる。

#### 2) ディペンダブルソフトウェア技術に関する研究

青木グループの開発した 3 次元ビジョン用アルゴリズムコードのプロファイリングを行い, 高効率 実行を可能とするアーキテクチャのための必要要件の抽出を行った.

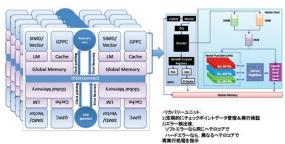

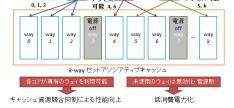

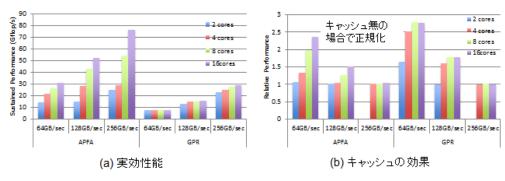

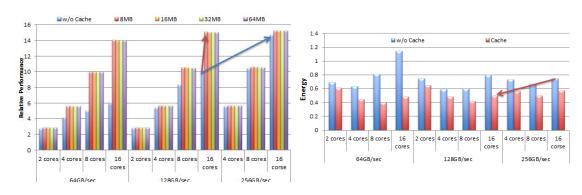

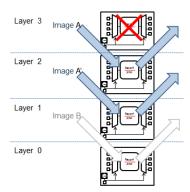

アプリケーションの特性を考慮した 3 次元 VLSI ハードウェアの構成技術の研究に関しては、マルチメディアアプリケーションを高効率に実行可能なベクトル処理機構を提案し、シミュレータと多数のベンチマークプログラムを用いた評価によりその有効性を明らかにした. 図 2 に示すような 3 次元積層型プロセッサを提案し、3 次元積層技術を用いたキャッシュメモリの基本設計、および図 3 に示す適応型キャッシュ機構の評価、更に、3 次元積層技術を用いたチップマルチベクトルプロセッ

サの基本設計を行った<sup>3)</sup>. また、3 次元積層型 チップマルチベクトルプロセッサのソフトウェア シミュレータを開発し、アーキテクチャの基本 設計に関する性能評価を行った. その結果, 図 4 に示すように、3 次元積層技術を用いてコ ア数を増加することで高い実効性能の向上を 得られること、3次元積層によりはじめて実現可 能な大規模なオンチップキャッシュを導入する

ことで、オフチップメモリアクセスを抑制し消費エネルギを大幅に削減できることを明らかにした。また、図 5 に示すように、I/O 層を強化することによりオフチップメモリバンド幅を向上させるよりも、オンチップメモリを搭載し、データアクセスの局所性を利用することで、エネルギ効率の高い処理が可能であることを明らかにした。これらの成果は、今後本研究課題で取り組む車載用 3 次元ビジョン用アーキテクチャの詳細設計において、重要な知見である。

図 2. 三次元積層構造を有するマルチコア 画像処理プロセッサの構成

# 適応型キャッシュ機構 NコアCMP core core core / 2/12 M core / 2/12 M

アクセス可能

図 3. 三次元積層化による適応キャッシュ機構の導入

図4. プロセッサ性能とメモリバンド幅

図 5. キャッシュ vs. Off-chip メモリバンド幅

ディペンダブルなアプリケーションスケジューリング機構の研究では、ディペンダブルプログラム 実行機構のためのオンラインモニタ・評価に基づくスレッド実行制御に関する研究開発を行った 15.2 本機構では、複数コアが大規模なキャッシュメモリを共有していることを想定しており、動的に複数のスレッドの性能をモニタリングし、各スレッドの性能を維持するために必要十分なキャッシュを割り当てる事が可能となるようにスレッドをコアにスケジューリングする。また、キャッシュメモリはウェイ単位で管理し、利用されていないウェイへの電源供給を遮断することで、電力効率の向上を図っている。これらの成果は、本研究課題で想定している3次元ビジョン用チップ設計において組み込むことが予定されているヘルスモニタリング情報に基づくスレッドスケジューリング・マイグレーションを実現するために必要不可欠な要素技術である。また、将来の異種複数の演算コアが混在する計算環境において、高いジョブ実行のディペンダビリティ向上を目的にヘテロジニアスな計算環境におけるチェックポイント・リスタート機構に関する研究を行った40、本研究では、ヘテロジニアスな計算環境におけるチェックポイント・リスタート機構に関する研究を行った40、本研究では、ヘテロジニアスな計算環境として、GPUと CPU が混在する環境においても、アプリケーションコードに対して透過的で安全なチェックポインティング、リスタートを実現可能な機構を開発し、実機を用いた評価によりその動作、有効性を確認した。

#### 3) ディペンダブルハードウェア技術に関する研究

画像処理・認識の高性能化と自己診断・修復機能の搭載によって運転支援用画像処理システムのデベンダビリティを向上させるためのハードウェア技術について検討した。マルチコア画像処理プロセッサのスレッドスケジューリング・マイグレーション機能や自己診断・修復機能を制御するための SVP (Supervisor Processor) をマルチコア画像処理プロセッサに搭載して、システムのデベンダビリティを高めることを検討した。SVP には高いデベンダビリティが要求されるため、自己診断・修復機能をリコンフィギュラブル回路で構成することを検討した。ハードウェア技術としては、性能、電力効率ともに1~2 桁改善できる3次元LSI技術を採用することを前提に、微細なTSV (Through-Si Via) を有する3次元集積化技術の開発を行った7。

H23 年度におけるチップ試作を目指して、SIMD 型プロセッサと汎用プロセッサ、キャッシュメモリからなるプロセッサコアを複数搭載した画像処理プロセッサチップを 2~4 層、キャッシュメモリを 2

~4 層積層する 3 次元積層型プロセッサの概念設計を行った。また、各プロセッサ層に、自己診断、修復回路を搭載する方法の検討も行った。H23 年度に予定している大規模な 3 次元積層型画像処理プロセッサ試作の前準備として、SIMD/MIMD プロセッサを搭載した小規模マルチコアプロセッサ (4 コア搭載) テストチップを設計・試作し、動作確認に成功した。図 6 に、試作したルチコアプロセッサ (4 コア搭載) テストチップのチップ写真と、4 コアを同時並列動作させて得られた画像処理の結果を示す。二値化処理、ラブラシアン・フィルター処理は SIMD 動作、エッジ抽出処理はMIMD 動作により行っている。現在、このプロ

図 6. 試作したマルチコアプロセッサ・テストチップの顕微鏡写真(a)と画像処理結果 (b)

セッサチップを 4 層積層中であり、積層工程が完了次第、チップ層間にまたがるマイグレーション機能(図7)の評価や、3次元積層化に伴う問題点の抽出を行う予定である。

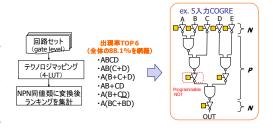

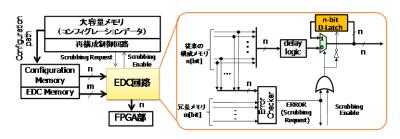

リコンフィギュラブル回路を使用するSVPのデベンダビリティの 向上を目指して、ソフトエラー救済技術を要するディペンダブル アーキテクチャの要素技術として、図 8、図 9 に示すような論理 セル COGRE (Compactly Organized Generic

Reconfigurable Element),およびエラー訂正回路を提案した. 多くのFPGAで用いられるLUT方式は入力数に応じて任意の 論理を実装可能であるが,真理値表をそのまま実現しているために多くの構成メモリが必要となり、ソフトエラーに対する脆弱

図 7. 三次元積層型プロセッサにおける障害回避 (マイグレーション)

性が問題となる. そこで LUT と同等の柔軟性を保持しつつ構成メモリ数を削減した論理セル COGRE を提案した. COGRE はプログラマブルインバータと NAND セルより構成されており,8 ビットの構成メモリをもつため,4-LUTと比較して半分の構成メモリ数で済む. MCNC 回路 20 種類に対し6入力 COGRE を用いて配置配線を行い,6-LUTと面積,構成メモリ数の比較を行った.この結果,6-LUTと比較して論理面積が46.3%削減可能であり,総構成メモリ数も32.1%削減可能であった.これより, COGRE は FPGA の小型化,省構成メモリの観点より有効であることがわかった.

構成メモリを対象として、符号化訂正回路とスクラビングを組合わせたエラー訂正回路を提案した.本回路では本来の構成メモリnビットに対しハミング符号化に必要なmビットを付与することで、1ビットまでのエラー訂正、および2ビットまでのエラー検知が可能である.一度ソフトエラーを検知すると、大容量メモリからコンフィグレーションパスを通じて正しい構

図8. 5入力COGRE

成データに書換えることでソフトエラーを自動修復する.この際,FPGAの機能実現に必要な構成データはラッチを通して供給されるため,ソフトエラーの影響は隠蔽される.事前評価より得られたm=21,

図9. エラー訂正回路のブロック

n=6にて6-LUTを対象としてFIT値を算出した結果,タイル単位でTMR化した場合と比較して構成メモリ数を約25%削減し,約22倍のFIT値が得られた.これより,提案エラー訂正回路による高信頼化が確認できた.

メモリ・ソフトエラー検出・救済を中心とした自己修復機能を有する3次元 LSI テスト回路の設計するとともに、3次元LSIテスト回路の試作に必要な3次元LSI技術のプロセス最適条件の検討を行った。また、ソフトエラー耐性を評価するための評価システムを構築した。

## §4. 成果発表等

#### (4-1) 原著論文発表

- ●論文詳細情報

- 1) Masayuki Sato, Ryusuke Egawa, Hiroyuki Takizawa, Hiroaki Kobayashi, "A Majority-based Control Scheme for Way-Adaptable Caches," Proceedings of Conference for Young Scientists Facing the Multicore-Challenge, pp.19-31, 2010 [DOI: 無し]

- 2) Masayuki Sato, Ryusuke Egawa, Hiroyuki Takizawa, and Hiroaki Kobayashi, "A Voting-Based Working Set Assessment Scheme for Dynamic Cache Resizing Mechanisms," Proceedings of IEEE International Conference on Computer Design 2010, pp.98-105, 2010. [DOI: 10.1109/ICCD.2010.5647599]

- 3) Ryusuke Egawa, Yusuke Funaya, Ryu-ichi Nagaoka, Akihiro Musa, Hiroyuki Takizawa and Hiroaki Kobayashi, "Design and Early Evaluation of a 3-D Die Stacked Chip Multi-Vector Processor," Proceedings of IEEE International 3D System

Integration Conference, pp. 1-8, 2010. [DOI:付与予定]

- 4) Katsuto Sato, Hiroyuki Takizawa, Kazuhiko Komatsu, and Hiroaki Kobayashi, "Automatic Tuning of CUDA," Software Automatic Tuning: From Concepts to State-of-the-Art Results, Springer, pp.209--228, ISBN 978-1-441-96934-7, 2010. [DOI: 無し]

- 5) Ayako Suzuki, Koichi Ito, Takafumi Aoki and Ruriko Tsuneta, "A scale estimation algorithm using phase-based correspondence matching for electron microscope images," Proceedings of the 20th International Conference on Pattern Recognition, pp. 2420-2423, August 2010. [DOI 10.1109/ICPR.2010.592]

- 6) Toru Takahashi, Tatsuya Kawano, Koichi Ito, Takafumi Aoki and Satoshi Kondo, "Performance evaluation of a geometric correction method for multi-projector display using SIFT and phase-only correlation," Proceedings of 2010 International Conference on Image Processing, pp. 1189--1192, September 2010.

[DOI: 10.1109/ICIP.2010.5651839]

- 7) Kang-Wook Lee, Akihiro Noriki, Kouji Kiyoyama, Takafumi Fukushima, Tetsu Tanaka, and Mitsumasa Koyanagi, "Three-Dimensional Hybrid Integration Technology of CMOS, MEMS, and Photonics Circuits for Optoelectronic Heterogeneous Integrated Systems," IEEE Trans. on Electron Devices, Vol.58, No3, March. 2011 [DOI: 10.1109/TED.2010.2099870]

- 8) Hiroyuki Takizawa, Kentaro Koyama, Katsuto Sato, Kazuhiko Komatsu, and Hiroaki Kobayashi, "CheCL: Transparent Checkpointing and Process Migration of OpenCL Applications," in Proceedings of the 25th IEEE International Parallel and Distributed Processing Symposium (IPDPS2011), 2011 (採録決定済み)

- 9) Hiroyuki Takizawa, Kentaro Koyama, Katsuto Sato, Kazuhiko Komatsu, and Hiroaki Kobayashi, "CheCL: Transparent Checkpointing and Process Migration of OpenCL Applications," in Proceedings of the 25th IEEE International Parallel and Distributed Processing Symposium (IPDPS2011), 2011 (採録決定済み)

- 10) Toru Takahashi, Takafumi Aoki, Koichi Ito and Satoshi Kondo, "A correspondence search technique for geometric correction of projected images," 映像情報メディア学会論文誌(条件付採録決定). [DOI: 無し]

- 11) 高橋徹, 川野達也, 伊藤康一, 青木孝文, 近藤敏志, "SIFT と位相限定相関法を用いた高精度画像対応付けに基づくマルチプロジェクタディスプレイの校正手法," 電子情報通信学会論文誌 A, Vol. J94-A, No. 2, February 2011(採録決定). [DOI: 無し]

- 12) 高橋徹, 三浦衛, 伊藤康一, 青木孝文, "位相限定相関法に基づく高精度ステレオビジョンを用いた投影画像の幾何補正," 電子情報通信学会論文誌 D, Vol. J94-D, No. 8, August 2011 (条件付採録決定). [DOI: 無し]

## (4-2)知財出願

- ① 平成22年度特許出願件数(国内 2件)

- ② CREST 研究期間累積件数(国内 2件)