情報システムの超低消費電力化を目指した技術革新と統合化技術 平成 18 年度採択研究代表者 H22 年度 実績報告

## 後藤 敏

早稲田大学大学院情報生産システム研究科・教授

超低消費電力メディア処理 SoC の研究

## §1. 研究実施の概要

消費電力メディア処理 SoC の実現のため、画像、暗号、誤り訂正符号の各方式の最適な分担 およびアルゴリズム最適化手法、さらにはハードウェア・ソフトウェア実装最適化手法を融合させ、 従来技術と比較して 1/100 の電力削減を図ることで研究を進めた。本年度は、(1)方式・アルゴリズ ムレベルでは、画像の動きを予測し、必要な演算量に応じてコアの周波数を動的に変化させること により、監視系システムや TV 会議システムの応用において消費電力を平均 46%、最大 78%削減 することができた。また、TV会議ではRoI(Region of Interest)方式を拡張し、RoI(額)の領域を精 度よく検出することでエンコーダの演算量を平均で 76%削減した。 更に、画像センサー向け移動 物体追跡に関して、KLT Tracker の並列処理アルゴリズムを IMAP CAR 上に実装した。その結 果 640×240 の画像を 30fps で処理でき、PC 比で大幅な電力性能向上を確認した。(2)チップ試 作では、動画像デコーダに関して、4096x2160 対応の H.264 復号 LSI を開発し、従来比で約 60%の電力削減を確認した。(3)ハードウェア指向設計では乗算器や除算器を含むデータパスの 電力の最適化手法、クロック信号を含めて使用されていない回路部分の電力をゲーティングする 方式の最適化と微細プロセスにおける評価、高位レベルでの電力化最適化のためのスケジューリ ング、シェアリング手法の詳細化、電源電圧最適化による低消費電力フロアプラン、ネットワークオ ンチップ(NoC)の低電力化、プロセッサコアの低電力化により、全体として 50%の電力削減ができ る目途をつけた。(4)ソフトウェア設計指向ではマルチメディア用途向けプロセッサを開発、その上 に搭載されるソフトウェアによって低消費電力化を図ることを目指している。とりわけ高速な H.264/AVC エンコーダの画面内予測手法を提案、VLIW 型プロセッサ上で並列処理実現手法を 実現することで消費エネルギーを最大 75% (平均 62.88%) 削減することに成功した。(5)ルネサ スグループ(旧 NEC グループ)では、早稲田大学グループで開発された人抽出のための低演算量 画像認識アルゴリズムを STP 搭載組込プラットフォーム XBridge へ実装し、XBridge 評価ボードによる電力評価を実施した。デスクトップ PC(Core2Duo@3GHz)上にも同じアルゴリズムをソフトウェアとして実装し電力評価を実施した。双方のプラットフォームで画像 1 枚の人抽出処理に要する消費エネルギーを比較した。プラットフォーム全体の消費エネルギーで比較した場合には XBridge は 97.6%削減、またプロセッサ部分だけの消費エネルギーで比較した場合には 96.5%の削減を達成した。

# §2. 研究実施体制

- (1)早稲田大学グループ

- ①研究分担グループ長:後藤敏(早稲田大学大学院情報生産システム研究科、教授)

- ②研究項目:超低消費電力メディア処理SoCの研究

- (2) ルネサスグループ

- ①研究分担グループ長:粟島亨(ルネサスエレクトロニクス株式会社、チームマネージャー)

- ②研究項目:プログラマブルハードウェアを用いた低電力メデイア処理の研究

#### §3. 研究実施内容

(文中に番号がある場合は(4-1)に対応する)

超低消費電力メディア処理 SoC の実現のため、本プロジェクトではメディア処理低消費電力方式とアルゴリズムおよび SoC 設計技術、ハードウェア指向設計技術、ソフトウェア指向設計技術の3つのサブテーマに基づき取り組みを進めてきた。更に昨年度からは社会還元促進プログラムとして新たに追加されたプログラマブルハードウェアを用いた低電力メディア処理の研究を開始し、来年度で終了予定である。

## 「方式・アルゴリズム・SoC 設計技術」

#### ●超低消費電力メディア処理の方式の開発

監視システムや TV 会議という特定な使用場面を想定して、画像符号化の演算量を大幅に削減し消費電力を削減する実験システムを開発し評価を行った。監視システムではカメラは固定した位置にあり、また動きもフレーム間では激しく変化しないことに注目し、昨年度に考案した動き差分検知方式をもとに、今年度は、画像の動きを予測し、必要な演算量に応じてコアの周波数(電源電圧)を動的に変化させる機能を、4コアの組込みマルチプロセッサーに実装し、リアルタイムに消費電力を測定した。本方式を使わない方式に比べて、平均で 46%の電力削減、最良値では 78%の電力削減が行えた 26,440。また TV 会議では人が注目する部分には高精細な画像を、注目しない部分には画質を落とすというRoI (Region of Interest)方式を開発してきたが、本年度は人が複数人でも対応可能なシステムへ拡張し、RoI (顔)の領域を精度よく検出するアルゴリズムを考案し、平均で 76%のエンコーダの演算量を削減した 8,190。

### ●画像センサー向け移動物体追跡処理システムの構築

自動監視などを可能にする高度な画像センサー実現には、高精度な実時間画像認識機能が不可欠となっているが、人物追跡などの画像認識処理は、1TOPS以上の演算量を占め、HDTVクラスのビデオエンコーダと同等以上であり、画像センサーの中で 50%以上の大きな割合を占めている。そこで、画像処理の重要の一つである移動物体アルゴリズムとして KLT Tracker (CMU の金出教授により提案)を選択し、低消費電力化の検討を行った。KLT Tracker は、画像中から特徴点を抽出し、それらに対し勾配法に基づく追跡処理を行う事により、極めてロバストな動きベクトルの抽出を可能にしており、様々な画像認識応用に用いられている。ただ、極めて大きな演算量を必要とし、汎用PCを用いた実装では、多くの消費電力を必要とし、かつ実時間処理の実現は不可能である。本検討では、KLT Tracker の並列処理アルゴリズム構成法、メモリ構成法などを考案し、並列処理専用画像エンジンである IMAP CAR 上に実装した。その結果、640×240 の画像を 30fpsで処理できる事を確認した。一方、KLT Tracker を Open CV を用いて PC 上に実装したところ、320×240 の画像に対し、処理時間は 7~8fpsとなった。IMAP の消費電力は 2W 以下であり、P Cの消費電力が 50W 程度必要であることを勘案すると、大幅な電力性能向上が図れていることが確認できる。また、低消費電力化の成果を可視化するものとして、実時間画像処理デモシステムを

#### 構築した。

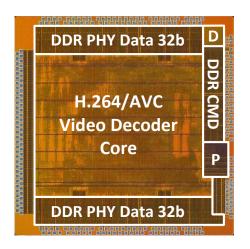

#### ●超低消費電力メディア SoC の試作

動画像デコーダに関しては、4096x2160 対応の H.264 復号 LSI を開発し、従来比で約 60% の電力削減を行うことができた。開発したビデオ復号 LSI の特徴は(1)H.264/AVC ハイプロファイル標準仕様に基づくデコーダで、4096x2160 画素の動画を 60 枚/秒処理できること。(2)処理するマクロブロック順序の最適化、フレームのロスレス圧縮方式、並列処理による高速化等の新技術を開発することで、外部 DRAMとデコーダエンジン間の転送量を従来と比べて38%削減したこと。(3)復号チップの電力消費を 4096x2160@60fps で 189mW を達成し(SMIC 0.90nm ルール)、従来の復号チップに比べて、55%~64%の消費電力削減、DRAMも60%の消費電力削減を図った(設計ルールが異なるためスケーリングを行った結果) 5,64)。

SMIC 90nm/1.0V CMOS

$4.0 \text{mm} \times 4.0 \text{mm} \ (= 16.0 \text{ mm} 2)$

消費電力:189mw@175MHz

Core:134mw

DRAM(64b DDR): 1.11mj/Mpixel

Logic Gates: 662K gates

SRAM: 59.6KB

図 1 4096x2160 対応の H.264 復号 LSI

## 「ハードウェア指向設計」

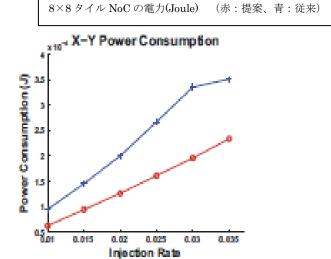

ハードウェア指向設計の研究では、アルゴリズムレベルで最適化されたC/C++ のプログラムに対し、それをハードウェアとして実現する上での電力最適化アルゴリズムの研究を行う。今年度は、昨年度の成果を発展させ、乗算器や除算器を含むデータパスの電力の最適化手法の研究、クロック信号を含めて使用されていない回路部分の電力をゲーティングする方式の最適化と微細プロセスにおける評価、フロアプランの NoC への応用、高位レベルでの電力最適化のためのスケジューリング、シェアリング手法の詳細化、電源電圧最適化による消費電力削減を行うフロアプラン手法の研究を行なった。高位データパスの最適化で電力を 3/4 程度に、電力ゲーティングで 3/5 程度に、また高位合成とフロアプランの統合で 2/3 程度にそれぞれ削減することにより、全体として1/3~1/2 とすることを目指す。 フロアプランについては、ネットワークオンチップ (NoC)の低電力化を目的とし、不規則構造を持つ Application・Specic・NoC の設計最適化に適用した。具体的には、フロアプラント、クラスタリングアルゴリズムを組み合わせ、スイッチとネットワークインタフェースの配置手法を開発することで、従来比で平均約30%の電力削減を達成したり。次に、3次元フロアプラン手法を元に、NoC を3次元 SoC として設計する手法を開発し、評価を行った。その結果、2次元と比べ、消費電力を更に約30%削減できるという結果を得た。また、高位合成スケジューリン

グにおいて、各タイムスロット毎に電源電圧を調整できる場合のレイテンシと電力の最適なトレード オフの評価を行い、レイテンシを 50%~60%を増加させることで、電力が 50%~60%削減できると いう結果を得た 23,29)。さらに多電源用フロアプランの検討を進め、電圧レベルシフターの位置の最 適化により電力を 10%以上削減できる見通しを得た。 高位合成におけるデータパスの最適化につ いては、乗算のように複数の二進数の加算を行うマルチオペランド加算に対し、7入力3出力まで の一般化並列加算器を用いた電力最適化に取り組み、段数削減のヒューリスティックを提案すると 同時に高速キャリーなどデバイス独自の機構をもちいることで、電力と遅延の積で従来手法に比べ 最大で 20 % 以上電力削減できるという結果を得た。回路の一部を動的にパワーオフするパワー ゲーティングに関しては、論理ゲートの制御値を用いて細かい単位でパワーオフを行う手法につい て、電力制御トランジスタのサイジングおよび通常の論理ゲートを用いて実現する擬似パワーゲー ティング法 34)を提案し小規模回路で評価を行った。内部のグリッチが遅延および電力消費に影響 することを示し、グリッチが発生しない場合にのみ電力ゲーティングを適用することで、遅延を一定 に保ったまま電力を20%程度削減できることを示した。また、クロックを自動的に停止する機構(クロ ックゲーティング)については、クロックの制御信号候補の抽出と、共有を考慮したクロック制御信号 の最適選択手法 22)を拡張し、クロックゲーティングを複数段で行うマルチステージの最適化を行い、 カウンタを含むベンチマーク回路で評価し、クロックゲーティングしない場合に比較して 20%、シン グルステージに比較して5%の電力削減を行った。

新アーキテクチャとその実装方式による低電力化では(1)高性能・低電力ネットワークオンチップ (NoC)アーキテクチャ および (2)低電力志向のプロセッサアーキテクチャと FPGA 構成の研究を行った。

(1)では NoC のルーティング・アルゴリズム改良によるハードウェア構成で、伝送するパケットのヘッダサイズ削減が可能となり、レイテンシとスループットの向上と同時に、NoC の低消費電力化が達成できた。NoC サイズとインジェクションレートにもよるが、8×8タイル NoC の場合、従来に比べて電力 40%程度の削減を達成した。次に、NoC の具体的応用として、パターン認識や制御などの問題に適用できるニューラルネットワーク(NN)を実装した。シミュレーションによる評価結果では、従来の P2P データ転送方式および従来ルーティングの NoC 方式に比べて、通信負荷がそれぞれ 54%~66%および 12%~13%削減でき、性能(CPS 値: Communication per Second)はそれぞれ 96%および 26%向上した。さらに、NNに必要なニューロン数やレイヤ数が非常に大きくなると NoC サイズの点で実装が困難になるという問題を解決するために、新たに「多重 NoC モデル」とよぶ構成を提案し、大規模 NN への対応を可能にした。例として、1レイヤに最大 64ニューロン、総ニューロン数およびレイヤ数は無制限 の NN を実装できる4×4PE 配列の NoC を構成した。シミュレーションの評価結果では、従来の P2P データ転送方式の NN に比べて、通信負荷が 30%~58%削減でき、システム性能(CPS 値)で 25%~47%向上した。以上の結果より、低消費電力志向の NoC アーキテクチャが示され、具合的な応用として超大規模・高性能 NN のハードウェア化が実現できた 3.70。

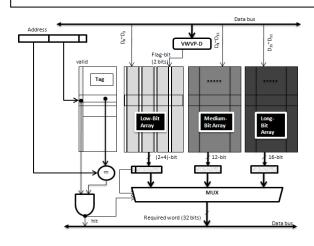

(2)では、キャッシュサイズ可変のキャッシュ機構 AWDC (Adaptive Width Data Cache)を提案し、設計・評価した。AWDC では、処理するデータサイズに応じてキャッシュの使用部分のみに電力を供給し、不使用部分には電力供給を停止できる。ベンチマークデータによるシミュレーションの結果、従来型のキャッシュに比べて、ダイナミック電力で 44.75%、スタティック電力で 42.86%の削減効果を得た 50%。次に、ディジタルシステムの実装デバイスである FPGA の低消費電力化の構成方式を提案した。FPGA 上の論理実装単位であるクラスタロジックブロック (CLB)ごとにパワー制御ハードマクロ(PCHM)を用意し、この PCHMを通して、実際に論理実装された CLB にのみ電力を供給し、不使用 CLB の電力供給は停止することができる。PCHM のために若干の回路面積のオーバヘッドがあるが、不使用部分の電力を停止できるので、電力削減効果が大きく、モバイル機器への FPGA 利用の拡大が期待できる。この新しい FPGA アーキテクチャを利用するための設計ツールも同時に開発し、評価を開始した 51%。

図2 新アーキテクチャによる電力削減-NoCの電力削減効果

可変データキャッシュの構成 (1ライン 32bit を Lower, ,Mid, Higher の 3 領域 に分割、データサイズに合わせて不使用部分の電力供給停止)

図3 新アーキテクチャによる電力削減-低電力キャッシュの構成-

これらの成果により、ハードウェア指向設計全体として、消費電力を 1/2~2/3 に削減することを可能とした。

#### 「ソフトウェア指向設計」

ソフトウェア指向設計の研究では、メディア処理向けプロセッサを開発しその上に搭載されるソフ トウェアに着目し超低消費電力化を目指す。メディア処理用のソフトウェアに特化した命令シーケン スならびに、これに対応したプロセッサアーキテクチャを構築する。 同時に、これを実現するアルゴ リズムを考案・実装する。 今年度は、暗号処理や画像処理などのアプリケーションに着目し、特に 画像圧縮処理(H.264/AVC エンコーダ)ソフトウェアを対象として、画面内予測における低消費 電力化手法およびこれを VLIW 型プロセッサ上で並列処理実現するための手法に関して研究を 行った 12.35.36<sup>)</sup>。H.264/AVC 画面内予測では、画像ブロック単位に多数の予測モードの中から最 適なモードを選択して予測符号化される。最適な予測モードは画像ブロックの性質によってそれぞ れ異なるが、その性質に基づき適切な予測モードを選択する必要がある。このための演算量、ひ いてはその消費エネルギーが膨大となる。また既存の画面内予測技術は画質の劣化やハードウェ ア構成の複雑化などの欠点もあった。そこで我々は、H.264/AVC 画面内予測アルゴリズムの演算 量を削減、並列処理可能な低消費電力化アーキテクチャを提案した。また、メモリアクセス回数の 削減のため、新たなSIMD型VLIW命令を提案した。これらにより、H.264/AVCの画面内予測処 理を対象とした場合に、既存の VLIW プロセッサを用いた場合に比較して、消費エネルギーを最 大 75% (平均 62.88%) 削減することを達成した。 既存手法と比べ、本研究は画質の劣化を抑えて、 演算量を削減でき低消費電力処理が可能であることが言えたことになる。また、VLIW 型プロセッ サの命令メモリアクセスエネルギーについて、新たなスクラッチパッドメモリアーキテクチャとコード 配置最適化手法も提案した。提案するスクラッチパッドメモリアーキテクチャは、プログラムカウンタ によりスクラッチパッドメモリへ配置するデータを判別する。コード配置最適化手法は、アプリケーシ ョン CFG から消費エネルギー最小となるコード配置とスクラッチパッドメモリのサイズを決定する。 これにより命令メモリのアクセス数を削減し、消費エネルギーを削減することができる。 計算機実験 により、メモリを含むプロセッサ全体で平均 60.5%占めていた命令メモリの消費エネルギーを 21.0% まで削減できた。現在、次世代 HEVC (High Efficiency Video Coding) に向け提案手法 の改良を進め、さらなる画像処理向けプロセッサ全体の低消費電力化の検討に着手している。

## 「プログラマブルハードウェアを用いた低電力メディア処理の研究」

多様なアルゴリズムが存在する画像認識アルゴリズムを、その多様性・柔軟性を満たしながら、 プログラマブルハードウェアを用いて低電力化することを目指す。画像認識アルゴリズムを STP エンジン上で実現し、低電力性を実証するために以下の3項目に関する研究開発を行った。

## (1)コアアルゴリズムの STP エンジンへの実装

早稲田大学グループが開発した人抽出のための低演算量画像認識アルゴリズムをベースに入 力画像全体を処理するためのアルゴリズムを開発した。昨年度開発したアルゴリズムは1つの検出 窓(識別用の固定サイズの小画像)を対象にしたものであった。全体処理では入力画像からの検 出窓の切り出し等の処理が必要である。各検出窓には重なりがある。この重なり部分は冗長な計算となるため、冗長な計算を削減するようアルゴリズム全体を見直し、コアアルゴリズムの処理全体を4つに分割(Gradient、StatusTable、Hist、SVM)した。また、入力画像のグレースケール変換(GrayScale)、複数サイズの検出窓に対応するための画像の縮小(DownScale)、及び、複数の縮小画像からの検出結果を1つの結果として統合するためのクラスタリングアルゴリズム(MeanShift)の3つの部分処理を加えた7つのタスクを開発した。

7つのタスクのうち MeanShift を除く6タスクは CPU 向けと STP エンジン向けに最適化を行った。MeanShift に関しては、計算量が小さく STP エンジンとの並列処理を前提とすると XBridge に搭載している CPU(MIPS 4KEc)で実行しても十分な性能が達成可能なので CPU タスクとして実行することとした。デスクトップPCとのベンチマークのため7つのタスクは CPU タスクとしても実行できるように開発した。CPU タスクと STP タスクではそれぞれ固有の最適化を行った。

## (2) STP エンジンと CPU との連携によるアプリケーション全体の実行制御方式の開発

人抽出のための画像認識アルゴリズムの7つのタスクを XBridge で実行するための実行制御方式を開発した。XBridge にはプログラマブルハードウェア STP エンジンと CPU(MIPS 4KEc)という 2 つのプロセッサが搭載されている。また STP エンジンには独立にタスクを実行可能なタイルブロック(TB)が 2 つ存在する。 CPU、STP エンジンの複数タイルによるタスクの並列処理方式を開発した。7 つのタスクの処理時間を分析したところ、最初の GrayScale タスクと最後の MeanShift タスクは STP エンジンとのパイプライン的な並列処理を前提とすると CPU タスクでも十分な処理性能である。 残りの 5 つのタスク(DownScale、Gradient、StatusTable、Hist、SVM)は計算量が多く CPU 処理では十分な性能が達成できない。また、この5つのタスクは1つの入力画像の処理において複数回(画像のサイズに依存するが最大 27 回)実行される。 従って、STP エンジンの 2 つのタイルブロックによる並列処理により効率的な実行が可能である。 以上の検討結果に基づき、タスクスケジューラへのタスクの投入方式を開発した。 複数画像を連続処理する場合、CPU での GrayScale タスクと、MeanShift タスクに要する処理時間は STP エンジンでの他の 5 つのタスクの処理時間に完全に隠蔽され見えなくなる。

タスクスケジューラの機能強化として、STP エンジンクロック制御方式、同一種類のタスクのCPU 実行、STPエンジン実行の動的な選択機能を開発し、タスクスケジューラの API として実装した。

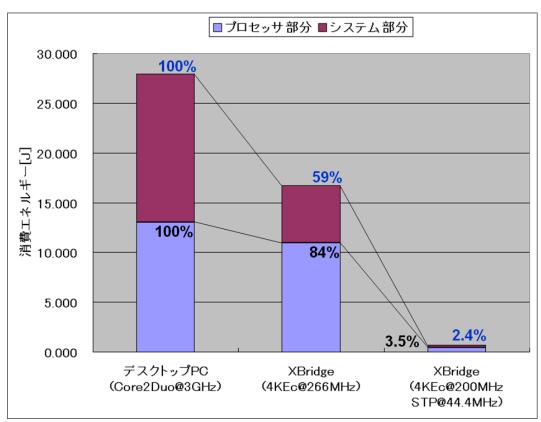

#### (3)STP エンジン評価環境による実機評価

上記(1)、(2)で開発した7つのタスク、及びアプリケーション全体の実行制御方式をXBridge、及びデスクトップ PC に実装し、処理時間、及び消費電力の計測を行った。消費電力はプロセッサ部分だけの比較ではなくシステム部分(メモリ、メモリコントローラ等)を含んだプラットフォームとしての比較も行った。XBridge側は、プロセッサ部分としてSTP エンジンと CPU(MIPS 4KEc)、システム部分としてメモリコントローラ(XBridgeに搭載)とメモリの消費電力を測定した。デスクトップPC側はプロセッサ部分として Intel Core2Duo@3GHz(6MB キャッシュ、TDP 65W)、システム部分

としてチップセットとメモリを含むマザーボードの消費電力を計測した。両プラットフォームはそれぞれの部分を含む独立した電源系統があるので、電源系統毎に消費電力を測定した。デスクトップP Cの GPU は消費電力が大きく直接の計算には関わらない部分なので、電源を分離して計測対象から除外した。

VGA サイズの 1 枚の入力画像の認識処理あたりの消費エネルギーを計測した。組み込みプラットフォームとの比較として XBridge の CPU のみで全タスクを処理した場合の消費エネルギーも計測した。この場合は停止状態の STP エンジンの消費電流は含めていない。

計測にはロジアナ機能を持つ電流計測器を用いた。計測対象となる区間を他の区間と区別するために、XBridge は GPIO ポート、デスクトップPCはパラレルポートから処理に同期して信号をアサートする。この信号をトリガとして、計測対象区間の電流を計測、積分することで、処理区間の消費エネルギーを厳密に算出した。

XBridge の CPU(MIPS 4KEc)の動作周波数は 266MHz、200MHz に設定可能である。両方の設定で計測を行い消費エネルギーの小さい方の値を採用した。結果は下表、下図の通り。 プラットフォーム全体の消費エネルギーで比較した場合には、XBridge はデスクトップ PC と比べて 97.6%削減、プロセッサ部分だけの消費エネルギーで比較した場合には 96.5%削減を達成した。また、

組込み込みプロセッサと比較した場合でも、XBridge はプラットフォーム全体で 96.0%削減、プロセッサ部分だけの消費エネルギーで比較した場合には 95.7%削減を達成した。結局、STPを使用することで、消費エネルギーを 1/42~1/23 に削減することを達成した。

以上により本プロジェクトの目標であった 10 倍以上の電力性能を達成した。

| プラットフォーム          |             |     | デスクトップ<br>PC      | XBridge              |                            |

|-------------------|-------------|-----|-------------------|----------------------|----------------------------|

| プロセッサ構成           |             |     | Core2Duo<br>@3GHz | MIPS 4KEc<br>@266MHz | 4KEc@200MHz<br>STP@44.4MHz |

| 処理時間[秒]           |             |     | 0.582             | 17.311               | 0.494                      |

| 絶対性能比率(対デスクトップPC) |             |     | 1.000             | 0.034                | 1.179                      |

| 消費エネルギー<br>[J]    | プロセッサ<br>部分 | CPU | 13.036            | 10.968               | 0.251                      |

|                   |             | STP | _                 | _                    | 0.208                      |

|                   |             | 小計  | 13.036            | 10.968               | 0.460                      |

|                   | システム部分      |     | 14.925            | 5.746                | 0.203                      |

|                   | プラットフォーム全体  |     | 27.961            | 16.714               | 0.663                      |

| 電力性能比率            | プロセッサ部分     |     | 1.000             | 1.189                | 28.360                     |

| (対デスクトップPC)       | プラットフォーム全体  |     | 1.000             | 1.673                | 42.195                     |

表 1 処理性能と消費エネルギーの比較

図4 消費エネルギーの比較

## §4. 成果発表等

### (4-1) 原著論文発表

#### ●論文詳細情報

- 1. Xin Jin and Satoshi Goto, "Encoder Adaptable Difference Detection for Low Power Video Compression in Surveillance System", Signal Processing: Image Communications. (In Press). (DOI: 10.1016/j.image.2011.01.002)

- 2. Xin Jin, Satoshi Goto, King Ngi Ngan, "Composite Model Based DC Dithering for Suppressing Contour Artifacts in Decompressed Video", IEEE Trans. Image Process., Vol.20, No.8, August 2011(In Press). (DOI:10.1109/TIP.2011.2114356)

- 3. Y.P. Dong, C. Li, Z. Lin, H. Zhang, and T. Watanabe:"High Performance Feedforward Neural Network Mapped by NoC architecture with a new Routing Strategy Implementation Method," J. Signal Processing, pp. 453-462, vol.15, no.3, May 2011.【本文引用】

- 4. Y-P.Dong, C.Li, H. Liu and T. Watanabe: "A High Performance Digital Neural Processor Design by Network on Chip Architecture," Proc.VLSI-DAT'11, Apr. 2011.

- 5. Dajiang Zhou, Jinjia Zhou, Xun He, Ji Kong, Jiayi Zhu, Peilin Liu and Satoshi Goto, "A 530Mpixels/s 4096x2160@60fps H.264/AVC high profile video decoder chip", IEEE- JSSC, Vol.46, No.4, pp.777-788, Apr. 2011.(DOI:10.1109/JSSC.2011.2109550) 【本文引用】

- 6. Gang He, Dajiang Zhou, Jinjia Zhou and Satoshi Goto, "A 530Mpixels/s Intra Prediction Architecture for Ultra High Definition H.264/AVC Encoder", IEICE Trans. on Electronics, Vol.E94-C No.4, pp.419-427, Apr. 2011.(DOI:10.1587/transele.E94.C.419)

- 7. Jinjia Zhou, Dajiang Zhou, Gang He and Satoshi Goto, "Cache Based Motion Compensation Architecture for Quad-HD H.264/AVC Video Decoder", IEICE Trans. on Electronics Vol.E94-C No.4, pp.439-447, Apr. 2011. (DOI:10.1587/transele.E94.C.439)

- 8. Tianruo Zhang, Minghui Wang, Chen Liu, and Satoshi Goto, "Multiple region-of-interest based H.264 encoder with a detection architecture in macroblock level pipelining, IEICE Trans. on Transaction on Electronics, vol. E94-C, no. 4, pp. 401-410, Apr. 2011. (DOI: 10.1587/transele.E94.C.401)【本文引用】

- 9. W. Zhong, B. Yu, S. Chen, T. Yoshimura, S. Dong, and S. Goto, "Application-Specfic Network-on-Chip Synthesis: Cluster Generation and Network Component Insertion", in IEEE Proc. International Symposium on Quality Electronic Design (ISQED), March 2011.【本文引用】

- N. Liu, S. Chen, T. Yoshimura, "Floorplanning for high utilization of heterogeneous FPGAs", in IEEE Proc. International Symposium on Quality Electronic Design (ISQED), March 2011.

- 11. Y. Tsukamoto, M. Yanagisawa, T. Ohtsuki, and Nozomu Togawa, " A Fast Selector-Based Subtract-Multiplication Unit and Its Application to Butterfly Unit," IPSJ Trans. System LSI Design Methodology, vol. 4, February Issue, pp.60-69, Feb. 2011. (DOI:10.2197/ipsjtsldm.4.60)

- 12. R. Nara, M. Yanagisawa, T. Ohtsuki, and N. Togawa, "Scan Vulnerability in Elliptic Curve Cryptosystems," IPSJ Trans. System LSI Design Methodology, vol. 4, February Issue, pp.47-59, Feb. 2011.(DOI:10.2197/ipsjtsldm.4.47)【本文引用】

- 13. Xiao Peng, Xiongxin Zhao, Zhixiang Chen, Fumiaki Maehara, Satoshi Goto, "Generic Permutation Network for QC-LDPC Decoder", IEICE Trans. Vol.E93-A, No.12, Dec. 2010. (DOI: 10.1587/transfun.E93.A.2551)

- 14. Minghui Wang, Xin Jin, Satoshi Goto, "Difference detection based early mode termination for depth map coding in MVC", PCS2010, Dec. 7th, 2010.(DOI:10.1109/PCS.2010.5702547)

- Gang He, Dajiang Zhou, Jinjia Zhou and Satoshi Goto, "Intra Prediction Architecture for H.264/AVC QFHD Encoder", PCS 2010, Dec. 7th, 2010. (DOI:10.1109/PCS.2010.5702533)

- 16. Kun Ba, Xin Jin and Satoshi Goto, "A dynamic slice-resize algorithm for fast H.264/AVC parallel decoder," The 18th International Symposium on Intelligent Signal Processing and Communications Systems (ISPACS2010), Cheng Du, China, Dec. 06-08, 2010. (DOI:10.1109/ISPACS.2010.5704638)

- 17. Wenxin Yu, Xin Jin, Satoshi Goto, "Adaptive solution of temporal scalable decoding process with frame rate conversion method for surveillance video", ISPACS2010, Chengdu, China, Dec. 6th 2010. (DOI: 10.1109/ISPACS.2010.5704682)

- Chen Liu, Xin Jin, Tianruo Zhang, Minghui Wang and Satoshi Goto, "Partial Decoding Schema for H.264/AVC Decoder", ISPACS2010, Chengdu, China, Dec. 6th.(DOI:2010.10.1109/ISPACS.2010.5704685)

- 19. Tianruo Zhang, Minghui Wang, Chen Liu, and Satoshi Goto, "Complexity Reduction Algorithm for Region-of-Interest based H.264 Encoding", APCCAS 2010, Malaysia, Dec. 6, 2010.【本文引用】

- Axel Beaugendre, Hiroyoshi Miyano, Eiki Ishidera and Satoshi Goto, "Human Tracking System for Automatic Video Surveillance with Particle Filters", APCCAS Malaysia, Dec. 6, 2010.

- 21. Ning Jiang, Yijun Lu, Shaopeng Tang and Satoshi Goto, "Rapid Face Detection

- using A Multi-mode Cascade and Separate Haar Feature", ISPACS 2010, Dec 6th, 2010.(DOI:10.1109/ISPACS.2010.5704623)

- 22. Xin Man, Takashi Horiyama and Shinji Kimura, "Power Optimization of Sequential Circuits Using Switching Activity Based Clock Gating," IEICE Trans. on Fundamentals, Vol.E93-A, No.12, pp.2472-2480, Dec. 2010.(DOI:10.1578/transfun.E93.A.2472) 【本文引用】.

- 23. R. Liu, S. Chen, and T. Yoshimura, "Post-scheduling frequency assignment for energy-efficient high-level synthesis," in Proc. IEEE Asia Pacific Conference on Circuits and Systems, pp.588-591, Dec.2010.【本文引用】

- 24. S. Chen, Jianwei Shen, Wei Guo, Mei-fang Chiang, and T. Yoshimura. "Redundant Via Insertion: Removing Design Rule Conflicts and Balancing Via Density", IEICE Trans. on Fundamentals of Electronics, Communications and Computer Sciences, Vol.E93-A, No. 12, pp.1-8, December. 2010.(DOI: 10.1587/transfun.E93.A.2372)

- 25. Z. Lin, Y.P. Dong, Y. Li, and T. Watanabe: "A Hybrid Architecture for Efficient FPGA-based Implementation of Multilayer Neural Network", Proc. APCCAS'10, pp. 616-619, Malaysia, Dec. 2010.(DOI:978-1-4244-7456-4/10)

- 26. Xin Jin, Kun Ba and Satoshi Goto, "Low power parallel encoding system for video surveillance applications," International SoC Design Conference (ISOCC) 2010, Songdo Convensia, Incheon, Korea, Nov. 22-23, 2010.(DOI: 10.1109/SOCDC.2010.5682929)【本文引用】.

- 27. Tianruo Zhang, Xin Jin, Chen Liu, Minghui Wang, and Satoshi Goto, "ROI based Complexity Reduction Algorithm for H.264 Encoder", ISOCC 2010, Incheon, Korea, Nov. 22-23, 2010.(DOI:10.1109/SOCDC.2010.5682927)

- 28. Chen Liu, Xin Jin, Tianruo Zhang, Minghui Wang and Satoshi Goto, "Interactive partial video decoding for viewing resolution adaptation", ISOCC2010, Incheon, Korea, Nov. 22-23, 2010.(DOI:10.1109/SOCDC.2010.5682925)

- 29. S. Chen, Y. Yao, and T. Yoshimura, "A dynamic programming based algorithm for post-scheduling frequency assignment in energy-efficient high-level synthesis," in International Conference on Solid-State and Integrated-Circuit Technology (ICSICT), pp.794-796, November, 2010. (DOI: 10.1109/ICSICT.2010.5667427)【本文 引用】

- J. Liang, S. Chen, and T. Yoshimura, "Redundant via insertion based on conflict removal," in International Conference on Solid-State and Integrated-Circuit Technology (ICSICT), pp 797-799. November 2010. (DOI:10.1109/ICSICT.2010.5667425)

- 31. Y.P. Dong, Z. Lin, and T. Watanabe: "An Efficient Hardware Routing Algorithms for

- NoC", Proc. TENCON'10, pp.1525-1530, Japan, Nov. 2010.(DOI:978-1-4244-6888-1/10)

- 32. Shaopeng Tang, Satoshi Goto, "Accurate human detection by appearance and motion", IEICE Transactions on Information and System, VOL.E93-D, NO. 10, pp. 2728-2736, Oct. 2010 (DOI: 10.1587/transinf.E93.D.2728)

- 33. Xiongxin Zhao, Zhixiang Chen, Xiao Peng, Dajiang Zhou and Satoshi Goto, "A BER performance-aware early termination scheme for layered LDPC decoder", SIPS 2010, pp. 416-419, October 6th, 2010. (DOI: 10.1109/SIPS.2010.5624881)

- 34. Lei Chen and Shinji Kimura,"The Sizing of Sleep Transistors In Controlling Value Based Power Gating," Proc. of 16th Workshop on Synthesis And System Integration of Mixed Information Technologies, pp.202-207, October, 2010.【本文引用】

- 35. R. Nara, Kei Satoh, M. Yanagisawa, T. Ohtsuki, and N. Togawa, "Scan-based Side-channel Attack against RSA Cryptosystems using Scan Signatures," IEICE Trans. Fundamentals, vol. E93-A , no. 12, pp. 2481-2489 , Dec. 2010.(DOI:10.1587/transfun.E93.A.2481)【本文引用】

- 36. Youhua Shi, Kenta Tokumitsu, Nozomu Togawa, Masao Yanagisawa and Tatsuo Ohtsuki, "VLSI Implementation of a Fast Intra Prediction Algorithm for H.264/AVC Encoding," Proc. of IEEE APCCAS, pp.1139-1142, Dec. 2010. 【本文引用】

- 37. Y. Tsukamoto, M. Yanagisawa, T. Ohtsuki, and Nozomu Togawa, "A Fast Selector-based Subtract-multiplication Unit and its Application to Radix-2 Butterfly Unit," Proc. of IEEE APCCAS, pp. 1083-1086, Dec. 2010.

- 38. SeungJu Lee, M. Yanagisawa, T. Ohtsuki, and Nozomu Togawa, "BusMesh NoC: A Novel NoC Architecture Comprised of Bus-based Connection and Global Mesh Routers," Proc. of IEEE APCCAS, pp. 712-715, Dec. 2010.

- 39. X.Jiang and T.Watanabe: "An Efficient 3D NoC Synthesis by Using Genetic Algorithms," Proc.IEEE TENCON2010, pp.1207- 1212, Nov. 2010.(DOI:978-1-4244-6888-1/10)

- 40. SeungJu Lee, M. Yanagisawa, T. Ohtsuki, and Nozomu Togawa, "A Throughput-aware BusMesh NoC Configuration Algorithm Utilizing the Communication Rate between IP Cores," Proc. of SASIMI, pp. 96-101, Oct.2010.

- 41. Minghui Wang, Tianruo Zhang, Chen Liu and Satoshi Goto, "Region-of-Interest based Preprocessing for H.264/AVC Encoding", The Journal of the Institute of Image Electronics Engineers of Japan, Vol. 39, No. 5, pp.682-691, Sep. 2010.

- 42. Chen Liu, Tianruo Zhang, Xin Jin, Minghui Wang and Satoshi Goto, "Fast Inter Mode Decision Algorithm Based on Residual Feature", The Journal of the Institute

- of Image Electronics Engineers of Japan, Vol. 39, No. 5, pp. 663-671, Sep. 2010.

- 43. Guifen Tian, Tianruo Zhang, Satoshi Goto, "A macroblock homogeneity detection method and its application for block size detection in H.264/AVC", The Journal of the Institute of Image Electronics Engineers of Japan, Vol. 39, No. 5, pp.672-691, Sep. 2010.

- 44. Xin Jin and Satoshi Goto, "Hilbert Transform based Workload Estimation for Low Power Surveillance Video Compression", ICIP 2010, pp.4461-4464, Sep. 26th, 2010. (DOI: 10.1109/ICIP.2010.5651500)【本文引用】

- 45. Shaopeng Tang, Satoshi Goto, "Multi scale block histogram of template feature for pedestrian detection",ICIP2010, pp. 3493-3496, Sep. 26th,2010.DOI: 10.1109/ICIP.2010.5654039)

- 46. Xin Jin and Satoshi Goto, "Encoder Adaptable Difference Detection for Low Power Video Compression in Surveillance System", PCM 2010, part II, pp.285-296, Sep. 21th, 2010.(DOI: 10.1007/978-3-642-15696-0\_27)

- 47. Jinjia Zhou, Dajiang Zhou, Gang He and Satoshi Goto, "A Bandwidth Reduction Scheme and its VLSI Implementation for H.264/AVC Motion Vector Decoding", PCM2010,partII,pp.52-61,Sep.21th,2010.(DOI: 10.1007/978-3-642-15696-0\_6)

- 48. Wenxin Yu, Xin Jin, Satoshi GOTO, "Temporal scalable decoding process with frame rate conversion method for surveillance video", PCM 2010, part II, pp. 297-308, Sep. 21th, 2010(DOI: 10.1007/978-3-642-15696-0\_28)

- 49. S. Chen and T. Yoshimura. Multi-layer floorplanning for stacked ICs: Configuration number and fixed-outline constraints. Integration, the VLSI journal, 43(4):378-388, September, 2010.(DOI:10.1016/j.vlsi.2010.04.001)

- 50. Jiongyao Ye and Takahiro Watanabe: "A Variable Bitline Data Cache for Low Power Design", Proc.PrimeAsia2010, pp.174-177, Sep. 2010. 【本文引用】 (DOI:978-1-4244-6737-2/10)

- 51. Ce. Li, Yiping Dong and Takahiro Watanabe: "A Novel Low Power FPGA Architecture,"Proc.FIT2010, pp. 65-68, Sep.7, 2010. 【本文引用】

- 52. Y-P.Dong, Z.Lin and T.Watanabe: "High performance Networks on Chip Architecture with a New Routing strategy for Neural Network," Proc. PrimeAsia 2010, pp. 347-350, China, Sep. 2010.(DOI:978-1-4244-6737-2/10)

- 53. Liu Song, Dajiang Zhou, Xin Jin, Satoshi Goto, "A constant rate bandwdith reduction architecture with adaptive compression mode decision for video decoding", EUSIPCO-2010, pp. 2017-2021, Aug. 23rd, 2010.

- 54. Xun He, Jinjia Zhou, Dajiang Zhou and Satoshi Goto, "High profile intra prediction architecture for UHD H.264 decoder", IPSJ Transactions on System LSI Design

- Methodology, Vol. 3, No. 2, pp. 303-313, Aug. 2010. (DOI: 10.2197/ipsjtsldm.3.303)

- 55. Zhixiang Chen, Xiongxin Zhao, Xiao Peng, Dajiang Zhou and Satoshi Goto, "A High Parallelism LDPC Decoder with an Early Stopping Criterion for WiMax and WiFi Application", IPSJ Transaction on System LSI Design Methodology, Vol. 3, pp. 292-302, Aug. 2010. (DOI: 10.2197/ipsjtsldm.3.292)

- 56. Jinjia Zhou, Dajiang Zhou, Xun He and Satoshi Goto, "A bandwidth optimized, 64 cycles/MB joint parameter decoder architecture for ultra high definition H.264/AVC applications", IEICE Transactions on Fundamentals, Vol. E93-A, No. 8, pp. 1425-1433, Aug. 2010.(DOI: 10.1587/transfun. E93.A.1425)

- 57. Shaopeng Tang, Satoshi Goto, "Histogram of template for pedestrian detection", IEICE Transactions on Information and System, VOL.E93-D, NO. 7, pp. 1737-1744, July 2010, (DOI: 10.1587/transinf.E93.D.1737)

- 58. Xin Jin, Kun Ba and Satoshi Goto, "Low power surveillance video coding system," ICME 2010, pp. 1156-1157, July 21st, 2010. (DOI:10.1109/ICME.2010.5583167)

- 59. Xuena Bao, Dajiang Zhou, Peilin Liu and Satoshi Goto, "An Advanced Hierarchical Motion Estimation Scheme With Lossless Frame Recompression For Ultra High Definition Video Coding", ICME 2010, pp. 820-825, July 21st, 2010, (DOI: 978-1-4244-7492-9/10/)

- 60. Xiao Peng, Zhixiang Chen, Xiongxin Zhao, Fumiaki Maehara, Satoshi Goto, "High Parallel Variation Banyan Network Based Permutation Network for Reconfigurable LDPC Decoder", ASAP 2010, pp 233-238, July 7th, 2010.(DOI: 978-1-4244-6965-9/10)

- 61. Ning Jiang, Yijun Lu, Shaopeng Tang and Satoshi Goto, "A Set of Separate Haar Features for Rapid Face Detection", ITC-CSCC 2010, pp. 128-131, July 5th, 2010.

- 62. Wenxin Yu, Xin Jin, Satoshi GOTO, "Hierarchical low complexity decoding with frame-skipping for surveillance video", ITC-CSCC 2010, pp. 1152-1155, July 5th, 2010.

- 63. Y.P. Dong, H. Zhang, Z. Lin, and T. Watanabe: "A Novel Hardware Method to Implement a Routing Algorithm onto Network on Chip", Proc. ICCCCAS'10, pp. 852-856, China, Jul. 2010.(DOI:978-1-4244-8223-8/10)

- 64. Dajiang Zhou, Jinjia Zhou, Xun He, Ji Kong, Jiayi Zhu, Peilin Liu and Satoshi Goto, "A 530Mpixels/s 4096x2160@60fps H.264/AVC high profile video decoder chip", Symposium on VLSI Circuits 2010, pp. 171-172, June 18th, 2010.(DOI 10.1109/VLSIC.2010.5560311)【本文引用】

- 65. Muchen Li, Xin Jin and Satoshi Goto, "Ultra Low Bit Rate Video Coding for Surveillance System, ICGCS 2010, pp. 611-614, June 20th, 2010. (DOI: 10.1109/ICGCS.2010.5542989)

- 66. Zhixiang Chen, Xiongxin Zhao, Xiao Peng, Dajiang Zhou and Satoshi Goto, "An Early Stopping Criterion for Decoding LDPC Codes in WiMAX and WiFi Standards", ISCAS 2010, pp. 473-476, June 1st, 2010. (DOI: 10.1109/ISCAS.2010.5537638)

- 67. Xuena Bao, Dajiang Zhou, and Satoshi Goto, "A Lossless Frame Recompression Scheme for Reducing DRAM Power in Video Encoding," ISCAS 2010, pp. 677-680, June 1st, 2010. (DOI: 10.1109/ISCAS.2010.5537495)

- 68. Liu Song, Dajiang Zhou, Xin Jin, Peilin Liu, Satoshi Goto, "An adaptive bandwidth reduction scheme for video coding", IEEE International Symposium on Circuits and Systems (ISCAS2010), pp. 401-404, May 30th, 2010. (DOI: 10.1109/ISCAS.2010.5537728)

- 69. W. Zhong, S. Chen, and T. Yoshimura. "Whitespace Insertion for Through-Silicon Via Planning on 3-D SoCs. In Proc. IEEE International Symposium on Circuits and Systems (ISCAS), pp. 913-916. Paris, France, May 2010.(DOI: 10.1109/ISCAS.2010.5537404)

- 70. Y.P. Dong, C. Li, Z. Lin, and T. Watanabe: "Multiple Network-on-Chip Model for High Performance Neural Network," IEEK trans. JSTS, pp.28-36, vol.10, no.1, Mar, 2010. 【本文引用】

- Y.P. Dong, Z. Lin, Y. Li, and T. Watanabe: "High Performance Implementation of Neural Networks by Networks on Chip with 5-Port 2-Virtual Channels," Proc. ISCAS'10, pp.381-384, France, May. 2010.(DOI:978-1-4244-5309-2/10)

- 72. R. Nara, H. Atobe, Y. Shi, N. Togawa, M. Yanagisawa, and T. Ohtsuki, "State-Dependent Changeable Scan Architecture Against Scan-Based Side Channel Attacks, " Proc. of IEEE ISCAS, pp. 1867-1870, May 2010. (DOI: 10.1109/ISCAS.2010.5537859)

## (4-2) 知財出願

- ① 平成21年度特許出願内訳(国内 0件)

- ② CREST 研究期間累積件数(国内 0件)