平成 20 年度 実績報告

「次世代エレクトロニクスデバイスの創出に資する革新材料・プロセス研究」 平成19年度採択研究代表者

## 菅原 聡

東京工業大学大学院理工学研究科・准教授

ハーフメタル強磁性体を用いたスピン機能 MOSFET の開発

### 1. 研究実施の概要

本研究課題では、従来のエレクトロニクスの分野で用いられることのなかったキャリアのスピンや材料の磁性に関する自由度・機能を MOSFET に導入し、スピン自由度を用いた新しいシリコン集積回路技術を構築するための基礎体系を創出する。本研究課題は、①スピン MOSFET および②擬似スピン MOSFET の創出、③これらの機能デバイスによる高機能集積回路の実現からなる。

スピン MOSFET に関しては、まずソース/ドレインに用いるフルホイスラー合金のハーフメタル性に重要となる規則度を精密に評価する手法を開発した。この方法を我々の開発した RTA によるメタル・ソース/ドレインプロセスで作製したフルホイスラー合金  $Co_2FeSi$  薄膜に適応して、この $Co_2FeSi$  薄膜が高い規則度を有することなどを明らかにした。また、ドーパント原子の界面偏析現象を用いて  $Co_2FeSi/Si$  ショットキーコンタクトのバリアハイト制御を行い、 $Co_2FeSi$  をソース/ドレインとするスピン MOSFET の試作・評価を行った。さらに、フルホイスラー合金によるトンネルコンタクトの形成について検討を行った。

擬似スピン MOSFET に関しては、非晶質絶縁膜上での高 TMR 比 MTJ を実現し、当初の目標値(100%)を上回る 130%という高い TMR 比を室温で得ることができた。また、MTJ/CPP-GMR 素子によるスピン注入磁化反転の検討を開始した。また、上記 MTJ の実験結果から、我々の開発した MTJ の SPICE モデルのパラメータを抽出して、擬似スピン MOSFET のデバイス設計を行い、試作を開始した。

高機能集積回路への応用に関しては、擬似スピン MOSFET による不揮発性 SRAM の詳細な回路解析・性能評価を行った. また、350nm プロセス CMOS を用いて不揮発性 SRAM の試作を開始した.

#### **2. 研究実施内容**(文中にある参照番号は 4.(1)に対応する)

本研究課題は、以下の3項目から構成される、以下、スピンMOSFETをS-MOSFET、擬似スピ

ン MOSFET (Pseudo spin-MOSFET)を PS-MOSFET と略す. ①ハーフメタル強磁性体ソース/ドレイン S-MOSFET の開発, ②強磁性トンネル接合(MTJ)を用いた PS-MOSFET の開発, ③ PS-MOSFET, S-MOSFETを用いた高機能ロジックの開発. それぞれの研究項目について, 本年度の研究実施内容を示す.

## ① ハーフメタル強磁性体ソース/ドレイン S-MOSFET の開発

スピン MOSFET を実現するための重要課題は、ハーフメタル強磁性体(HMF)による強磁性ソース/ドレイン(S/D)技術の開発である。 スピン MOSFET はそのデバイス構造から近年注目を集めているメタル S/D MOSFET の一種であると考えられるが、 CMOS プロセスに整合できる HMF メタル S/D の形成と HMF/Si 接合におけるバリア高さ制御が重要な課題になる。 特に CMOS におけるメタル S/D 技術と同様に RTA(Rapid thermal annealing)によるシリサイド技術を HMF に応用することが重要である。

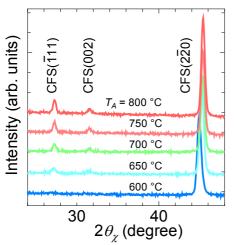

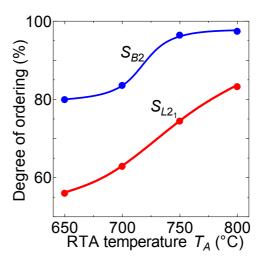

本年度は、我々がすでに開発した SOI(Si-on-insulator)基板を用いて、RTA によるシリサイド 化によって作製した  $Co_2FeSi(CFS)$ 薄膜の構造評価を詳細に行った。フルホイスラー合金のハーフメタル性はその規則度に強く依存しているため、フルホイスラー合金の規則度の評価技術を新たに確立した。Webstar による従来の方法の問題点を修正した解析モデルを提案して、本モデルを用いて RTA によって作製した  $Co_2FeSi$  薄膜の規則度を定量的に評価することに成功した<sup>1)</sup>。 RTA によって形成した  $Co_2FeSi$  薄膜の規則度の組成および RTA 温度の依存性を明らかにして、この薄膜が高い規則度を有することを明らかにした(図 1, 図 2).

図1 CFS 薄膜の In-plane 配置 X 線回折結果. L21 構造が確認された.

図 2 CFS 薄膜の B2 規則度と L21 規則度の RTA 温度依存性. バルクと同程度の高い規則度が得られた.

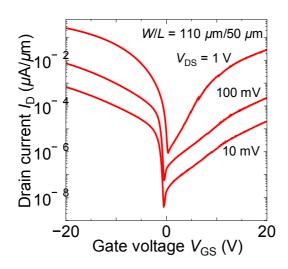

また、この SOI 基板を用いた RTA による  $Co_2FeSi$  の形成技術を利用して、 $Co_2FeSi$  をメタル・ソース/ドレインとしたスピン MOSFET の試作を行った。 $Co_2FeSi$  が Si のギャップ中の深い位置にピンニングされるため、両極性動作となるがトランジスタ特性を確認することができた(図 3). 次に、スピン MOSFET の機能実証のために、ドーパント不純物の界面偏析現象を利用してバリア

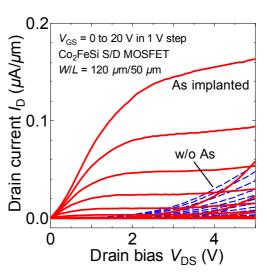

ハイトの低減技術の検討を試みた. As を浅くイオン注入した S/D 領域に RTA によるシリサイド 化によって  $Co_2FeSi$  を形成したところ, スピン MOSFET のオン電流が大きく増大して, As の界面 偏析によると考えられるバリアハイトの低減が確認された(図 4).

以上は SOI 型のスピン MOSFET についてフルホイスラー合金の形成についての検討結果であるが(単結晶の SOI 薄膜を用いた RTA にシリサイド化), トンネルコンタクトを用いれば, バルク型でもスピン MOSFET を実現できる。このためには絶縁体薄膜(トンネルバリア)上に直接フルホイスラー合金を作製する必要がある。昨年度は非晶質絶縁体(SiO $_2$ )上に堆積したアモルファスSiを用いれば, 絶縁膜上に直接 L2 $_1$  構造 Co $_2$ FeSi の形成できることを明らかにした。本年度はこの Co $_2$ FeSi 薄膜形成の詳細に検討し, さらに上述の規則度の評価技術をこの Co $_2$ FeSi 薄膜にも応用して, この薄膜が比較的に高い規則度を有する L2 $_1$  構造フルホイスラー合金であることを明らかにした。

図 3  $Co_2FeSi$  ソース/ドレイン MOSFET の  $I_D$ - $V_G$  特性(As の界面偏析なし)

図 4  $Co_2FeSi$  ソース/ドレイン MOSFET の  $I_D^-V_G$  特性. 赤線は As の界面偏析を行ったもの. 青破線は As を導入していないもの.

# ②巨大 TMR 比強磁性トンネル接合を用いた PS-MOSFET の開発

本研究項目では MTJ と MOSFET を組み合わせた PS-MOSFET を作製し、機能実証を行うことを目的としている。 PS-MOSFET は既存の MRAM 技術を利用してスピントランジスタによるエレクトロニクスを展開する技術である。 本年度は PS-MOSFET の実現に向けた非晶質絶縁膜(SiO $_2$ ) 上の高 TMR 比 MTJ の作製および、そのスピン注入磁化反転についての技術開発を行い、 擬似スピン MOSFET の詳細な性能予測(シミュレーション)およびデバイス設計・試作を開始した。

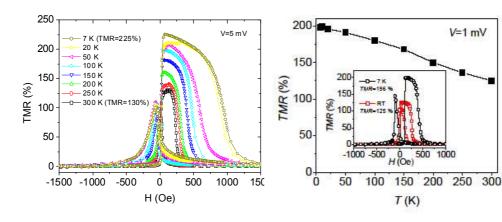

従来の MgO 単結晶基板に代わり、熱酸化 Si 基板上に高 TMR 比を有する MTJ 素子を作製するための技術開発を行った。具体的には、スパッタ法を用いて、SiO<sub>2</sub> 基板上に(100)配向した MgO バッファ層を形成し、その上に配向性の高い高品質のハーフメタル・フルホイスラー合金 ( $Co_2FeAl_{0.5}Si_{0.5}$ : CFAS)膜を用いて強磁性トンネル接合 (MTJ)素子を作製するプロセスを開発した。 CFAS に対する熱処理温度を最適化することで、室温において 130%という、期初目標(100%)を上

回る高い TMR 比を得ることができた $^{2)-4}$  (図 5、図 6)。また、これとは別に AlOx バリアを用いて MTJ を作製し、CFAS のスピン分極率 P を評価したところ、低温で P = 0.9 が得られ、CFAS は間違いなくハーフメタルであることを確認した。これにより、プロセス改善により TMR はまだかなり向上できる見通しを得た。上記の他、PS-MOSFET 試作のための試料として熱酸化 Si 基板および SiN バッファ上に CFAS 膜を作製し東工大 G に提供した。

また、上記ホイスラー合金、CFAS を用いた MTJ/CPP-GMR 素子のスピン注入磁化反転 (CIMS)電流を低減させるための研究を開始し、H20 年度は CIMS 観測のための評価装置・技術 の立ち上げを行った。微細加工によって低抵抗の微小 CPP-GMR( $0.2 \times 0.1 \cdot m^2$ )素子を作製し、CIMS の観測に成功、素子作製プロセスおよび評価技術の確立を行うことができた。また、Cu に 代わり Ag スペーサを用いることで CPP-GMR を大幅に増大(室温で  $0.2\% \rightarrow 12\%$ )できることを見 出した $^{50}$ 。次に、スピン注入磁化反転の実験を行うべく CFAS を用いた CFAS/Cr/Ag/CoFe から なる CPP-GMR 素子を作製し、微細加工によって微小な素子を作製した。このときの GMR は 3% 程度であった。この小さな値は上部電極に CoFe を用いたこと、および微細加工技術に問題があったことによるものと考えている。それでも、スピン偏極電流による磁化反転を観測することができた。これはホイスラー合金を用いた素子としては初めてである。電流密度  $J_{c0}$  は  $1\times 10^7$  A/cm²であり、従来材料を使用した場合に比べ 1/5 以下に低減しており、小さな GMR の割には CFAS 合金が期待できる結果となった。

PS-MOSFET に関しては、上記の非晶質絶縁膜 $(SiO_2)$ 上に作製したフルホイスラー合金 MTJ の電気特性を完全にフィットできる SPICE マクロモデルの開発し(前年度開発した SPICE モデル を基にモデルの修正を行った)、試作を予定している 350nm の CMOS プロセスを想定して PS-MOSFET の動作検証・性能評価を行い、試作のためのデバイス・回路設計を行った。この PS-MOSFET の設計には昨年度開発した設計手法を用いた。また、CMOS チップに MTJ をインテグレーションするためのプロセスを開発した。

図 5 熱酸化 Si 基板上の MTJ 素子の 各種温度における TMR 曲線

図 6 熱酸化 Si 基板上に作製した MTJ 素子の TMR の温度変化

### ③PS-MOSFET, S-MOSFET を用いた高機能ロジックの開発

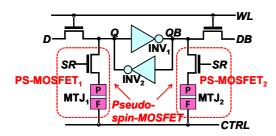

本研究課題ではPS-MOSFET またはS-MOSFET をインバータ・ループによる双安定回路の記憶ノードに接続すれば、不揮発性 SRAM、不揮発性ラッチ、不揮発性フリップ・フロップなどの不揮発性ロジックを構成できることを提案している。本年度は PS-MOSFET を用いた不揮発性 SRAM の回路解析・設計と試作を開始した。

まず、昨年度より開発した MTJ の SPICE モデルを用いて、PS-MOSFET を用いた不揮発性 SRAM(図7)の動作検証と回路解析を行った。ストア動作におけるTMR比、Vhalf、MTJ抵抗値の 影響や、ストア動作におけるデバイスディメンジョン効果など詳細に回路解析を行い、不揮発性 SRAM の設計指針を確立した。

また、350nm の CMOS プロセスを利用した PS-MOSEFT による不揮発性 SRAM の試作を開始した. プロセス上の要請は、外注で試作する CMOS 回路と我々で作製する MTJ とのインテグレーション技術である. CMOS 回路とMTJ の電気接続、 MTJ サイズによる高精度な抵抗値制御に関しては電子線リソグラフィーをベースとしたインテグレーション技術を開発し、また、CMOS チップ上に高 TMR 比の MTJ を実現することに関しては、CMOS チップのパッシベーション膜の影響を明らかにした.

図7 擬似スピン MOSFET を用いた不揮発性 SRAM の回路構成

#### 3. 研究実施体制

#### (1)「東工大」グループ

- ①研究分担グループ長:菅原 聡(東京工業大学、准教授)

- ②研究項目

RTA によるハーフメタル・フルホイスラー合金の形成とその S-MOSFET への応用 PS-MOSFET の性能評価と機能実証

PS-MOSFET, S-MOSFET を用いた高機能ロジックの提案・設計と性能予測

## (2)「NIMS」グループ

①研究分担グループ長:猪俣浩一郎(独立行政法人物質・材料研究機構、フェロー)

#### ②研究項目

巨大 TMR 比ハーフメタル MTJ の作製および低電流スピン注入磁化反転技術開発 PS-MOSFET の作製と機能実証

PS-MOSFET を用いた高機能ロジックの作製と評価

## (3)「東大」グループ

- ①研究分担グループ長:田中雅明(東京大学、教授)

- ②研究項目

PS-MOSFET の作製と機能実証

PS-MOSFET を用いた高機能ロジックの作製と評価

## 4. 研究成果の発表等

- (1) 論文発表 (原著論文)

- 1. Y. Takamura, A. Nishijima, Y. Nagahama, R. Nakane, and S. Sugahara, "Formation of Siand Ge-based Full-Heusler Alloy Thin Films Using SOI and GOI Substrates for the Half-Metallic Source and Drain of Spin Transistors", ECS Transactions, Vol. 16, pp.945-952, 2008.

- 2. W. H. Wang, H. Sukegawa, R. Shan, and K. Inomata, Appl. Phys. Lett. **93**, 182504-1-182504-3 (2008). "Large tunnel magnetoresistance in Co<sub>2</sub>FeAl<sub>0.5</sub>Si<sub>0.5</sub>/MgO/Co<sub>2</sub>FeAl<sub>0.5</sub>Si<sub>0.5</sub> magnetic tunneling junctions prepared on thermally oxidized Si substrates with MgO buffer".

- 3. W. H. Wang, H. Sukegawa, R. Shan, and K. Inomata, Appl. Phys. Lett. **93**, 122506-1-122506-3 (2008), "Fabrication of fully epitaxial magnetic tunnel junctions using *L*2<sub>1</sub>-ordered Co<sub>2</sub>FeAl<sub>0.5</sub>Si<sub>0.5</sub> electrodes and their tunneling magnetoresistance characteristics".

- 4. W. H. Wang, H. Sukegawa, R. Shan, T. Furubayashi and K. Inomata, Appl. Phys. Lett. **92**, 221912-1-221912-3 (2008), "Preparation and characterization of highly L2<sub>1</sub>-ordered full-Heusler alloy  $Co_2FeAl_{0.5}Si_{0.5}$  thin films for spintronics device applications".

- T. Furubayashi, K. Kodama, H. Sukegawa, Y. K. Takahashi, K. Inomata, and K. Hono, Appl. Phys. Lett. 93, 122507-1-122507-3 (2008), "Current-perpendicular-to-plane giant magnetoresistance in spin-valve structures using epitaxial Co<sub>2</sub>FeAl<sub>0.5</sub>Si<sub>0.5</sub> /Ag/ Co<sub>2</sub>FeAl<sub>0.5</sub>Si<sub>0.5</sub> trilayers".

- 6. K. Inomata, M. Wojcik, E. Jedryka, N. Ikeda and N. Tezuka, Phys. Rev. B 77, 214425-1-214425-9 (2008), "Site disorder in Co<sub>2</sub>Fe(Al, Si) Heusler alloys and its influence on junction tunnel magnetoresistance".

- 7. K. Inomata, N. Ikeda N. Tezuka, R. Goto, S. Sugimoto, M. Wojcik and E. Jedryka, Sci. Tech. Adv. Mater. **9**, 014101-1-014101-9 (2008), "Highly spin-polarized materials and devices for spintronics".

## (2) 特許出願

平成 20 年度 国内特許出願件数:1件(CREST 研究期間累積件数:1件)