「情報システムの超低消費電力化を目指した技術革新と統合化技術」 平成 18 年度採択研究代表者

# 後藤 敏

早稲田大学大学院情報生産システム研究科 教授

低消費電力メディア処理 SoC の研究

# 1. 研究実施の概要

メデイア情報処理システムの超低消費電力化実現のために、画像、暗号、誤り訂正符号の各方式の最適な分担、およびアルゴリズムの最適化をはかり、ハードウェア実装とソフトウェア実装の各観点から最適化をはかり、超低消費電力 LSI チップを開発し、従来技術と比較して 1/100 の電力削減を図ることで研究を進めている。(1)本年度は画像と暗号の一体化、画像と誤り訂正の一体化をデータ重要度に応じて処理の深さを変え、人間にとっては遜色のない、かつ安全性も保たれる技術を開発した。その結果、個々の技術で 1/2 程度の計算量を削減し、トータルで 1/4 程度の計算量を削減できた。(2)最も計算量と消費電力が必要となる画像のエンコーダに対して 1/2~1/3 の消費電力で実行可能な LSI を開発した。(3)3 次元フロアープランの導入で 25%のダイナミックパワーの削減を図れることが分かった。(4)新しいパワーゲーテイング手法の導入で、28%の電力削減を行うことができた。(5)オペコードビット/オペランド削減アルゴリズム、エネルギー最小化アルゴリズムの 3 つのアルゴリズムによって、プロセッサ全体で最大 12%の消費エネルギーを削減することができた。

#### 2. 研究実施内容

(文中にある参照番号は4.(1)に対応する)

画像処理、暗号処理、符号化処理等の領域を統合する方式をメディア情報の重要度に応じて、暗号強度や誤り訂正能力を適応的に変化させ、統合的観点から消費電力を削減する方式検討を継続して進めた。暗号処理と動画圧縮処理(H. 264)を一体化する方式として、画像の重要部分には暗号強度の強い「AES」を、非重要部分には暗号強度の弱い「ストリーム暗号」を適用する手法を提案し、計算量としてすべてを AES で暗号化する場合に比べて、

50%~83%の計算量を削減した[2]。誤り訂正と画像処理を一体化する方式として、画像の重要部分には訂正能力の強い「1/2 の符号化率をもつ LDPC」を、非重要部分には訂正能力の弱い「2/3 の符号化率をもつ LDPC」を適用し、前者は後者に比べて消費電力を 25%~56% の削減を行いことができた。

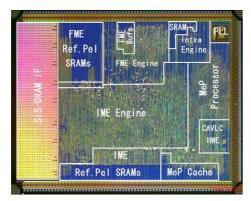

最も処理が重い画像処理部に対しては、コアとなる H.264 エンコーダの低電力化を引き続き進めている。昨年度開発した HDTV1080P エンコーダ SoC(世界初)は、新たに考案したローパスフィルタを用いた整数画素動き予測手法[4]や計算再利用を用いた小数画素精度動き予測処理 [5][14]などにより低演算量化を図り、ISSCC2005(台湾大)で発表されている LSI の 1/3~1/2(同等の仕様において)の低電力化を達成した。また、開発した LSI は、当該分野を代表する国際会議である Symposium on VLSI Circuits[12]に採択された。現在、本成果を発展させ、画像の内容に踏み込み周波数解析、背景解析、動き解析等を加えた、さらなる低電力化のためのアルゴリズム・アーキテクチャ検討を進めている。

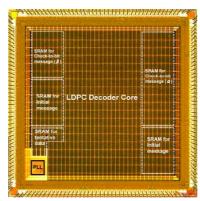

符号化処理に関しては、最先端の誤り訂正手法である LDPC(Low-Density Parity-Check Code)に焦点を当て、低電力化を進めている。我々は、DAC/ISSCC 2006 student design contest でアジアの大学で初めて1位を獲得したLSI 技術を有しているが、これを比較対象としてASPLA 90nm を用いたLSI 設計、評価を行った。FIFO バッファによる高効率スケジューリングやメモリ構成法、ブロックインタリーブ手法などを新たに考案[6]し、同じ処理性能当たりの電力を1/30(アーキテクチャの工夫による削減は1/3)に低減可能なLSI を実現した。本成果は、第9回LSI IP デザイン・アワードで表彰されている。また、低電力 LDPC の関連成果は ISLPED 2007 [11](日本からはこの一件のみ)に採択されている。現在、無線通信処理を含むベースバンド全体の低電力化の検討に着手している。

フルハイビジョン(1080p)向け実時間 H.264エンコーダーLSI (TSMC 0.18um)

1. 14Gb/s、符号長15,360ビット LDPCデコーダLSI (ASPLA 90nm)

応用システムの低電力化のための設計手法の研究の一環として、高位レベルでの配置配線の 正確な評価を行うためのフロアプラン手法の研究、演算モジュールの電力最適化手法の研究およ びゲートレベルでの細粒度パワーゲーティング手法の研究を行った。フロアプランに関しては、ま ずアルゴリズムの高精度化と高速化を行った。ベンチマークデータでの評価では従来システム比 で配線長を7~12%短縮、処理速度を2.7~4.9 倍に高速化した。またこの手法を3次元フロアプランに適用し、4層のフロアプランで配線長が50%削減できることを確認した。これにより、約25%のダイナミックパワーの削減が期待できる。演算モジュールに関しては、もっとも基本的である加算回路のプレフィックス木に対し、回路のスイッチング確率を最小化する手法を提案した。本手法は、与えられた遅延制約の元で、各ノードのスイッチング確率を最適化し、その総和を最小化する。また、ゲートレベルの細粒度のパワーゲーティングでは、論理素子の制御値に着目した論理素子の電力停止手法を提案し、制御対象のブロックを外部出力から決定する基本アルゴリズムと同時に、各論理ゲートのスイッチング確率を用いたヒューリスティックをいくつか提案し、その有効性の検討を計算機実験により行った。ベンチマーク回路による実験では、平均で28.1%のゲートの電力停止が可能であるという結果を得た。さらに、提案手法が、等価性判定回路や加算回路の桁上げ先見回路などで用いられているAND木やOR木の最適化に有効であることを示すと同時に、最適な木構造を示した。

ソフトウェア指向設計の研究では、新たな低電力化プロセッサを開発しその上に搭載されるソフトウェア面に着目して超低消費電力化を目指す。特にコンフィギュラブルプロセッサの概念を導入し、その最適化設計によってこれを実現する。VLIW型プロセッサはハードウェアリソースを抑えつつ並列に命令を発行可能であり、組み込み用途に適したアーキテクチャと言える。しかしながら命令メモリのビット幅が長くなり、消費電力・消費エネルギーを無駄に増加させてしまう。したがって、VLIW型プロセッサの命令メモリのビット幅の削減は、高性能でエネルギー効率の高いプロセッサを実現可能にすると考えられる。命令メモリのビット幅は命令エンコーディング形式に依存し、それはオペコードとオペランド群で構成される。オペコードのビット幅は命令セットにおける命令数に、オペランドのビット幅は汎用レジスタ数に依存する。また、我々はオペコードのビット幅を削減するために、結合命令の概念を導入した。結合命令は各VLIWスロットで同時に発行される複数の命令を1つの命令として取り扱った命令である。我々は、オペコードビット幅削減アルゴリズム、オペランドビット幅削減アルゴリズム、エネルギー最小化アルゴリズムの3つのアルゴリズムで構成される ASIP 合成システムを構築した。実験結果では、メモリを含むプロセッサ全体で、9~12%の消費エネルギーを削減することを確認した。また、本研究成果の一部をテスト設計に応用し、[15]に発表している。

#### 3. 研究実施体制

- (1)後藤グループ

- ① 研究分担グループ長:後藤 敏(早稲田大学大学院、教授)

- ②研究項目

- ・超低消費電力メディア処理 SoC

### 4. 研究成果の発表等

### (1) 論文発表(原著論文)

- [1] Xiang-hui Wei, Shen Li, Yang Song, Satoshi Goto, "An Irregular Search Window Reuse Scheme for MPEG-2 to H.264 Transcoding", IEICE Special Section on Signal Processing for Audio and Visual Systems and Its Implementation, pp.749-755, Mar., 2008

- [2] Yibo Fan, Jidong Wang, Takeshi Ikenaga, Yukiyasu Tsunoo, Satoshi Goto, "An Unequal Secure Encryption Scheme For H.264/AVC Video Compression Standard", IEICE Trans. Fundamentals, Vol. E91-A, No.1, pp. 12-21 Jan. 2008.

- [3] Yao Ma, Yang Song, Takeshi Ikenaga, Satoshi Goto, "A High Throughput Multiple Transform Architecture for H.264/AVC Fidelity Range Extensions", Journal of Semiconductor Technology and Science, Vol.7, No.4, Dec., 2007

- [4] Zhenyu Liu, Yang Song, Ming Shao, Shen Li, Lingfeng Li, Satoshi goto, Takeshi Ikenaga, "32-Parallel SAD Tree Hardwired Engine for Variable Block Size Motion Estimation in HDTV1080p Real-Time Encoding Application", IEEE Workshop on Signal Processing Systems (SiPS 2007), Oct. 2007.

- [5] Yang Song, Ming Shao, Zhenyu Liu, Shen Li, Lingfeng Li, Takeshi Ikenaga, Satoshi Goto, "H.264/AVC Fractional Motion Estimation Engine with Computation Reusing in HDTV1080p Real-Time Encoding Applications", IEEE Workshop on Signal Processing Systems (SiPS 2007), Oct. 2007.

- [6]Qi Wang, Kazunori Shimizu, Takeshi Ikenaga, Satoshi Goto, "Efficient Fully-Parallel LDPC Decoder Design with Improved Simplified Min-Sum Algorithms", IEICE Trans. Electron, Vol. E90-C, No. 10, pp. 1964-1971, Oct. 2007.

- [7] Liangwei Ge, Song Chen, Kazutoshi Wakabayashi, Takashi Takenaka, Takeshi Yoshimura, "Max-flow Scheduling in High-level Synthesis", IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences E90-A/9, 1940-1948, Sep., 2007

- [8] 森隆 寛, 外村 元伸, 大住 勇治, 後藤 敏, 池永 剛, "キュービック補間に基づく魚眼画像の高画質補正アルゴリズム及び専用ハードウェアエンジンの提案", 画像電子学会誌, Vol. 36, No. 9, pp.680-687, Sep., 2007

- [9] 伊東 健, 中村 創, 後藤 敏, 池永 剛, "デジタルシネマ用 JPEG 2000 エンコーダ向け並列 CBM アルゴリズム及び LSI アーキテクチャ", 画像電子学会誌, Vol. 36, No. 9, pp.650-656, Sep., 2007

- [10] Lingfeng Li, Yang Song, Shen Li, Takeshi Ikenaga, Satoshi Goto, "A Hardware Architecture of CABAC Encoding and Decoding with Dynamic Pipeline for H.264/AVC",

- The Journal of VLSI Signal Processing 2007, Springer Netherlands, Online Published in Aug., 2007

- [11] Kazunori Shimizu, Nozomu Togawa, Takeshi Ikenaga, Satoshi Goto, "Power-Efficient LDPC Code Decoder Architecture", IEEE International Symposium on Low Power Electronics and Design (ISLPED 2007), Aug. 2007.

- [12] Zhenyu Liu, Yang Song, Ming Shao, Shen Li, Lingfeng Li, Shunichi Ishiwata, Masaki Nakagawa, Satoshi Goto, Takeshi Ikenaga, "A 1.41W H.264/AVC Real-Time Encoder SOC for HDTV1080P", 2007 Symposium on VLSI Circuits, June 2007.

- [13] Yang Song, Zhenyu Liu, Takeshi Ikenaga, Satoshi Goto, "Lossy Strict Multilevel Successive Elimination Algorithm for Fast Motion Estimation", IEICE Trans. Fundamentals, Vol.E91-A, No.4, pp.764-770, Apr., 2007

- [14] Ming Shao, Zhenyu Liu, Satoshi Goto, Takeshi Ikenaga, "Lossless VLSI Oriented Full Computation Reusing Algorithm for H.264/AVC Fractional Motion Estimation", IEICE Trans. Fundamentals, Vol. E90-A, No. 4, pp. 756-763, Apr. 2007.

- [15] Youhua Shi, Nozomu Togawa, Masao Yanagisawa, Tatsuo Ohtsuki, "A Secure Test Technique for Pipelined Advanced Encryption Standard," IEICE Transactions on Information and Systems, vol. E91-D, no. 3, pp. 776-780, 2008.