「ディペンダブル VLSI システムの基盤技術」 平成 19 年度採択研究代表者

# 小野寺 秀俊

# 京都大学大学院情報学研究科 教授

ロバストファブリックを用いたディペンダブル VLSI プラットフォーム

# 1. 研究実施の概要

素子寸法の極限的な微細化に伴い、製造性劣化や素子特性のばらつき、使用に伴う特性劣化、ならびにソフトエラーなどの一過性雑音事象への耐性低下が問題となっている。本研究では、これらのディペンダビリティ阻害要因の排除を目的とし、適応的調整と再構成が可能な新しい VLSI プラットフォームを開発する。すなわち、ばらつきに強靭な構造を持ち特性の適応的調整が可能なロバストファブリック、各種の高信頼化構造の実現が容易な再構成アーキテクチャ、必要に応じた信頼度で逐次処理を実行可能な再構成プロセッサ、機能記述から再構成アーキテクチャへのマッピング技術を明らかにし、アプリケーションに応じたディペンダビリティを持つ VLSI システムが実現可能であることを示す。また、ディペンダビリティ評価手法の検討とともに本技術の応用展開を図る。

平成 19 年度は、研究開始にあたり各ディペンダビリティ阻害要因の実態把握と、それに対処する具体的な方法、ならびに達成目標の妥当性や達成の見通しの明確化を図ることに注力した。基本回路構成要素となるべきロバストファブリックについては、製造性を向上させるためのレイアウト構造を検討した。また、基板バイアスによる特性の自己調整可能量を評価した。再構成可能アーキテクチャについては、回路の冗長化による高信頼化が実現容易な基本回路の構成法を明らかにした。本アーキテクチャ上に実装するプロセッサについて、基本命令セットを定めるとともに、SERの定量的評価法について検討した。機能記述から再構成可能アーキテクチャ上へのマッピングについては、設計対象の耐故障性能をシミュレーションにより評価する環境を開発した。本技術の応用先として、宇宙用途以外に民生用途も念頭におき、ディペンダビリティの評価尺度について検討した。

平成20年度は、平成19年度に引き続き研究目標と解決方法のより一層の詳細化・具体化を図り、ディペンダビリティを静的に確保する技術の開発に取組む。平成21年度には、チップ試作により開発技術の効果を確認し、ホットスワップなどの動的ディペンダビリティ確保技術の開発に着手する計画である。

# 2. 研究実施内容

(文中にある参照番号は4.(1)に対応する)

本研究は、物理的・自然現象的ディペンダビリティ阻害要因を克服するため、回路技術、アーキテクチャ、プロセッサ、設計自動化技術を結集し、適応的調整と再構成が可能な VLSI プラットフォームを開発するものである。平成 19 年度の研究実施内容は、以下の通りである。

# (1) ロバストファブリック

ロバストファブリックは、ディペンダブル VLSI プラットフォームを構成する基本回路構成要素である。本年度はスタンダードセルを対象として、製造性を強化する技術、特性ばらつきを評価する技術、特性ばらつきを補償する技術について検討した。

製造性の強化については、レイアウトパターンに規則性を導入する事によりパターン複雑度を下げ、露光パターンの忠実性向上と焦点ずれへの耐性向上を図る方法を検討した。D フリップフロップを例にとり、レイアウト規則性に関する 2 種類の制約(等ピッチ制約と、等ピッチかつ同一方向制約)を加えた場合のゲートポリの仕上がり寸法(CD)ずれや、焦点ずれ量に対する CD ずれ量の増加割合を露光シミュレーション(65nm プロセスを想定)により評価した。その結果、ベストフォーカス条件では、回路内部の CD ばらつき量は規則性導入前の 6.8%から、それぞれ 2.7%と 1.3%に減少した。また、フォースずれに対する耐性も、規則性導入により大きく増加した[1]。一方、レイアウト面積は、規則性導入により、それぞれ 12%と 29%増加する。また、ポリの等ピッチ化により寄生容量が増加し、動作特性に影響が出る可能性がある。今後、これらの定量化が必要である。

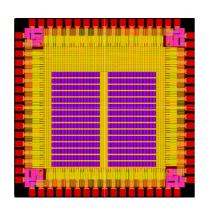

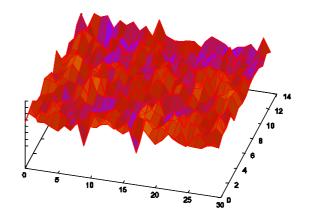

特性ばらつきの評価技術については、論理ゲート遅延のばらつき特性を正確に求めるために、統計的 MAX 演算の計算アルゴリズムと複数入力の同時遷移を考慮する方法について検討した。また、実チップにおけるばらつきを評価するために、90nm プロセスにおいてリングオシレータアレイを作成し、発振周波数ばらつきを評価した。図 1 に、試作チップとチップ面内における発振周波数分布を示す(Inv 7 段)。チップ上でなだらかに変化する成分は、ランダムな成分の約 1/5 であり、このチップ内ではランダム成分が支配的であった。今後、ばらつきの詳細なモデル化や、より広いチップ領域でのばらつき特性の評価が必要である。

特性ばらつきの補償技術として、基板バイアス電圧の調節による特性調整可能量を実験的に評価した。90nm プロセスで試作したリングオシレータでは、例えば 0.7V までの順方向バイアスにより、発振周波数は 71%増加した。今後、ばらつき補償や NBTI による特性劣化補償への適用方法を検討する。

#### (2) 再構成アーキテクチャ

本年度は、空間的冗長化が容易な再構成可能 VLSI アーキテクチャの基本セル(ALU)を検討した。構成情報保持部と演算回路部に分け、それぞれ要求ディペンダビリティに応じて多重化度が変更できる構成を考案した。宇宙利用のように、構成情報、演算回路ともに3 重化してソフトエラー

によるフォールトを回避し、一方で一般消費者向けの場合には、多重化しないことで回路機能の 集積度を維持する。フリップフロップやレジスタ等の記憶素子だけでなく、多数決回路を含めた組 み合わせ回路部で宇宙線によって発生するグリッチについても回避できるよう、多数決回路の多 重化や他のセルとの接続も多重化できる構成を取る。

構成情報の情報量が、デバイスの面積オーバーヘッドやソフトエラー率の上昇に直結するため、 過去のアプリケーションマッピングに関するノウハウをもとに、回路割り当ての柔軟性を適切に制限 して、構成情報量を小さく抑えた。

さらに次年度以降のチップ試作に向けて、基板バイアスによる性能調整機能を実現するためのレイアウト方式について検討を行った。90nm プロセスで試作したテストチップのリングオシレータの測定結果より、スタンダードセルの外部からストラップ形式で基板電位を印可する方式で、十分な電位制御性を実現できることが分かった。設計実験の検討により、面積オーバヘッドや配線長の増加を 1%程度に抑えることができることを明らかにした. クロック分配の製造ばらつきに対する耐性を定量的に評価し、ランダムなばらつきにはメッシュ型分配が強いことが分かった。次年度以降のVLSI 試作に得られた知見を利用する。

#### (3) 再構成プロセッサ

本年度は、ロバストファブリック上プロセッサ用の命令セットとして、12 ビット長命令で構成される、コンパクトな命令セットを定めた。この命令セットを用いて、高信頼性モードを備えたプロセッサの仮実装を行った。このプロセッサでは、高信頼性が要求されない場合は、複数の命令パイプラインで異なる命令を実行することで命令レベル並列性の利用による高性能を実現し、高信頼性が要求される時は、複数の命令パイプラインで同一の命令を実行し、各ステージの出力に備えられた比較器で結果を比較するものである。本プロセッサコアは、0.18 μm プロセスにおいて 0.20 mm² という小領域に実装可能であったため、来年度以降に命令セットの拡張を検討する。

また、SER の定量的評価法について検討した結果、FO4 のインバータ 11 段で構成した組み合わせ回路の SER はラッチや SRAM の SER よりも 1 桁小さいが、無視できるものではないという結論を得た。例えば、90nm の LSI では、海面レベルにおいて SET の頻度は 3.1E-4 FIT、ラッチの SER は 3.2E-4 FIT、SRAM の SER は 1.6E-3 FIT となった。一方、組合せ回路の SER は多く見積もって 9.9E-5 FIT であった。更に、プロセッサ内のキャッシュ用 SRAM において、SEU の発生からそれが発覚するまでのサイクル数を評価した。その結果、4MB の大容量キャッシュにおいても、1 ライン上に複数の SEU が発生する確率は 1 日あたり 7.2E-9 回と低く、SEU 対策として ECC が有効であるとの結論を得た。

#### (4) マッピング技術

今年度は、再構成デバイスのアーキテクチャの変更に柔軟に対応できるリターゲッタブルなマッピングツールの開発に着手し、さらに、このようにしてマッピングされたデバイスのソフトエラー耐性をシミュレーションベースで評価する枠組みも開発し、アーキテクチャ評価環境の構築に向け大き

く前進した。この評価環境では、様々な耐故障機構をもつアーキテクチャを対象とし、性質の異なる様々なアプリケーションを実行させた際に、発生するソフトエラーの中で演算結果に影響を与える(sensitive)もの、特に持続的な誤りを引き起こす(persistent)ものがどの程度占めるのかを定量的に評価することが可能である。さらに再構成アーキテクチャグループとも定期的に情報交換を行い、候補となっているアーキテクチャに上記評価環境を適合させる方策を検討した。

# (5) アプリケーション展開に向けた評価・実用化検討

暗号通信回路への展開を図る際の評価用プラットフォームとして、R3000 互換プロセッサと AES 暗号処理専用回路からなる組込みシステムの RTL 記述を作成し、論理シミュレータと FPGA にて動作を確認した。本システムは、専用回路もしくはプロセッサが解釈実行する手順(C 言語記述)を置き換えることにより、暗号通信以外のアプリケーションに適用可能である。今後は、ディペンダビリティ改善を行うためのアーキテクチャレベルでのプラットフォームとして活用する。また、今年度はディペンダビリティの評価尺度を定義するための要件調査として、JAXA、輸送機器メーカ、半導体企業に対するヒアリングを行った。さらに機能安全規格(IEC61508)等の調査を行った。

図 1 ばらつき評価のためのリングオシレータアレイチップ(90nm プロセス)と、チップ面内における 発振周波数分布

# 3. 研究実施体制

- (1) 京大グループ

- ①研究分担グループ長:小野寺 秀俊(京都大学、教授)

- ②研究項目

- •ロバストファブリック

- ・再構成プロセッサ

- ・再構成可能ディペンダブル VLSI へのマッピング技術

- (2)阪大グループ

- ①研究分担グループ長:尾上 孝雄(大阪大学、教授)

- ②研究項目

- ・ディペンダブル VLSI プラットフォーム用再構成可能 VLSI アーキテクチャ

- (3)京都高度技術研究所グループ

- ①研究分担グループ長:神原 弘之(京都高度技術研究所、主席研究員)

- ②研究項目

- ・ディペンダブル VLSI プラットフォームのアプリケーション展開に向けた評価・実用化検討

# 4. 研究成果の発表等

- (1) 論文発表 (原著論文)

- [1] Hirokazu Muta, Hidetoshi Onodera, "Manufacturability-Aware Design of Standard Cells", IEICE Trans. on Electronics, vol E90-A, no 12, pp. 2682-2960, 2007/12.