「情報システムの超低消費電力化を目指した技術革新と統合化技術」 平成 18 年度採択研究代表者

# 後藤 敏

(早稲田大学大学院情報生産システム研究科 教授)

「超低消費電力メデイア処理 SoC の研究」

#### 1. 研究実施の概要

(1) 画像処理、暗号処理、符号化処理等の領域を統合する方式をメディア情報の重要度に応じて、暗号強度や誤り訂正能力を適応的に変化させ、統合的観点から消費電力を削減する基本方式を検討した。動画圧縮処理と誤り訂正処理を最適に組合せると従来の処理を独立に行う方法に比べて、動画の品質を保ちながら、40%の計算量を減らす方式を考案した。(2) 動画像処理に対してH.264 エンコーダチップの低消費電力化を図り、現状までに提案されている最良方式に比べて、約1/2の電力で実行できることを確認した。(3) ハードウェア指向設計の研究において、アルゴリズムレベルで最適化されたC/C++のプログラムに対し、それをハードウェアとして実現する上での低消費電力を目指した高位レベルでの配置配線の評価精度を向上する新しいモデリングを用いたフロアプラン手法の基本アルゴリズムの研究を行った。(4) ソフトウェア指向設計の研究では、新たな低電力化プロセッサを開発しその上に搭載されるソフトウェア面に着目して超低消費電力化を目指し、コンフィギュラブルプロセッサの概念を導入し、「不必要な命令」の削除、とりわけメモリアクセス最小化の観点から、アプリケーションプログラムに対して最適な命令再合成アルゴリズムの構築に取り組んだ。

### 2. 研究実施内容

画像処理、暗号処理、符号化処理等の領域を統合する方式をメディア情報の重要度に応じて、暗号強度や誤り訂正能力を適応的に変化させ、統合的観点から消費電力を削減する 基本方式を検討した。動画圧縮処理と誤り訂正処理を最適に組合せると従来の処理を独立 に行う方法に比べて、動画の品質を保ちながら、40%の計算量を減らす方式を考案した。

最も処理が重い画像処理部(特に最先端の画像圧縮技術である H.264)の低電力化が不可欠であり、最終目標としては、ハードウェアアルゴリズムの改良により、1/10の消費電力とすることを目指しているが、今年度は、現時点での世界における位置づけを明確化するため、CRESTで得られた成果のみならず、過去に我々のチームで蓄積してきた技術も総動員して、SoCの設計・評価を行った。比較対象としては、ISSCC2005において台湾大から発表されたH.264 エンコーダを取り上げた。このLSIは、720PのH.264 エンコーダを 31.7mm²、785mW で実現している。ただし、コ

アのみの実現であり、画像エンコーダシステム実現のためにはプロセッサ、外部バス、I/O、SRAM、DRAM および DRAM I/F が必要である。 設計したSoCは、HDTV1080P(世界初)を対象とし、コアだけでなく、DRAM (SiS DRAM) やプロセッサ (MeP) を含むSoCとなっている。エンコーダの 9割以上の処理を占めるIME、FME処理に対し、ローパスフィルタの適用や独自のメモリーマネージメント手法、計算再利用手法等を適用している。評価により、27.1mm²で1409mWを達成した。 処理する画素数が2倍以上になっており、かつDRAMやプロセッサの電力も勘案すると、台湾大のLSIの1/2の低電力化が達成できていることが確認された。 今後は、さらなる低電力化の検討や、暗号・誤り訂正機能との融合、他のサブチームの成果との融合を通じて、最終目標を目指して検討を進める予定である。

ハードウェア指向設計の研究においては、アルゴリズムレベルで最適化されたC/C++ の プログラムに対し、それをハードウェアとして実現する上での電力最適化アルゴリズムの 研究を行う。今年度は、高位レベルでの配置配線の評価精度を向上する新しいモデリング を用いたフロアプラン手法の基本アルゴリズムの研究を行った。また、高位合成における ハードウェアのデータパスの最適化手法および回路の部分的なパワーオフについて、論理 合成と組み合わせた手法の基礎的な研究を行った。フロアプランのモデリングについては、 フロアプランを表すブロックのシーケンス情報から、ブロックの位置情報を計算する高速 計算法を提案し、フロアプランにおける配線長などの見積もり精度を向上させることがで きた。これにより、高位レベルでの電力の推定精度を向上させることができる。また本手 法をフロアプラン最適化手法の一つであるシミュレーティッドアニ―リングに組み入れる ことで、最適なフロアプランを求める手法の高速化を達成した。高位合成におけるデータ パスの最適化については、浮動小数点変数を最適な長さの固定小数点変数へ変換する最適 化手法を提案した。本手法は領域計算、アフィン算術、誤差解析と非線形最適化問題のソ ルバーを用いている。浮動小数点数の固定小数点化で、浮動小数点演算における桁あわせ と正規化部分のハードウェアを削減できる。また、回路の動的なパワーオフに関しては論 理ゲートの制御値に着目し、制御値を用いて細かい単位でパワーオフを行う手法を提案し た。現在パワーオフできる領域を最適化するアルゴリズムの開発を行っている。

ソフトウェア指向設計の研究では、新たな低電力化プロセッサを開発しその上に搭載されるソフトウェア面に着目して超低消費電力化を目指す。特にコンフィギュラブルプロセッサの概念を導入し、その最適化設計によってこれを実現する。現状、汎用マイクロプロセッサでは、その性質上 30%あるいはそれ以上に「不必要な命令」があると言われている。この事実に着目し、特定の画像処理アプリケーションプログラムあるいは通信処理アプリケーションプログラムに特化した上で「不必要な命令」の削除、とりわけメモリアクセス最小化の観点から、アプリケーションプログラムに対して最適な命令再合成アルゴリズムの構築に取り組んだ。構築する命令再合成アルゴリズムは、主に、複数の命令を1つの命令に圧縮し、複数の命令を1命令で発行することで擬似的にVLIW(Very Long Instruction Word)方式の命令を発行することに基づく。命令の並列性を失うことなく命令ビット幅を削減する。どのような命令を1つの命令に再符号化するかが最大の鍵となる。命令再合成アルゴリ

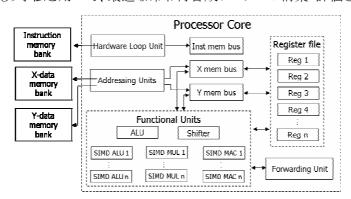

ズムの構築に必要なアーキテクチャとして、VLIW 方式の命令形式に特化したスケーラブルなコンフィギュラブルプロセッサのアーキテクチャ(図 1)を考案し、その上で、面積・遅延・消費電力見積りの方法論を確立した。

スケーラブルなコンフィギュラブルプロセッサのアーキテクチャと見積もり手法を、想定しているアプリケーションとして画像処理を用いて評価した結果、提案する見積もり手法は 90%程度の精度を有していることを確認した。

今後、本年度において確立されたコンフィギュラブルプロセッサアーキテクチャとその面積・遅延・消費電力見積もり手法を用いて、最適な命令再合成システムの構築・評価を行う。

図1: プロセッサアーキテクチャの構成

# 3. 研究実施体制

- (1)「後藤」グループ

- ①研究分担グループ長:後藤 敏(早稲田大学大学院情報生産システム研究科 教授)

- ②研究項目

- ・超低消費電力メディア処理SoC

# 4. 研究成果の発表等

### (1) 論文発表(原著論文)

- Yang Song, Zhenyu Liu, Takeshi Ikenaga, Satoshi Goto, "Low-Power Partial Distortion Sorting Fast Motion Estimation Algorithms and VLSI Implementation", IEICE Trans. Inf. & Syst., Vol. E90-D, No. 1, pp. 108-117, Jan. 2007.

- O Shen Li, Lingfeng Li, Takeshi Ikenaga, Shunichi Ishiwata, Masataka Matsui, Satoshi Goto, "Content-based complexity reduction methods for MPEG-2 to H.264 video transcoding", IEICE Trans. Inf. & Syst., Vol. E90-D, No. 1, pp. 90-98, Jan. 2007.

- O Zhenyu Liu, Yang Song, Satoshi Goto, Takeshi Ikenaga, "A Fine-Grain Scalable and Low Memory Cost Variable Block Size Motion Estimation Architecture for H.264/AVC", IEICE Trans. Electronics, Vol. E89-C, No. 12, pp. 1928-1936, Dec. 2006.

- O Kazunori Shimizu, Tatsuyuki Ishikawa, Nozomu Togawa, Takeshi Ikenaga, Satoshi Goto,

- "Power-Efficient LDPC Decoder Architecture based on Accelerated Message-Passing Schedule", IEICE Trans. Fundamentals, Vol. E89-A, No. 12, pp. 3602-3612, Dec. 2006.

- O Yang Song, Zhenyu Liu, Takeshi Ikenaga, Satoshi Goto, "A VLSI Architecture for Variable Block Size Motion Estimation in H.264/AVC with Low Cost Memory Organization", IEICE Trans. Fundamentals, Vol. E89-A, No. 12, pp. 3594-3601, Dec. 2006

- O Nobuhiro DOI, Takashi HORIYAMA, Masaki NAKANISHI, and Shinji KIMURA, "Bit-Length Optimization Method for High-Level Synthesis based on Non-Linear Programming Technique," IEICE Trans. on Fundamentals, Vol. E89-A, No. 12, pp.3427-3434, Dec. 2006.