「超高速・超省電力高性能ナノデバイス・システムの創製」 平成14年度採択研究代表者

# 古屋 一仁

## (東京工業大学理工学研究科 教授)

# 「超へテロナノ構造によるバリスティック電子デバイスの創製」

#### 1. 研究実施の概要

本研究では、半導体、金属そして絶縁体と大きく異なる物質を、立体的かつナノメートルサイズで組み合わせた "3次元超へテロナノ構造"を創製し、バリスティック走行による超高速性、極小化による低消費電力性をもつ新しいデバイス実現をめざす。さらに、3次元超へテロナノ構造により、電子の波動性を使う多機能デバイスの可能性、電子波の量子効果による新たなテラヘルツ帯増幅などの新デバイスの可能性を示す。

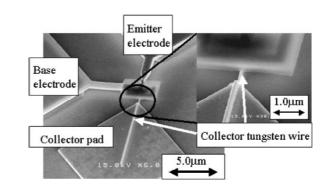

これまで、InP中の金属細線1本(100nm幅)をコレクタとする世界最小エミッタ (100nmx500nm)へテロ接合バイポーラトランジスタ (HBT) の増幅動作、ショットキー構造をソース/ドレインとするゲート長25nmのSi-MOSFETの増幅動作、真性領域のみを走行領域とするバリステックトランジスタ(BT)での二桁台の電流利得など、3次元超へテロナノ構造を用いた電子デバイスの動作を実証した。

また、電子波デバイス原理の探究として、半導体中のダブルスリット構造(スリット間隔25nm)による干渉像を観測した。テラヘルツ領域増幅としては、スロットアンテナと集積化した共鳴トンネルダイオードによる254GHzでの発振を確認するとともに、半導体中2次元電子ガスを用いたクライストロンを提案している。

今後、HBT/BTではマイクロ波特性による高速性の実証を、半導体クライストロンでは THz 帯発振の確認を目指す。

#### 2. 研究実施内容

本研究における研究実施方法・現時点での 成果を、以下の三つの項目に分けて述べる。

# 3次元超ヘテロナノ構造を電荷供給部/収 受部として持つデバイス

InP中に埋め込まれる金属細線の本数に対する、その上に成長するInP層厚の依存

性を明らかにし、それを元に幅100nmの金属細線1本をコレクタとするヘテロ接合バイポーラトランジスタ (HBT) を作製した。コレクタ抵抗低減の為に金属細線高さは200nmと従来に比べて2倍とした。作製した幅100nm長さ500nmのエミッタ領域をもつHBTで電流増幅動作を確認した。我々の知る限り世界最小面積のバイポーラトランジスタである。今後、マイクロ波特性評価により容量減少を確認し高周波特性向上を狙う。

# 超ヘテロナノ構造により電子を真性半導体へ引きだすバリステックトランジスタ

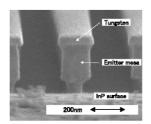

微細金属からなるゲート電極を正バイアスしヘテロバリアエミッタからホットエレクトロンを真性InP半導体へ引き出して走行させるバリステックトランジスタを作製した。へ

テロバリアエミッタはGaInAs/AlAs/GaInAs/AlAs/InP ダブルバリア構造からなる。従来の構造では一様な エミッタの上部に微細金属ゲートが存在し、エミッ タからゲート電極へ流れ込む電流の割合が大きかっ た。この問題を解決するために、エミッタ形成後そ のエミッタをマスクとしてゲート電極を形成するエ ミッタアップ形に構造を変更してトランジスタを作 製した。その結果、二桁台の電流利得を得、従来 (0.5程度)に比べて飛躍的に進歩した。さらにリー クを抑制し、エミッタ電流のゲート電圧による制御

エミッタアップ構造バリステックト ランジスタのエミッタメサの断面電 子顕微鏡像

性を向上させるために、ゲート金属を半導体で埋め込むことはやめ、またエミッタ幅を細くする構造上の改良を行った。エミッタ幅150nmのトランジスタで、ゲート電圧よるコレクタ電流変調特性を測定したところ、これまで観測できなかった、エミッタのダブルバリア共鳴トンネル現象に基づく線形特性とNDR特性を観測した。現在、エミッタ幅のさらなる縮小化を目指してエミッタメサ形成エッチング条件を把握し、微細エミッタバリスティックトランジスタの作製を行っている。

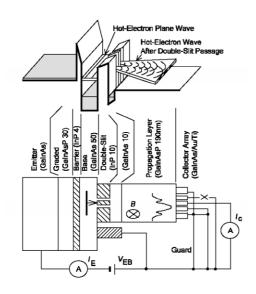

### 電子波面制御デバイス・電子波ビートデバイスなどの新原理デバイスの探究

電子波干渉現象観測のための素子構造概念図

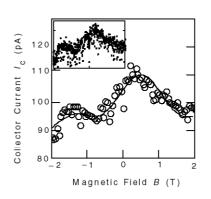

干渉現象観測素子の コレクタ電流の磁場中での変化

ホットエレクトロン平面波を InP/GaInAs3次元へテロナノ構 造からなるダブルスリットに入 射させ、伝搬後に現れる干渉パ

ターンを微細電極で観測した(構造図)。スリット間隔は25nm、検出電極周期は80nmであった。液体へリウム温度下で測定した。干渉パターンを微細電極上で磁場掃引して現れた電流の磁場依存特性(測定結果図)は、理論的検証により、ダブルスリット回折像であることを確認した。

GaInAs/AlInAs/InP共鳴トンネルダイオードとスロットアンテナとを集積化したテラヘルツデバイスを作製し254 GHzでの発振を得た。さらに半導体2次元電子ガスを用いたクライストロンを提案した。GaInAs/InAlAs/InP HEMT構造によるテラヘルツ帯で動作する半導体クライストロンの、現状技術で作製可能なサイズでの設計を完了し、現在試作に取りかかっている。

#### 3. 研究実施体制

古屋グループ

- ① 研究分担グループ長:古屋 一仁(東京工業大学理工学研究科、教授)

- ② 研究項目:超ヘテロナノ構造によるバリステック電子デバイスの創製

### 4. 主な研究成果の発表 (論文発表および特許出願)

# (1) 論文発表

○ T. Tanaka, K. Tokudome and Y. Miyamoto, "Effects of Low-Oxygen-Content Metalorganic Precursors on AlInAs and High Electron Mobility Transistor Structures with the Thick AlInAs Buffer Layer" Jpn. J. Appl. Phys. Vol. 42 Part 2, No. 8B, L993-L995 : (2003)

- K. Furuya, Y. Ninomiya, N. Machida, and Y. Miyamoto, "Young's Double-Slit Interference Observation of Hot Electrons in Semiconductors", Phys. Rev. Lett., Vol. 91, No. 21, pp. 216803-1 216803-4, Nov. 2003.

- O K. Yokoyama, K. Matuda, T. Nonaka, Y. Miyamoto, and K. Furuya, "Fabrication of GaInAs/InP Heterojunction Bipolar Transistors with a Single Tungsten Wire as Collector Electrode", Jpn. J. Appl. Phys., Vol. 42, No. 12B, pp. L1501-L1503, Dec., 2003.

- Y. Miyamoto, R. Yamamoto, H. Maeda, K. Takeuchi, N. Machida, Lars-Erik Wernersson, and K. Furuya, "InP Hot Electron Transistors with a Buried Metal Gate", Jpn. J. Appl. Phys., Vol. 42, No. 12, pp. 7221-7226, Dec., 2003.

- O K. Takeuchi, H. Maeda, R. Nakagawa, Y. Miyamoto, and K. Furuya, "InP Hot Electron Transistors with Emitter Mesa Fabricated between Gate Electrodes for Reduction in Emitter-Gate Gate-Leakage Current", Jpn. J. Appl. Phys. Vol. 43, No. 2A, pp. L183-L186, Jan., 2004.

- O M. Asada and M. Yamada, "Theoretical analysis of interaction between electron beam and electro- magnetic wave for unidirectional optical amplifier", J. Appl. Phys., vol. 95, No9 May, 2004.

- M. Asada, "Proposal and Analysis of a Travelling-Wave Amplifier in Terahertz Range Using Two-Dimensional Electron Gas", Jpn. J Appl. Phys., vol. 43, No. 4A, 2004, pp. 1332-1333 Apr., 2004

#### (2) 特許出願

H15年度特許出願件数:0件(CREST研究期間累積件数:0件)