「素材・デバイス・システム融合による革新的ナノエレクトロニクスの創成」 平成 26 年度採択研究代表者

2018 年度 実績報告書

# 橋本 昌官

# 大阪大学大学院情報科学研究科 教授

ビアスイッチの実現による アルゴリズム・処理機構融合型コンピューティングの創出

# § 1. 研究成果の概要

本研究では、IoT(Internet of Things)に代表される組み込み用途において、専用ハードウェア化による高いエネルギー効率、ソフトウェア実装と同等の設計生産性、低い NRE(Non-recurring Expense)コストのすべてを実現する新たなアルゴリズム・処理機構融合型コンピューティングを創出し、その実現に不可欠な新ナノデバイスとしてビアスイッチを開発する。 上記の目的の実現に向け、平成30年度は主に以下の研究項目を実施した。

# ビアスイッチデバイス開発

- カルコゲナイドバリスタの研究 (デバイス Gr.)

- スニークパスを回避するプログラミング順 (テスト Gr.) [1] ビアスイッチのプログラミング順を適切に決めることで、スニークパス問題が回避できることを証明した[1]。

#### 高エネルギー効率アーキテクチャの開発

- ビアスイッチ FPGA 向け設計ツール開発(マッピング Gr.)

- ビアスイッチ FPGA クロスバ基本回路の設計 (回路 Gr.)

- 機械学習/AI 向け大規模積和演算アクセラレータ (アーキテクチャ Gr.)

- CNN の小規模 FPGA への効率的実装 (動作合成 Gr.)

#### ビアスイッチ FPGA の試作

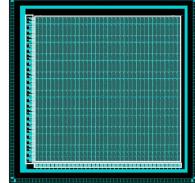

- ビアスイッチ FPGA の設計 (アプリケーション Gr.) これまでの検討[2]に基づき、大規模並列計算が実行しやすい FPGA アーキテクチャを設計 し、レイアウト設計まで完了した(図 1)。

- ビアスイッチ FPGA の設計検証 (テスト Gr.)

- チップレベル性能見積もり (回路 Gr.) ビアスイッチ性能と FPGA 性能との関係を調査するため、ビアスイッチの性能評価モデルを作成し、チップレベルの性能を評価した[3]。

- ビアスイッチ FPGA 向けツール提供(マッピング Gr.)

- ビアスイッチ FPGA の試作 (デバイス Gr.)

図1: 設計したビアスイッチFPGA

### 【代表的な原著論文】

- 1. R. Doi, J. Yu, and M. Hashimoto, "Sneak Path Free Reconfiguration of Via-Switch Crossbars Based FPGA," Proc. International Conference on Computer-Aided Design (ICCAD), 2018.

- 2. H. Ochi, K. Yamaguchi, T. Fujimoto, J. Hotate, T. Kishimoto, T. Higashi, T. Imagawa, R. Doi, M. Tada, T. Sugibayashi, W. Takahashi, K. Wakabayashi, H. Onodera, Y. Mitsuyama, J. Yu, and M. Hashimoto, "Via-Switch FPGA: Highly-Dense Mixed-Grained Reconfigurable Architecture with Overlay Via-Switch Crossbars," IEEE Trans. VLSI Systems, 26(2), pp. 2723–2736, 2018.

- 3. T. Higuchi, T. Ishihara, H. Onodera, "Performance Modeling of VIA-switch FPGA for Device-Circuit-Architecture Co-Optimization," Proc. International System-on-Chip Conference, pp. 112–117, 2018

# § 2. 研究実施体制

- (1)「テスト・アプリケーション」グループ

- ① 研究代表者:橋本 昌宜(大阪大学大学院情報科学研究科、教授)

- ② 研究項目

- ・ビアスイッチ FPGA の設計と検証

- ・スニークパス問題を回避するプログラミング順の検討

- ・配線遅延解析法の検討

- (2)「ビアスイッチ・動作合成」グループ

- ① 主たる共同研究者:杉林 直彦 (日本電気株式会社グリーンプラットフォーム研究所、シニアマネージャー)

- ② 研究項目

- ・ビアスイッチの研究開発

- ・ビアスイッチ FPGA の試作

- ・CNN の小規模 FPGA への効率的実装法

- (3)「アーキテクチャ」グループ

- ① 主たる共同研究者:密山 幸男 (高知工科大学システム工学群、准教授)

- ② 研究項目

- ・機械学習向け多オペランド演算アクセラレータの開発

- (4)「回路」グループ

- ① 主たる共同研究者:小野寺 秀俊 (京都大学大学院情報学研究科、教授)

- ② 研究項目

- ・チップレベル性能予測

- ・基本レイアウト構造の検討

- (5)「マッピング」グループ

- ① 主たる共同研究者:越智 裕之 (立命館大学情報理工学部、教授)

- ② 研究項目

- ・ビアスイッチ FPGA 向け設計ツールの整備と提供

- ・混合粒度再構成可能アーキテクチャのための配置アルゴリズム開発

- ・ビアスイッチクロスバ向け配線アルゴリズムの開発