### ACCEL 研究開発課題「縦型 BC-MOSFET による三次元集積工学と応用展開」 追跡評価報告書

#### 1. 研究成果の発展状況や活用状況

本研究開発課題は、飛躍的な高集積化と省エネ性を同時に実現する縦型ボディーチャネル (BC-) MOSFET が持つ特長を活かし、大容量、高速、低消費電力のワーキングメモリーなどへの応用展開、また産業界に適用できるレベルであることを実証することを目的とした。研究期間中、DRAM 回路においては、従来技術に比べて消費電力の約半減とチップサイズの削減を実証し、また 300mm ウェハの試作で実用のメモリテスト仕様を満たすテストチップを完成させた。STT-MRAM への応用ではメモリアクセス時間の短縮、リーク電流の削減や小面積化、低消費電力化なども実証した。ロジック回路への応用展開では、SRAM や I/O バッファを例にレイアウト面積や消費電力を劇的に改善できることを示した。

研究終了後、現在 3nmCMOS 世代以降で主流になっている縦型 Gate-All-Around (GAA) 型 MOSFET のプロセスやデバイス構造の検討も進め、断面が円形である 10nm 以下(当時としては世界最小サイズ)の Si ナノピラーの形成に成功した。MRAM 技術は AI (人工知能) コンピューティング分野へと発展されている。また、クロスポイント型不揮発性シナプスアレイ回路と新しいスパイキング学習ニューロン体回路を中核とする不揮発性ニューロモーフィックコプロセッサの開発なども引き続き研究を進めている。

後継プロジェクトとしては、内閣府の戦略的イノベーション創造プログラム (SIP)、JST の産学共創プラットフォーム共同研究推進プログラム (OPERA)、また文部科学省の次世代 X-nics 半導体創生拠点形成事業、NEDO のポスト 5G 情報通信システム基盤強化研究開発事業等や JAXA 事業で研究成果の発展と展開が進められている。研究終了後の知的財産権の権利化については、国内 22 件、海外 20 件の出願があり、特許登録は国内 5 件、海外 7 件となっている。研究成果の社会実装を目指すために設立したパワースピン株式会社 (2018 年)では、スピントロニクス融合技術やライセンスのメーカーへの提供、設計などを請け負って事業を進めている。

以上により、研究成果の発展状況や活用状況は十分であると評価する。

#### 2. 研究成果から生み出された科学技術や社会・経済への波及効果

研究終了後、研究成果の科学技術や社会・経済への波及例としては、以下が挙げられる。 スピントロニクス/CMOS Hybrid LSIを活用し、検出人数を従来の5~20人/秒から40~170人/秒へと向上させた「非接触多人数対応 AI 検温カメラ」をアイリスオーヤマ株式会社 とともに開発し、2023年5月のG7科学技術大臣会議で検温カメラとしてデモンストレーションを行った。また、日本電信電話株式会社(NTT)などが国際連携によって開発する光電融合データセンターのプロジェクト「IOWN(アイオン)」に参画し、NTTとキオクシア株式会社が手掛ける「光電融合」に対応した高速不揮発性メモリーの開発をはじめている。

日米両国でのより強固で高度な技術を持つ半導体人材の育成と研究開発のため、G7 広島サミットで米国国立科学財団(NSF)、米国のマイクロン・テクノロジー、及び東京エレクトロン株式会社に加え、東北大学を含む日米の 11 大学がメンバーとして参画する「U.S.-Japan University Partnership for Workforce Advancement and Research & Development in Semiconductors(UPWARDS) for the Future: 半導体でより良い未来を実現する人材育成と研究開発を加速するための日米産学パートナーシップ」が署名され、この事業の中でも日米の技術分野での競争力と強靭性を向上させる一歩を踏み出している。

以上により、科学技術や社会・経済への波及効果は非常に大きいと評価できる。

現在、2nm 以下の次世代ロジック半導体の製造技術の研究開発が国内外で進み始めているが、本研究開発課題の成果が今後の半導体分野の研究開発へ波及していくものと期待する。

以上

# 戦略的創造研究推進事業 ACCEL 追跡評価用資料

# 研究開発課題 「縦型 BC-MOSFET による三次元集積 工学と応用展開」 2014 年 4 月~2019 年 3 月

研究代表者:遠藤 哲郎

2025年3月

## 目次

| 要 | 匕<br>日                                                                                                                                                                                                                                        | . 1                                                       |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| 研 | 究開発課題の展開状況および波及効果(まとめ図)                                                                                                                                                                                                                       | . 2                                                       |

| 笋 | 1 章 研究開発課題の概要                                                                                                                                                                                                                                 | . 3                                                       |

|   | 1.1 研究開発概要                                                                                                                                                                                                                                    | . 3                                                       |

|   | 1.2 研究開発期間                                                                                                                                                                                                                                    | . 4                                                       |

|   | 1.3 研究体制                                                                                                                                                                                                                                      | . 4                                                       |

|   | 1.4 研究開発課題の研究成果                                                                                                                                                                                                                               | . 4                                                       |

|   | 1.4.1 概要                                                                                                                                                                                                                                      | . 4                                                       |

|   | 1.4.2 社会実装/実用化に向けた取組について                                                                                                                                                                                                                      | . 5                                                       |

| 笋 | 2 章 研究開発課題終了から現在に至る状況                                                                                                                                                                                                                         | . 7                                                       |

|   | 2.1 調査の方法                                                                                                                                                                                                                                     | . 7                                                       |

|   | 2.1.1 基礎データ調査の方法                                                                                                                                                                                                                              | . 7                                                       |

|   | 2.1.2 インタビュー調査の方法                                                                                                                                                                                                                             | . 8                                                       |

|   | 2.2 研究開発課題終了後の研究成果の状況                                                                                                                                                                                                                         | . 8                                                       |

|   | 2.2.1 DRAM (周辺回路:縦型 BC-MOSFET+メモリセル:FinFET)                                                                                                                                                                                                   | . 8                                                       |

|   | 2.2.2 STT-MRAM (クロスポイント MTJ 技術:平坦化技術+RIE 加工技術)                                                                                                                                                                                                | . 9                                                       |

|   |                                                                                                                                                                                                                                               |                                                           |

|   | 2. 2. 3 ロジック LSI への応用展開                                                                                                                                                                                                                       |                                                           |

|   | 2 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7                                                                                                                                                                                                       | . 9                                                       |

|   | 2.2.3 ロジック LSI への応用展開                                                                                                                                                                                                                         | . 9                                                       |

|   | 2.2.3 ロジック LSI への応用展開                                                                                                                                                                                                                         | . 9<br>10<br>20                                           |

|   | 2.2.3 ロジック LSI への応用展開.         2.2.4 後継プロジェクトへの発展状況について.         2.2.5 ベンチャーへの展開.                                                                                                                                                             | . 9<br>10<br>20<br>22                                     |

|   | <ol> <li>2.2.3 ロジック LSI への応用展開.</li> <li>2.2.4 後継プロジェクトへの発展状況について.</li> <li>2.2.5 ベンチャーへの展開.</li> <li>2.2.6 Si ウェハ基板技術の産業界への展開.</li> </ol>                                                                                                    | . 9<br>10<br>20<br>22<br>22                               |

| 第 | 2.2.3 ロジック LSI への応用展開.2.2.4 後継プロジェクトへの発展状況について.2.2.5 ベンチャーへの展開.2.2.6 Si ウェハ基板技術の産業界への展開.2.3 知的財産権等の権利化状況.                                                                                                                                     | . 9<br>10<br>20<br>22<br>22<br>22                         |

| 第 | 2.2.3 ロジック LSI への応用展開.2.2.4 後継プロジェクトへの発展状況について.2.2.5 ベンチャーへの展開.2.2.6 Si ウェハ基板技術の産業界への展開.2.3 知的財産権等の権利化状況.2.4 その他.                                                                                                                             | . 9 10 20 22 22 22 23                                     |

| 第 | 2.2.3 ロジック LSI への応用展開.<br>2.2.4 後継プロジェクトへの発展状況について.<br>2.2.5 ベンチャーへの展開.<br>2.2.6 Si ウェハ基板技術の産業界への展開.<br>2.3 知的財産権等の権利化状況.<br>2.4 その他.<br>3 章 研究開発課題成果の波及と展望.                                                                                  | . 9<br>10<br>20<br>22<br>22<br>22<br>23<br>23             |

| 笄 | 2.2.3 ロジック LSI への応用展開.<br>2.2.4 後継プロジェクトへの発展状況について.<br>2.2.5 ベンチャーへの展開.<br>2.2.6 Si ウェハ基板技術の産業界への展開.<br>2.3 知的財産権等の権利化状況.<br>2.4 その他.<br>3 章 研究開発課題成果の波及と展望.<br>3.1 半導体技術への波及と展望.                                                             | . 9<br>10<br>20<br>22<br>22<br>22<br>23<br>23<br>23       |

| 第 | 2.2.3 ロジック LSI への応用展開.<br>2.2.4 後継プロジェクトへの発展状況について.<br>2.2.5 ベンチャーへの展開.<br>2.2.6 Si ウェハ基板技術の産業界への展開.<br>2.3 知的財産権等の権利化状況.<br>2.4 その他.<br>3 章 研究開発課題成果の波及と展望.<br>3.1 半導体技術への波及と展望.<br>3.1.1 半導体技術動向.                                           | . 9<br>10<br>20<br>22<br>22<br>22<br>23<br>23<br>23<br>25 |

| 第 | 2.2.3 ロジック LSI への応用展開.<br>2.2.4 後継プロジェクトへの発展状況について.<br>2.2.5 ベンチャーへの展開.<br>2.2.6 Si ウェハ基板技術の産業界への展開.<br>2.3 知的財産権等の権利化状況.<br>2.4 その他.<br>3 章 研究開発課題成果の波及と展望.<br>3.1 半導体技術への波及と展望.<br>3.1.1 半導体技術動向.<br>3.1.2 国内の半導体分野における政策.                  | . 9<br>10<br>20<br>22<br>22<br>23<br>23<br>23<br>25<br>28 |

| 第 | 2.2.3 ロジック LSI への応用展開. 2.2.4 後継プロジェクトへの発展状況について. 2.2.5 ベンチャーへの展開. 2.2.6 Si ウェハ基板技術の産業界への展開. 2.3 知的財産権等の権利化状況. 2.4 その他. 3 章 研究開発課題成果の波及と展望. 3.1 半導体技術への波及と展望. 3.1.1 半導体技術動向. 3.1.2 国内の半導体分野における政策. 3.1.3 半導体分野の国際共同研究.                         | . 9 10 20 22 22 23 23 23 25 28 29                         |

| 第 | 2.2.3 ロジック LSI への応用展開. 2.2.4 後継プロジェクトへの発展状況について. 2.2.5 ベンチャーへの展開. 2.2.6 Si ウェハ基板技術の産業界への展開. 2.3 知的財産権等の権利化状況. 2.4 その他. 3 章 研究開発課題成果の波及と展望. 3.1 半導体技術への波及と展望. 3.1.1 半導体技術動向. 3.1.2 国内の半導体分野における政策. 3.1.3 半導体分野の国際共同研究. 3.1.4 半導体技術への波及のまとめと展望. | . 9 10 20 22 22 23 23 23 25 28 29                         |

| 第 | 2.2.3 ロジック LSI への応用展開. 2.2.4 後継プロジェクトへの発展状況について. 2.2.5 ベンチャーへの展開. 2.3 知的財産権等の権利化状況. 2.4 その他. 3 章 研究開発課題成果の波及と展望. 3.1 半導体技術への波及と展望. 3.1.1 半導体技術動向. 3.1.2 国内の半導体分野における政策. 3.1.3 半導体分野の国際共同研究. 3.1.4 半導体技術への波及のまとめと展望. 3.2 科学技術・社会経済への波及と展望.     | . 9 10 20 22 22 23 23 23 25 28 29 29 30                   |

#### 要旨

本資料は、国立研究開発法人科学技術振興機構(JST)戦略的創造研究推進事業 ACCEL の研究開発課題「縦型 BC-MOSFET による三次元集積工学と応用展開」(2014年4月~2019年3月、以後、本研究開発課題と記載)において、研究終了後一定期間を経過した後、副次的効果を含めて研究成果の発展状況や活用状況を明らかにし、事業および事業運営の改善などに資するために、追跡調査を実施した結果をまとめたものである。

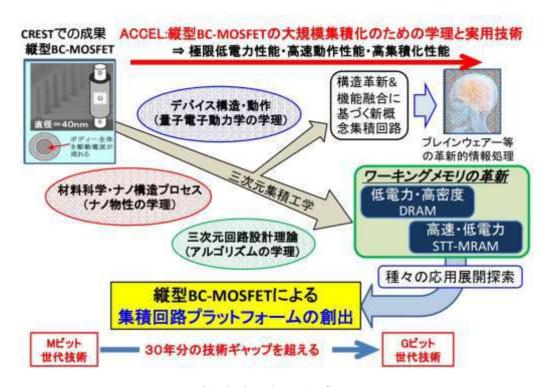

本研究開発課題は、飛躍的な高集積化と省エネ性を同時に実現する縦型ボディーチャネル (BC-) MOSFET による新しい三次元集積回路とそれを実現する技術プラットフォームの創出、さらにメモリとロジックの融合、集積回路の三次元構造化を起点に、ブレインウェアなどの価値観を一新させる新規情報処理基盤の創出を目指した。

第1章では、本研究開発課題の概要、研究体制また研究終了時点での研究成果等をまとめた。電子機器に不可欠な DRAM を代表とするワーキングメモリの技術限界を突破すべく、DRAM 周辺回路への縦型 BC-MOSFET を導入する基盤技術、および縦型 BC-MOSFET によるスピントロニクスデバイスである STT-MRAM セルを形成する基盤技術を開発した。次に、このワーキングメモリの新規技術をコアとして、ロジック LSI を中心にアナログ LSI やパワーLSI などへの応用展開、さらに新概念集積回路として AI・脳型 LSI 等の探索を実施した。

第2章では、本研究開発課題終了後から現在に至る状況について、研究成果の状況、後継プロジェクトの状況、共同研究者の状況、産業等の権利化状況をまとめた。本研究開発課題終了後、DRAM は次世代半導体に向けてより微細な縦型構造形成プロセスや新規デバイス構造へ展開し、STT-MRAM や CMOS との融合技術は後継プロジェクトで AI、IoT 向けの低消費電力デバイスへと展開している。また、共同研究者が後継プロジェクトで、製造装置技術やウェハ技術を展開している状況、産業財産権等の権利化状況、期間中に創業したベンチャー企業への展開状況について述べた。

第3章では、本研究開発課題成果の波及と展望について半導体技術への波及と展望、科学技術・社会経済への波及と展望をまとめた。本研究開発課題の研究成果は、半導体技術分野で国内外の技術動向や政策の流れの中、2nm以下の次世代半導体デバイスの GAA (Gate-All-Around) 構造で横型 GAA の先の縦型 GAA 技術として波及していくとともに、スピントロニクスとの融合による超低消費電力化へ貢献し、IT 技術へ波及していくと予想される。また社会・経済的には、超低消費電力デバイスの特長を活かして、ベンチャー企業により IT 分野での社会実装へと波及している。AI、IoT、次世代通信事業分野における後継プロジェクトで成果展開されることで、本研究開発課題の成果は、低消費電力化のキー技術が不可欠である 2050 年カーボンニュートラル、Society 5.0 の実現に貢献している。

| 研究開発課題                                                                                                                                                                   | <b>⊘</b> .=l                       | アクラ                                                                                                                             | ・ィビティ/                       | アウト                                                                                  | アウ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | アウトカム (long-term) /<br>インパクト                                                         |                                                         |                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------------------------|

| のねらい                                                                                                                                                                     | インプット                              | プット                                                                                                                             |                              |                                                                                      | ~追跡調査時点                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                      | 今後予想される展開                                               | 事業化によって創生される<br>社会                                                       |

| 目的·目標                                                                                                                                                                    | 研究体制                               | 事業化                                                                                                                             | の基盤となる<br>的財産                | る主な知                                                                                 | 終了後を含む本プロジェクトの成果(要約) 青字:終了後                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                      | 社会実装が見込まれる分野・市場・技術等                                     | 科学技術的および<br>社会・経済的な波及効果                                                  |

| 研ね飛化同縦ヤM新積実ラ創リ合三起ン価せ理目 想 ①②③④に別い的省にボルFい路すフ、次点ウ値る基指 定 次A次字が開い的省にボルFい路すフ、少様構、アを規の。 場 代Iの代・IT 課 高ネ現ィBに次そ技一らク回造ブな一情創 : 半 通層 集性すーC-よ元れ術ムメの路化レの新報出 導 信圏の 積をるチ)る集をプのモ融のをイーさ処を 体 | 研究代表者:<br>遠字教授)<br>PM:<br>政岡徹(JST) | 成年<br>2018<br>2021<br>2021<br>2022<br>2023<br>研究E<br>**<br>**<br>**<br>**<br>**<br>**<br>**<br>**<br>**<br>**<br>**<br>**<br>** | 23<br>25<br>25<br>25<br>発表論文 | 832号<br>508号<br>517号<br>706号<br>295号<br>148号<br>22<br>20<br>5<br>7<br>Rew 展開<br>8(8) | 動作原理上の最小値でほぼ実現 ・世界最高の低ノイズ特性を有する総型 BC-MOSFET の開発に成功 ・Gbit 級大規模 DRAM を300mm ウェハで、低電圧動作実証に成功 ・3次元化で顕著となるSiミッシング現象の解明とその抑制技術を開発 ・10nm以下のナノピラー構造形成酸化プロセス ・垂直GAA(UVGAA)MOSFET  縦型BC-MOSFET/CSTT-MRAM技術: ・MTIと縦型 BC-MOSFET の接続部の平坦化・微細化プロセス技術を開発し、直上に MTJ を形成するSTT-MRAMを実証 ・300mm ウェハに128Mbit STT-MRAMを実証・300mm ウェハに128Mbit STT-MRAMを実証・300mm ウェハに128Mbit STT-MRAMを実証・300mm ウェハに128Mbit STT-MRAMを実証・300mm ウェハに128Mbit STT-MRAMを関係し、世界最高書き込み速度性能の実面MTJにおいて260°Cでデータ保持と1000万回以上の書き込み両性を達成・1.5nmMRAMへ向けた多層MTJ側壁損傷低減プロセス開発 ・1.5nmMRAMへ向けた多層MTJ側壁損傷低減プロセス開発 ・1.5nmMRAMへ向けた多層が1側壁損傷低減プロセス開発 ・1.5nmMRAMへ向けた多層が1側壁損傷低減プロセス開発 ・1.5nmMRAMへ向けた多層が1側壁損傷低減プロセス開発 ・1.5nmMRAMへ向けた多層が1側壁損傷低減プロセス開発 ・1.5nmMRAMへ向けた多層が1り下の回路開発に成ってアウト面積の解りまし、一口の開発に成功・新概念集積の路・不揮発性ニューロ等の回路開発に表し、高速化を開発に表し、高速化を開発に表し、高速化を開発に表し、高速化を開発に表し、高速化を開発に表し、高速化を開発に表し、高速化を開発に表し、高速化を開発を表し、高速化を開発を表し、高速化を開発を表し、高速化を開発を表し、高速化を開発を表し、高速に対して表し、表し、表し、表し、表し、表し、表し、表し、表し、表し、表し、表し、表し、表 | 果を活用し、IoT デバイスとが<br>フィジカル空間デジタ ル処理基<br>MOS Hybrid IoT デ バイス基盤!<br>FRA)世界の知を呼び込むI T・輸 | 技術の研究 開発(2018-2020)、JST 産学共創<br>送システム融合型 エレクトロニクス技術 の創出 | カーボンニュートラル2050<br>実の波術・・3次名・イルークでは、大型では、大型では、大型では、大型では、大型では、大型では、大型では、大型 |

#### 第 1 章 研究開発課題の概要1

本調査の対象である ACCEL 研究開発課題「縦型 BC-MOSFET による三次元集積工学と応用 展開」の概要を下記に示す。

#### 1.1 研究開発概要

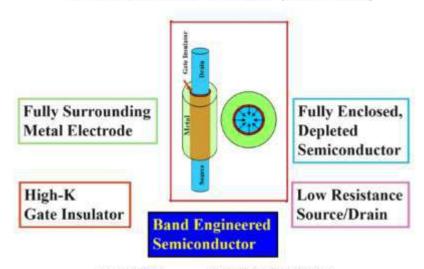

本研究開発課題は、飛躍的な高集積化と省エネ性を同時に実現する縦型ボディーチャネル (BC-) MOSFET<sup>2</sup>による新しい三次元集積回路とそれを実現する技術プラットフォームの創出であり、さらにメモリとロジックの融合、集積回路の三次元構造化を起点に、ブレインウェアなどの価値観を一新させる新規情報処理基盤の創出を目指した(図 1-1)。

図 1-1 新規概念の実証 (POC3) のスキーム

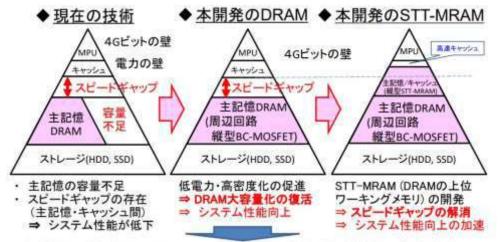

まず、電子機器に不可欠な DRAM を代表とするワーキングメモリの技術限界を突破すべく、 ①DRAM のメモリセル以外の周辺回路へ縦型 BC-MOSFET を導入する基盤技術、および②縦型 BC-MOSFET による STT-MRAM⁴セルを形成する基盤技術を開発する(図 1-2)。次に、このワー

<sup>&</sup>lt;sup>1</sup> https://www.jst.go.jp/kisoken/accel/evaluation/s-houkoku/JST\_1118710\_13527217\_PER.pdf

<sup>&</sup>lt;sup>2</sup> 縦型ボディーチャネル (BC-) MOSFET (Metal-Oxide-Semiconductor-Field-Efect-Transistor) は、直径数 10nm シリコン柱の周囲をゲート電極で取り囲み、その上下にソース・ドレイン電極を配置した構造のMOSFET (電界効果トランジスタ)。

<sup>&</sup>lt;sup>3</sup> POC:技術的成立性の証明 (Proof of Concept: POC)。なお POC 目標値は非公開。

<sup>&</sup>lt;sup>4</sup> スピン注入メモリ (Spin Transfer Torque Random Access Memory)。スピントロニクスを利用し、TMR(トンネル磁気抵抗)効果を動作原理とする不揮発性メモリ。

キングメモリの新規技術をコアとして、③ロジック LSI を中心に、アナログ LSI やパワー LSI などへの応用展開、さらに、新概念集積回路として AI・脳型 LSI 等の探索を実施する。

本開発の縦型BC-MOSFETによる飛躍的低電力性能・高速動作性能・高集積化性能を、MPUや低電圧ロジックLSI等へ波及させる

電子機器の高性能化・多機能化を促進

図 1-2 電子機器のメモリ階層と課題の克服

#### 1.2 研究開発期間

2014年4月~2019年3月

#### 1.3 研究体制

研究代表者 遠藤 哲郎 (東北大学国際集積エレクトロニクス研究開発センター・センター長)

プログラムマネージャー 政岡 徹 (JST・ACCEL プログラムマネージャー)

#### 1.4 研究開発課題の研究成果

#### 1.4.1 概要

主要な研究成果は以下の通りである。

#### (1) DRAM 周辺回路向け縦型 BC-MOSFET の基盤技術

低電力化の指標となる性能指数を MOSFET の動作原理上の最小値でほぼ実現できた。また、既存構造と比較して大幅なノイズ削減に成功し、世界最高の低ノイズ特性を有する縦型 BC-MOSFET の開発に成功した。さらに、メモリセル以外の周辺回路を縦型 BC-MOSFET で構成した Gbit 級大規模 DRAM を大口径 300mm ウェハにて試作することにより、電源電圧を従来

標準から大幅に低電圧化した場合の良好な動作実証に世界で初めて成功し、動作時消費電力の削減およびチップサイズの削減については、所定の性能を得て、当初設定の目標を達成し、また、実用のメモリテスト全仕様を満足するといった目標以上の大きな進展も得られた。加えて、Si ミッシング(縦型 BC-MOSFET を形成するナノメートルサイズの Si 柱が熱酸化時の Si 原子移動によって柱を維持できなくなる現象)のメカニズム解明では、理論と実験両面から 3 つの大学等との共同研究によるモデル化が進展し、その抑制プロセス技術開発に繋げた。また、界面原子制御のための計算科学およびナノ計測からのアプローチによって、将来のスケーリングに向けた知見が得られた。

#### (2) 縦型 BC-MOSFET に基づく STT-MRAM 技術

縦型 BC-MOSFET の STT-MRAM への応用においては、究極の面積縮小が図れるクロスポイント型メモリ構造化に向け、MTJ(磁気トンネル接合)5と縦型 BC-MOSFET の接続部の平坦化・微細化プロセス技術の開発によって、縦型 BC-MOSFET 直上に MTJ を形成することができる STT-MRAM の技術成立性を実証することができた。これにより、データアクセス時間の高速化および待機電力の削減については所定の性能を得て、当初設定の目標を達成した。加えて、この技術を使って大口径 300mm ウェハにて 128Mbit STT-MRAM を試作した結果、世界最高の書き込み速度性能の実証にも成功し、AI 応用等のハイエンドメモリで STT-MRAM 活用への道を拓くことができた。

#### (3) 縦型 BC-MOSFET の応用展開および新概念集積回路の探索

縦型 BC-MOSFET の応用展開として、ロジック LSI で重要な SRAM について、平面型 MOSFET と比べたレイアウト面積の縮小およびリーク電流の削減について、所定の性能を得ることができ、当初設定の目標を達成した。さらに、電源系アナログ回路用のレベルシフタ、パワー用の CMOS DC-DC コンバータ等、多岐にわたる回路開発にも成功した。新概念集積回路としては、不揮発性ニューロン回路および不揮発性連想メモリシステムの研究開発により、低電力・高密度・高速化にて、揮発性回路に比べ桁違いの極めて高い優位性を示すことができた。

#### 1.4.2 社会実装/実用化に向けた取組について

・当初半導体メーカーとの共同開発を行っていた DRAM<sup>6</sup>基盤技術において、縦型 BC-MOSFET の各種回路 TEG<sup>7</sup>群および規模実証チップを搭載した 300mm ウェハの 1 次試作の結果、Gbit 級 DRAM チップについて、従来標準から大幅低電圧化した電源電圧での動作、および JEDEC の全仕様を満足した動作電圧時の消費電力の大幅な低減により、開発の前倒しで POC の達成を確認した。DRAM 周辺回路はロジック回路の一部であり、縦型 BC-MOSFET のロジッ

<sup>&</sup>lt;sup>5</sup> 二つの強磁性体層の間に薄い絶縁体層で挟んだ構造。これに電圧を印加すると強磁性体層の磁化の向きによりトンネル磁気抵抗が変化する。この効果をMRAM(ランダム磁気メモリ)に利用している。

<sup>&</sup>lt;sup>6</sup> Dynamic Random Access Memory。情報を一時的に保持するために、定期的に情報の更新(リフレッシュ)が必要。

<sup>&</sup>lt;sup>7</sup> TEG:test elementary group。プロセスおよびデバイスの評価や管理を行うためのテストチップ。

ク応用展開という中間評価会での新たな要望もあり、DRAM の 2 次試作を取り止め、そのリソースをロジックデバイス開発に向ける判断を行った。

- ・STT-MRAM 基盤技術の研究開発の骨子は MTJ を搭載した集積化プロセスの開発であり、具体的には MTJ 直下の平坦化技術、MTJ の RIE 加工技術の開発により、世界最高レベルの狭ビッチ MTJ を実現することにある。そこで、縦型 BC-MOSFET による STT-MRAM の技術成立性を明らかにするために、性能実証用テストチップの1次試作を行い、データアクセス時間などの高性能化指標を達成した。この成果の波及効果は大きく、他プロジェクトの研究開発へ適用されている。

- ・ロジック LSI の課題は、混載メモリの大容量化によるチップ面積の増大と消費電力の増加である。縦型 BC-MOSFET をロジック LSI へ適用する場合、チップ面積の低減化と低消費電力化が期待できるため、SRAM®および I/O バッファ回路の面積縮小化と消費電力削減を新たに設定し、ロジック企業のヒアリングより数値目標を提示した。SRAM や I/O バッファ回路を含む TEG マスクの設計・試作検証の準備を進めると共に、技術の受け取り手となる企業の獲得を研究代表者と共に探索した結果、国内半導体メーカーの参画を得ることができた。当該半導体企業から東北大学への研究員の派遣と共同開発契約の締結を経て、縦型 BC-MOSFET のロジック開発の加速と体制の強化を進め、現在企業サイドの生産ラインでの試作開始を急いでいる。

- ・STT-MRAM による新規な不揮発性回路構造を用いた AI・脳型 LSI への応用展開を検討した 結果、不揮発性ニューロン回路、不揮発性連想メモリシステムの設計および試作を経て、 評価・解析を進めている。企業等との具体的な応用検討は、次のステップに向けて評価を 進めている。

- ・縦型 BC-MOSFET の微細化には、Si ピラーの形状が重要な鍵を握っているが、酸化工程中にピラーの形状が変わる Si ミッシングについて取組み、その原因解明と抑制プロセスの開発が行われた。また、実用化への取組みの前提として、知的財産権の取得に関してはプロジェクト開発当初から注力し、東北大学を中心に特許出願戦略や特許マップの策定、随時見直しやフォロー、さらに共同研究パートナーへの技術の特許化を促進してきた。その結果、縦型 BC-MOSFET の基本特許を始め、DRAM 基盤技術や STT-MRAM のプロセス加工技術など国内出願で 37 件、海外出願で 50 件の成果<sup>9</sup>が得られた。

6

<sup>8</sup> Static Random Access Memory。情報を保持するために外部のリフレッシュが不要で、DRAM より高速なアクセスが可能。

<sup>&</sup>lt;sup>9</sup> 特許件数は終了報告書による集計値 https://www.jst.go.jp/kisoken/accel/evaluation/s-houkoku/JST\_1118710\_13527217\_PER.pdf

#### 第 2 章 研究開発課題終了から現在に至る状況

#### 2.1 調査の方法

#### 2.1.1 基礎データ調査の方法

研究代表者(一部グループ内の成果も含む)を基本的に調査対象とした。利用したデータ ベースと調査範囲等を下記に示す。

#### (1) 論文

本研究開発課題期間中の論文は、2014 年~2019 年に発表された論文であり、終了報告書等に成果論文としてリストアップされている論文を収集した。終了報告書の成果論文リストの中で *in press、to be submitted*等と表記があり、その後発表されたものについても基本的には期間中の論文とした $^{10}$ 。以下、これらの論文を「成果論文(①とする)」と定義する。

本プロジェクト終了後の論文は、2019年1月以降に発表され、かつ研究代表者が著者になっている論文を収集し、発展論文(②とする)とし、リストにした。

データベースは、主としてエルゼビア社の Scopus を利用し、文献タイプは Book (Book chapter、Book review)、Editorial、Erratum を除く全文献タイプとした。

各論文についての評価の一つである FWCI (Field-Weighted Citation Impact) <sup>11</sup>、および Journal の指標となる CiteScore <sup>12</sup>についても収集した。

#### (2) 特許の出願・登録状況

本研究開発課題期間中の特許は、終了報告書等の成果リスト記載の特許とした。本研究開発課題終了後の特許は2019年4月以降に出願され、かつプロジェクトメンバーが発明者の特許を収集した。データベースは、主にPatent SQUARE を利用し、補助的に特許情報プラットフォームと Espacenet を利用し、国内外の登録状況などを確認した。

#### (3) 受賞

本研究開発課題期間中、終了後の受賞を調査対象者(主に研究代表者)の所属する研究室 や本人のWEB サイト、researchmap また Google 等の検索サイトで調査を行った。

#### (4) ベンチャー

<sup>10</sup> 終了報告書に記載の論文でも、2022 年、2023 年など最近の論文については、内容を精査した上で、インタビューで確認し、成果論文とするか、終了後の成果とするかを決定した。

<sup>&</sup>lt;sup>11</sup> FWCI (Field-Weighted Citation Impact): 1 文献あたりの被引用数を世界平均(年別・分野別・文献タイプ別に算出)で割った数値。

<sup>&</sup>lt;sup>12</sup> ジャーナル評価指標 (Web of Science の Impact Factor と同様の指標)。論文の出版年の CiteScore を 取得した。

インターネット検索やベンチャー情報の記載のあるデータベースを用いて検索し、研究 代表者に確認した。本研究開発課題との関係をインタビューで確認した。

#### 2.1.2 インタビュー調査の方法

インタビュー調査は研究代表者および、PM、研究開発課題に参加した企業等の主なメンバー数名に実施した。

#### 2.2 研究開発課題終了後の研究成果の状況

研究開発課題終了後の研究成果の展開状況と関連した後継プロジェクトへの展開状況、 またベンチャー企業や参画企業における展開状況について述べる。

#### 2.2.1 DRAM (周辺回路: 縦型 BC-MOSFET+メモリセル: FinFET)

本研究開発課題の研究成果を次世代半導体へと発展させるために、縦型 Gate-All-Around<sup>13</sup> (GAA) のプロセスやデバイス構造の検討も進められている。2021 年には、10nm 以下の Si ナノピラー構造を形成する酸化プロセスも提案 $^{14}$ している。2 重酸化により、断面が円形である 10nm 以下の Si ナノピラーの形成に成功した。

上述のナノピラー構造プロセスをベースに三次元デバイスへ展開させるために、究極の 縦型 GAA の新規な構造の提案<sup>15</sup> (図 2-1) も進めている。

この構造では、従来の GAA-MOSFET が直面していた非対称のソース/ドレイン構造による特性のばらつきや集積化の問題をほぼすべて解決する、対称なソース/ドレイン構造、ばらつきの低減、および高集積化を備えた究極の垂直 GAA (UVGAA) MOSFET を製造するための新しい方法を提案し、JST の支援を受けて 2021 年に PCT 出願した。ソースとドレインの同時製造が初めて可能になり、ソース/ドレイン構造が対称になるので UVGAA-MOSFET のばらつきが小さくなる可能性があり、さらに複数の MOSFET のゲートとソース/ドレインの垂直方向の同時製造も初めて実現できるので、高集積化、ばらつきの大幅な低減、高収率、高性能(高速、低エネルギー消費)、低コストが期待できる。また、この新規な UVGAA-MOSFET をベースにして、メモリセルやロジックデバイスを垂直方向に積層した三次元 (3D) 集積回路からなる新しいアーキテクチャも提案されている。

<sup>13</sup> 電流が流れるチャンネルの全周をゲート電極が覆う構造・縦型 BC-MOSFET は縦型 GAA に分類される。

<sup>14</sup> Ye S., Yamabe K., Endoh T., Journal of Physical Chemistry C, vol. 126, 16, 8853-886.1

Ye S., Yamabe K., Endoh T. July 2021Materials Science in Semiconductor Processing 134:106046 DOI:10.1016/j.mssp.2021.106046

図 2-1 垂直 GAA (UVGAA) MOSFET の形成方法<sup>16</sup>

(a) 簡略化された典型的な製造プロセス、(b) 典型的な構造、および (c) 1 つのナノピラーで垂直 方向に集積された 2 つの積層 UVGAA-MOSFET の平面図

#### 2.2.2 STT-MRAM (クロスポイント MTJ 技術: 平坦化技術+RIE 加工技術)

MRAM 技術は後述する後継プロジェクトで展開を進めており、AI (人工知能) コンピューティング分野へと発展されている。さらに文部科学省でも STT-MRAM で代表されるスピントロニクス技術をアカデミアの中でも拠点を作って先端技術開発を引き続き進めていくことが国の方針として示されている<sup>17</sup>。

#### 2.2.3 ロジック LSI への応用展開

新概念情報処理に関しては、縦型 BC-MOSFET による新しい不揮発性ロジックアーキテクチャを用いた認識処理 LSI 回路応用に向け、クロスポイント型不揮発性シナプスアレイ回路と新しいスパイキング学習ニューロン体回路を中核とする不揮発性ニューロモーフィックコプロセッサの開発なども引き続き進めていて、後述する後継プロジェクト中で展開している。

<sup>&</sup>lt;sup>16</sup> Ye S., Yamabe K., Endoh T., Mater Sci Semicond Process, 134 (2021) 106046. #fig4

$<sup>^{17}\</sup> https://www.meti.go.jp/policy/mono_info_service/joho/conference/semicon\_digital/0005/04.pdf$

#### 2.2.4 後継プロジェクトへの発展状況について

(1) 内閣府戦略的イノベーション創造プログラム(SIP)第2期SIP「フィジカル空間デジタル処理基盤研究サブテーマ II. 超低消費電力 IoT デバイス・革新的センサ技術 超低消費電力 MTJ/CMOS Hybrid IoT デバイス基盤技術の研究開発」(2018~2020)<sup>18</sup>

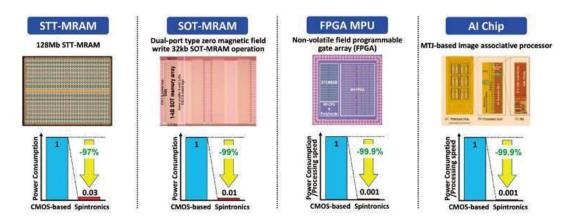

スピントロニクスを開拓した東北大学・教授 大野英男が内閣府革新的研究開発推進プログラム ImPACT で開発した MRAM 技術と、本研究開発課題で開発した MTJ 材料技術および CMOS 技術を発展させている(図 2-2)。トヨタ自動車株式会社、日本電気株式会社(NEC)が参画している。MTJ/CMOS Hybrid 技術により、IoT<sup>19</sup>デバイスに演算処理機能に加えて不揮発機能を持たせることで、課題である待機電力を大幅に削減し、従来の消費電力と演算処理性能のジレンマを解消することが可能となる。これにより、将来のフィジカル空間に求められる飛躍的な低消費電力性能(従来比:1/5~1/10)を有する IoT デバイスの基盤技術の確立を目指している。

図 2-2 SIP 第 2 期「超低消費電力 IoT デバイス・革新的センサ技術 超低消費電力 MTJ/CMOS Hybrid IoT デバイス基盤技術の研究開発」<sup>20</sup>

本プロジェクトの成果として、本研究開発課題の 300mm ウェハプロセスで培ったスパッタ技術、反応性イオンエッチング技術、損傷制御集積プロセス技術を用いて、33nm までの 4 重界面垂直磁気トンネル接合 (MTJ) (Quad-MTJ) を作製<sup>21</sup>している。従来の二重界面垂直 MTJ と比較して、2 倍の熱安定性係数や 10 年間の記憶保持を達成している。高い書き込み効率と低損傷の統合プロセス技術により、優れた耐久性 10<sup>11</sup>以上を達成した。

<sup>&</sup>lt;sup>18</sup> https://www.jst.go.jp/impact/sahashi/index.htm 内閣府革新的研究開発推進プログラム(ImPACT)「大野社会実装分科会 スピントロニクス集積回路プロジェクト」

<sup>&</sup>lt;sup>19</sup> IoT: Internet of Things。様々なモノ (物) がインターネットに接続され情報交換することにより相互 に制御する仕組み。

<sup>20</sup> http://www.cies.tohoku.ac.jp/program/sip.html

$<sup>^{21}</sup>$  S. Miura etal., IEEE J. Trans. Electron Devices, vol. 67  $\,$  (12) , pp. 5368-5373, Dec. 2020.

本成果論文の被引用数はTop1%であり、超低消費電力MTJ/CMOS Hybrid IoTデバイスの注目度が高いことがわかる。

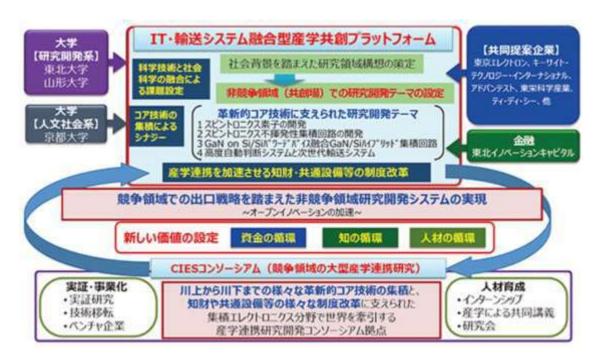

(2) JST 産学共創プラットフォーム共同研究推進プログラム(OPERA)「世界の知を呼び込む IT・輸送システム融合型エレクトロニクス技術の創出」(2016~2020)

最大 1.5 億円のプロジェクトで、東北大学と共に共同申請機関として東京エレクトロン 株式が MRAM 製造技術を担当している (図 2-3)。

図 2-3 世界の知を呼び込む IT・輸送システム融合型エレクトロニクス技術の創出 (IST OPERA) <sup>22</sup>

MRAM 製造技術の成果では、直径がわずか原子 10 個程度 (2.3nm) の世界最小高性能磁気トンネル接合素子を開発した<sup>23</sup>。車載応用可能な 150℃でも高いデータ保持特性(熱安定性)を維持しながら、DRAM 置き換えに必要となる 10 ナノ秒での高速低電圧動作を実現した。

また、磁気抵抗メモリで記憶を担う磁気トンネル接合素子の高速動作を特徴づけ、時定数を制御できる新構造を提案し、直径 5nm 以下の素子で 10 ナノ秒以下の高速書き込み動作を実証した<sup>24</sup>。これにより、オングストローム世代半導体製造技術での磁気抵抗メモリ基盤技術を確立した。

<sup>22</sup> http://www.cies.tohoku.ac.jp/opera/overview/

<sup>&</sup>lt;sup>23</sup> https://www.wpi-aimr.tohoku.ac.jp/jp/achievements/press/2020/20201208\_001354.html

$<sup>^{24}</sup>$  https://www.wpi-aimr.tohoku.ac.jp/jp/achievements/press/2021/20211214\_001455.html

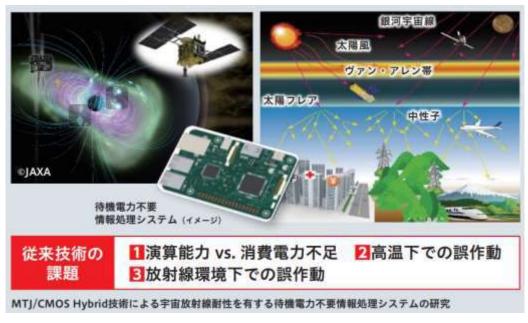

(3) 国立研究開発法人宇宙航空研究開発機構 (JAXA) 宇宙探査イノベーションハブ MTJ/CMOS Hybrid 技術による待機電力不要システム研究、およびその耐環境性試験 (宇宙用途向け) (2022~2023)

本プロジェクトは本研究開発課題の MRAM 製造技術が関連している<sup>25</sup>。宇宙探査においては、月、火星以遠の探索ではエネルギー源となる太陽光が微弱な環境下で 10 年以上の長期ミッションが想定されるため、既存技術ではなしえない超低消費電力の電子システム、また、宇宙機の電子システムには待機電力不要に加えて宇宙放射線耐性の両立が重要な課題となっている。本プロジェクトでは、スピントロニクス素子である MTJ と CMOS 技術が融合された MTJ/CMOS Hybrid 技術を用いて待機電力不要システムを研究し、飛躍的な演算効率向上と桁違いの低消費電力化を実現する革新的半導体デバイス・集積回路の実現を目指している(図 2-4)。

図 2-4 MTJ/CMOS Hybrid 技術による宇宙放射線耐性を有する 待機電力不要情報システム<sup>26</sup>

本プロジェクトの成果として、300mm ウェハプロセスラインを用いて高性能 MTJ デバイス技術、メモリセルアレイ回路設計技術により MTJ サイズ 50nm の MTJ/CMOS Hybrid 型半導体チップを試作した。作製したデバイスを JAXA が耐性効果を実測し、従来の 10 年@85℃から 1000 万年@150℃に耐性が向上することを明らかにした27。従来のはやぶさの SOI (Silicon on Insulator) 基板を用いたデバイスより 2 桁耐性が向上した。

<sup>&</sup>lt;sup>25</sup> http://www.cies.tohoku.ac.jp/program/jaxa.html

<sup>&</sup>lt;sup>26</sup> https://www.ihub-tansa.jaxa.jp/assets/prev/files/report\_2022/2022report\_5\_4\_3.pdf

$<sup>^{\</sup>rm 27}$  https://shuyukai-tohoku-u.net/wp/wp-content/uploads/2023/07/kanto2023endo.pdf p12.

(4) 国立研究開発法人新エネルギー産業技術開発機構 (NEDO) 研究開発課題発掘のための 先導調査研究 高効率・高速処理を可能とする AI チップ・次世代コンピューティングの技 術開発 CMOS/スピントロニクス融合技術を用いたコンピューティング技術 (2021~2022)

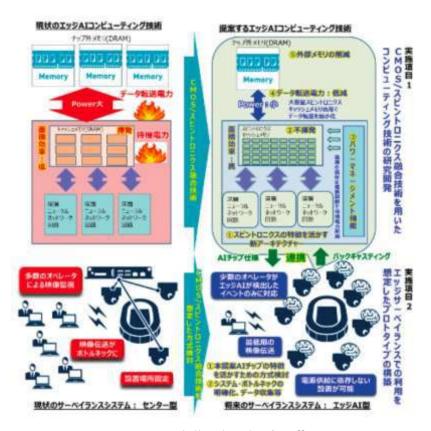

本プロジェクトは、本研究開発課題において、AI、脳型 LSI の方向性を示したこともとに エッジ AI に適した高い電力効率のコンピューティング技術と、その社会実装として見守り システムなどに利用する次世代サーベイランスシステムに関して先導調査研究を行っている (図 2-5)。

図 2-5 先導調査研究の概要28

本プロジェクトにおいて、AI 技術ではニューロモーフィックプロセッサ指向のハイブリッド乗算法を提案して低消費電力で低遅延のハイブリッド乗算モジュールを設計して、ニューロモーフィックプロセッサの開発を進めている<sup>29</sup>。

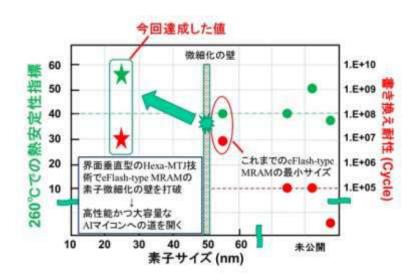

またデバイス技術では、6 重界面磁気トンネル接合素子 (i-PMA $^{30}$  Hexa-MTJ) を開発した。 MTJ 作製では、本研究開発課題で開発された MTJ 製造プロセス技術が活かされている。25nm の微細 MTJ において、260 $^{\circ}$ Cのはんだ付け工程中のデータ保持と 1000 万回以上の書き込み耐性を同時に達成した(図 2-6)。

<sup>&</sup>lt;sup>28</sup> http://www.cies.tohoku.ac.jp/program/national\_project/np\_03.html

<sup>&</sup>lt;sup>29</sup> https://link.springer.com/content/pdf/10.1007/s00521-023-08280-y.pdf

<sup>30</sup> 界面垂直磁気異方性 (i-PMA): Interfacial Perpendicular Magnetic Anisotropy

図 2-6 i-PMA Hexa-MTJ と従来の Double-MTJ との比較<sup>31</sup>

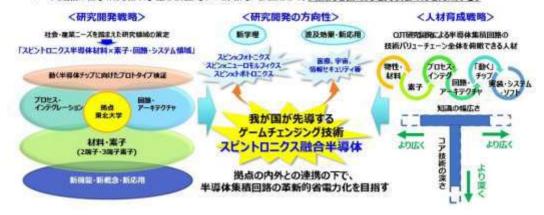

## (5) 文部科学省 次世代 X-nics 半導体創生拠点形成事業 スピントロニクス融合半導体創出拠点(2022~2031)

本プロジェクトは、2022年から 10年間の人材育成事業で、2035年~2040年頃の社会で求められる半導体(ロジック、メモリ、センサー等)の創生を目指したアカデミアの中核的な拠点を形成し、省エネ・高性能な半導体創生に向けた新たな切り口("X")による研究開発と将来の半導体産業を牽引する人材の育成の推進を目指している。東北大学の拠点では、本研究開発課題における組み合わせ・ハイブリッドの手法を活かして、スピントロニクスの先の材料技術、人材育成を行っている32。

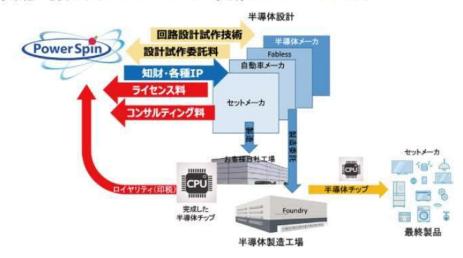

## (6) 東北経済産業局 戦略的基盤技術高度化支援事業 スピントロニクス/CMOS Hybrid LSIの設計技術およびソフトウェア開発と実用化(2020~)

本プロジェクトは経済産業省のサポイン事業(戦略的基盤技術高度化支援事業)であり、 本研究開発課題に関連して創業したパワースピン株式会社(パワースピン)が主体となって いる<sup>33</sup>。本研究開発課題のスピントロニクスにおける MRAM 製造技術が関連する。

パワースピンがハードウェアの開発、東北大学国際集積エレクトロニクス研究開発センター (CIES) がそのハードウェア開発につなげる基盤技術の提供と事業管理、ティアンドエス株式会社がソフトウェア開発を行い、3者が一体となって回路設計/システム設計/ソフトウェア実装効率の向上を実現する技術基盤の構築を進めている(図 2-7) <sup>34</sup>。

<sup>31</sup> http://www.tohoku.ac.jp/japanese/newimg/pressimg/tohokuuniv-press20221205\_01web\_iPMA.pdf 図 3:本研究と従来の研究との比較

<sup>32</sup> http://xnics.tohoku.ac.jp/

<sup>33</sup> http://www.cies.tohoku.ac.jp/img/program/national\_project/np\_05-1.png

<sup>34</sup> 特開 2023-074969

図 2-7 スピントロニクス/CMOS Hybrid LSI の設計技術およびソフトウェア開発と 実用化事業 $^{35}$

(7) NEDO 戦略的省エネルギー技術革新プログラム 実用化開発/アフターコロナ時代の 感染ハザードマップのための高速人物位置同定 AI マイコンを用いた非接触多人数対応 AI 検温カメラの開発(2020~)

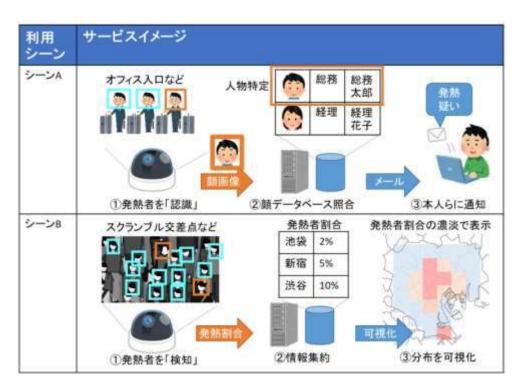

本プロジェクトでは、「非接触多人数対応 AI 検温カメラ」技術を本研究開発課題の成果であるスピントロニクス/CMOS Hybrid LSI を活用し開発を行っている(図 2-8)。助成事業者はパワースピンで東北大学が共同研究・委託先である。

$<sup>^{35}\ \</sup>mathrm{http://www.\,cies.\,tohoku.\,ac.\,jp/program/national\_project/np_05.\,html}$

図 2-8 検温カメラによる感染症対策サービスイメージ36

本プロジェクトの成果として、パワースピンが設計したスピントロニクスデバイスを搭載するサーマルカメラをアイリスオーヤマ株式会社と共同で研究開発した例があげられる 37。2023 年 5 月の広島 G7(主要国首脳会議)の科学技術大臣会議で検温カメラとしてデモンストレーションをしており、検出人数を従来の 5~20 人/秒から 40~170 人/秒へと向上させている。なお、40 人/秒は顔で個人認識して発熱者を検出する場合で、170 人/秒は発熱者のみの検出である。イベント等で来場者の登録情報を認識しての発熱検出や、会社で社員の発熱者管理に活用が期待されている(図 2-9)スピントロニクスの導入により低消費電力となるので、デバイスからの発熱が無視できるため電子機器を密閉した筐体に入れることができるという特長がある。

$https://www.nikkei.com/nkd/industry/article/?DisplayType=1\&n\_m\_code=062\&ng=DGXZQOCC25B220V21C22A0000000$

$<sup>^{36}~\</sup>mathrm{https://www.nedo.go.jp/content/100927667.pdf}$

図 2-9 高速・低消費電力 AI 検温カメラ技術と高速検温イメージ38

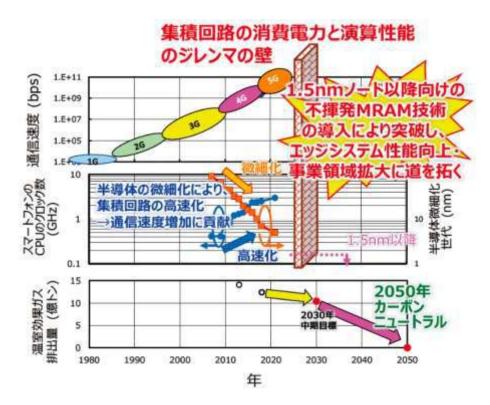

(8) NEDO ポスト 5G 情報通信システム基盤強化研究開発事業 先導研究(助成)/半導体プロセス 1.5nm ノード以降の不揮発性 MRAM の微細加工基盤技術の研究開発(2021~2023)

本プロジェクトは本研究開発課題の発展として重要なプロジェクトである。東京エレクトロン(TEL)が代表で、TELが 1.5nm ノード以降に向けた MTJ ピッチでの RIE エッチング 基盤技術の開発を担当、東北大学国際集積エレクトロニクス研究開発センター(CIES)は共同研究者としてその微細加工基盤技術検証につなげる集積プロセスの開発・試作・評価を担当し、半導体プロセス 1.5nm ノード以降に向けた不揮発性 MRAM の微細加工基盤技術の構築を目指している(図 2-10)。

<sup>38</sup> http://www.cies.tohoku.ac.jp/program/national\_project/np\_04.html

図 2-10 低消費電力化により消費電力と演算性能のジレンマの解決39

本プロジェクトでは、MTJ 形成プロセスで課題となる 4 重界面垂直磁気トンネル接合 (Quad-MTJ) の熱安定性係数におよぼす側壁損傷の影響を、マイクロマグネティックシミュレーションによって調べている<sup>40</sup>。Quad-MTJ などの多層 i-PMA は、材料や MTJ のパターニングプロセスを変えることなく、側壁損傷の影響を制御することで、MRAM の X-nm 世代の候補となることを示した。

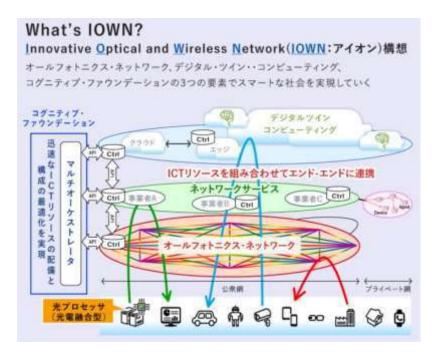

#### (9) NTT Φ IOWN Global Forum

日本電信電話株式会社(NTT)が進めている IOWN(アイオン: Innovative Optical and Wireless Network)では、革新的な技術によりこれまでのインフラの限界を超え、あらゆる情報をもとに個と全体との最適化を図り、多様性を受容できる豊かな社会を創るため、光を中心とした革新的技術を活用した高速大容量通信、膨大な計算リソースなどを提供可能なコミュニケーションインフラの構想を進めている(図 2-11)。ここで課題となっているのが、光信号を高速で受け取るための、NAND デバイスの 10 万倍速いデバイス開発である<sup>41</sup>。

本プロジェクトは日米の連携事業として進められている。CPUでは米国のインテル(Intel Corporation)、DRAMでは米国のマイクロン・テクノロジー (Micron Technology)、ストレイジでは日本のキオクシア株式会社など日米の主要企業が参画している。NTT は、2023 年 6

<sup>&</sup>lt;sup>39</sup> http://www.cies.tohoku.ac.jp/program/national\_project/np\_02.html

<sup>&</sup>lt;sup>40</sup> H. Nagase et al., AIP Advances 12, 125317 (2022) .

<sup>41</sup> https://www.tohoku.ac.jp/japanese/2021/08/news20210826-03.html

月に光電融合のデバイスを製造する NTT イノベーティブデバイス株式会社を設立した<sup>42</sup>。ここで製造する光電融合デバイスから出力される高速な信号に追従して受け取ることができる超高速デバイス開発を東北大学が担当する。

2023年現在、デバイスの規格作りをしている段階である。

図 2-11 IOWN 構想の構成イメージ<sup>43</sup>

#### (10) CIES コンソーシアム

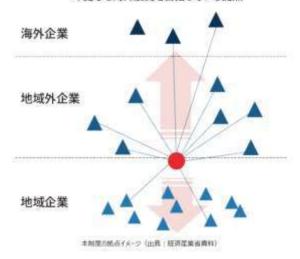

以上の後継プロジェクトは、本研究開発課題代表者の遠藤がセンター長である東北大学国際集積エレクトロニクス研究開発センター(CIES)が中心となって推進している。CIESでは、上記プロジェクトの他にも産学共同研究を推進しており、本コンソーシアムでスピントロニクス、AI ハードウェア、パワーエレクトロニクスにおいて企業との共同研究を推進している<sup>44</sup>。2021年にCIESは、経済産業省のJ-Innovation HUB 地域オープンイノベーション拠点選抜制度で、海外・国内グローバル企業との産学連携活動を積極的に行い、今後の更なる海外展開を目指している拠点として国際展開型に指定された。

CIES コンソーシアムでは上述の後継プロジェクトの他、様々な国家プロジェクト、地域連携プロジェクト、産学共同研究が推進されている<sup>45</sup>。産学共同研究では、スピントロニクス分野ではLSI技術(図 2-12)を中心に、STT/SOT<sup>46</sup>-MRAM&スピン素子/CMOS Hybrid プロセ

<sup>42</sup> https://group.ntt/jp/newsrelease/2023/06/12/230612c.html

<sup>43</sup> https://www.rd.ntt/iown/0002.html

<sup>44</sup> http://www.cies.tohoku.ac.jp/program/

<sup>45</sup> http://www.cies.tohoku.ac.jp/program/

<sup>&</sup>lt;sup>46</sup> SOT: スピン軌道トルク。

ッサの研究等が進められ、スピン軌道トルク型磁気トンネル接合(SOT-MTJ)素子を用いた 不揮発メモリ(SOT-MRAM)チップの試作・実証に初めて成功している<sup>47</sup>。

図 2-12 スピントロニクスをベースにした LSI 技術

#### 2.2.5 ベンチャーへの展開

研究代表者の遠藤は、PM の政岡と、CIES の研究成果の社会実装を目指すために 2018 年 10 月にパワースピン株式会社(パワースピン)を創業した<sup>48</sup>。スピントロニクス技術に加え、パワースピン独自技術により、演算性能/消費電力比を従来より高めた IoT デバイスと AI システムを中心に事業を展開している。パワースピンの具体的な事業内容は以下の通りである。

- ・スピントロニクス/CMOS Hybrid 技術による STT-MRAM などの磁気メモリ、IoT デバイスや AI チップ等の各種ロジック LSI とそのモジュールの設計事業

- ・スピントロニクス技術による磁気メモリ、IoT デバイスや AI チップなどのスピントロニクス/CMOS Hybrid LSI の試作事業

- ・スピントロニクス/CMOS Hybrid 技術にかかる知財・各種回路 IP・PDK の販売・ライセンシング事業

- ・ 当該事業領域でのコンサルティングサービス事業からなる 4 つの事業の中核事業

#### 会社の経営体制:

発足時(2018年) 代表取締役社長 政岡徹

取締役 CTO 遠藤哲郎 取締役 COO 福田悦生

2023 年現在 代表取締役社長 CEO 福田悦生

代表取締役 CTO 遠藤哲郎

取締役 政岡徹

47 https://www.tohoku.ac.jp/japanese/newimg/pressimg/tohokuuniv-press20200615\_01web\_SOT-MRAM.pdf

<sup>&</sup>lt;sup>48</sup> https://www.tohoku.ac.jp/japanese/newimg/pressimg/tohokuuniv-press20190701\_02\_power.pdf

パワースピンは、半導体を製造するメーカーになるのではなく、東北大学で生み出されたスピントロニクス融合技術やライセンスの製造メーカーへの提供、設計などを請け負う会社を目指している。パワースピンは極めて優れた低消費電力を特徴とするスピントロニクス/CMOS Hybrid 技術を中心とし、英国のアーム(Arm)社49と同様のビジネスモデル(図 2-13)を展開している。

弊社保有の革新的技術群にて、お客様に省電力半導体開発サービスをご提供すると共に、 事業化に必要となるライセンスサービス等を行うビジネスモデルです。

図 2-13 パワースピンのビジネスモデル50

パワースピンにおける最近の社会実装につながる発展事例として、前述のサーマルカメラの開発例があげられる。

2022 年には、スピントロニクス融合技術を中心とした省電力の半導体設計事業で横浜に拠点<sup>51</sup>を設けた。さらに 2023 年 11 月には、回路設計の人材等の強化に 25 億円の資金を調達<sup>52</sup>している。

<sup>49</sup> https://www.arm.com/ja/

<sup>&</sup>lt;sup>50</sup> https://mic.tohoku.ac.jp/resident/powerspin.html

<sup>&</sup>lt;sup>51</sup> https://www.nikkei.com/article/DGXZQOCC177NZ0X10C22A1000000/

<sup>52</sup> https://powerspin.co.jp/news/231114\_funding\_news/

#### 2.2.6 Si ウェハ基板技術の産業界への展開

本研究開発課題でSi ミッシング現象解明とその抑制プロセスの技術開発が行われた。終了後、参加企業において、ロジック半導体への展開を進め、デバイス製造企業のウェハ購入コストを、従来のエピタキシャルウェハに比べて削減することが可能になった。

終了後も参加企業は、参画した 2 つ大学と後継プロジェクトの SIP で協力して基板技術を展開している。なお、東北大学とは、共同研究に移行して引き続き技術開発を進めている。

#### 2.3 知的財産権等の権利化状況

知的財産権等の権利化は期間中に政岡 PM が戦略的に出願のマップを作り、特に DRAM の周辺回路の特許、STT-MRAM を積層する特許を多く出願している。期間中の特許は、国内 25件、海外 25件出願し、国内は 25件すべてが登録され、海外は先端半導体分野が強い米国、台湾、韓国で 23件が登録されている。本研究開発課題終了後は、国内 22件、海外は 20件出願していて、登録された特許は国内 5件、海外 7件となっている。

東北大学 CIES の特許部が有している特許には、スピントロニクスのメインである STT-MRAM 技術の他に CREST・ACCEL の縦型 MOSFET 技術、パワーMOSFET (GaN on Si) の特許もある。特に STT-MRAM は基本特許から押さえている。パワースピンは、これら東北大学の特許ライセンスを持ち、その数は東北大学のライセンシングを含めて 350 件ほどである。一方で、大学の特許をそのまま社会実装することは困難であり、パワースピンでは東北大学で権利化されたデバイスの回路設計技術、周辺回路設計を主に業務として行っており、顧客の製品本体にデバイスを使うための設計の橋渡しも行っている。単なる設計受託ではなく、特許で権利が保護されているセーフティゾーンの技術を提供できることが強みとなっている。今後、縦型 MOSFET と他のデバイスを組み合わせたデバイスに本研究開発課題の特許が使用されると予想している。

Si ウェハについては本研究開発課題に参画した企業では重要特許が 2 件ある。一つは、 Si ピラー構造と酸化時における  $Si/Si0_2$  界面の粗さに関する特許で終了後に登録された。 もう一つは、本研究開発課題終了後に東北大学との共同出願で、ウェハの極表層の酸素濃度 に特長を持たせた Si ウェハとその製造方法に関するものである。この特許も登録され、海 外は 1 カ国(台湾)が登録され、2 カ国が 2023 年現在審査中である。

#### 2.4 その他

遠藤は 2023 年 12 月に米国電気電子学会 IEEE (The Institute of Electrical and Electronics Engineers) より、「不揮発性メモリーとスピントロニクスロジックに関する貢献」でフェローの称号が授与53された。

<sup>&</sup>lt;sup>53</sup> http://www.cies.tohoku.ac.jp/news/article.html?news\_id=515

#### 第 3 章 研究開発課題成果の波及と展望

#### 3.1 半導体技術への波及と展望

#### 3.1.1 半導体技術動向

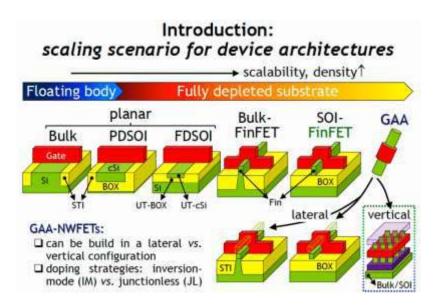

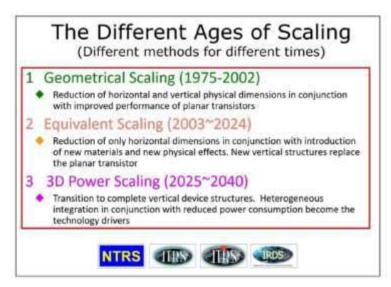

最先端半導体デバイスの動向としては、IRDS (International Roadmap for Devices and Systems) で示されているように 2022 年以降より、ロジック半導体は FinFET から横型 GAA が使われるようになっている。図 3-1 に、MOSFET における GAA への展開の流れを示した。GAA には、横型 (lateral) GAA と縦型 (vertical) GAA の二つがある。

横型 GAA には、ナノシート GAA などの構造が海外の半導体企業<sup>54,55</sup>より開発されている。 国内では、ラピダス株式会社(Rapidus)が 2022 年に創立し、IMB のナノシート GAA を 2nm ノードのロジック半導体として 2027 年に量産するロードマップで開発を進めている<sup>56</sup>。こ のように、2nm ノードからそれ以下の次世代半導体デバイスでは横型 GAA の時代となってき ている。これに対して、高密度化に優位性のある本研究開発課題の縦型 BC-MOSFET は、この 縦型 GAA に分類される。

Figure ES56 Practical migration of transistor structure from FinFET to GAA to fully vertical

図 3-1 MOSFET 構造における GAA への展開のシナリオ<sup>57</sup>

https://news.samsung.com/global/samsung-begins-chip-production-using-3nm-process-technology-with-gaa-architecture

$<sup>^{54}~\</sup>mathrm{https://www.eetimes.com/ibm-unveils-worlds-first-2-nm-chip/}$

https://www.rapidus.inc/wp/wp-content/uploads/2023/01/Strategic-Partnership-between-IBM-and-Rapidus\_V4a-LSTC%EF%BC%88%E5%85%AC%E8%A1%A8%E7%89%88%EF%BC%89.pdf

$<sup>^{57}</sup>$  https://irds.ieee.org/images/files/pdf/2022/2022IRDS\_ES.pdf  $\,$  p 70  $\,$

縦型 GAA はモアムーア $^{58}$ の技術とされており、ゲート長のスケールダウンが限界になると横型 GAA から縦型 GAA へ進むといわれている $^{59}$ 。図 3-2 は、2025 年~2040 年における理想的な三次元 MOSFET を示す図である。この三次元構造化では、縦型 GAA のような縦型デバイス構造への移行と異種素子との集積で低消費電力化が加速されるとしている(図 3-3)。

### The Ideal 3D MOS Transistor (2025~2040)

Figure ES54 The id

The ideal 3D transistor

図 3-2 理想的な三次元 MOSFET<sup>60</sup>

本研究開発課題では、異種素子である STT-MRAM を縦型 BC-MOSFET へ積層する低消費電力 デバイスを実証してきた。このスピントロニクスを融合したデバイス構造も、図 3-3 の異種 素子との集積による低消費電力化の方向に合致したものであり、縦型 GAA 技術と併せて新たな次世代半導体デバイス技術へと波及していくと予想される。

60 https://irds.ieee.org/images/files/pdf/2022/2022IRDS\_ES.pdf p69

<sup>58</sup> モアムーア (More Moore):新材料や三次元構造を採用して、ムーアの法則をさらに進展させる技術。

<sup>&</sup>lt;sup>59</sup> https://irds.ieee.org/images/files/pdf/2022/2022IRDS\_ES.pdf p48

図 3-3 三次元へのスケーリングの時代変遷<sup>61</sup>

#### 3.1.2 国内の半導体分野における政策

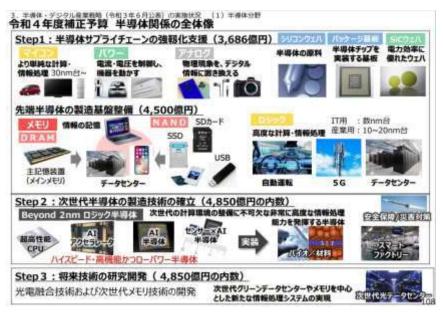

国内の半導体政策の動きとして、2021年6月に経済産業省は半導体・デジタル産業戦略62 を策定し、2022 年 12 月には次世代半導体の製造技術の確立に向けて 2nm 以下のロジック半 導体への支援を強化している(図3-4)。

図 3-4 2022 (令和 4) 年度補正予算 半導体関係の全体像63

<sup>61</sup> https://irds.ieee.org/images/files/pdf/2022/2022IRDS\_ES.pdf p69 下図

<sup>62</sup> https://www.meti.go.jp/press/2021/06/20210604008/20210603008-1.pdf

<sup>&</sup>lt;sup>63</sup> https://www.meti.go.jp/press/2023/06/20230606003/20230606003-1.pdf 半導体・デジタル産業戦略 p108.

2022年12月には、半導体・デジタル産業戦略に基づいた国内の半導体産業界の動きとして、次世代半導体の量産技術の実現に向けた研究開発拠点「技術研究組合最先端半導体技術センター(Leading-edge Semiconductor Technology Center (LSTC))」 <sup>64</sup>が設立された。 LSTC は、産業ニーズを基に 2nm 世代以降の次世代半導体の設計・製造に必要となる研究開発テーマを策定し、国内外の企業・研究機関と連携し、次世代半導体に資する研究開発を行う。また、次世代半導体の設計・製造基盤を担うプロフェッショナル・グローバル人材の育成を目指すとともに、次世代半導体が需要になる新産業の創出を目指している。 LSTC では、企業として前述の Rapidus が参画し、アカデミアでは東北大学も参画している。 LSTC のロードマップでは、先端 GAA 製造技術のロードマップが検討されている(図 3-5)。

####

188

図 3-5 LSTC ロードマップ<sup>65</sup>

2023 年 6 月には半導体・デジタル産業戦略の改定として、2nm 以下のロジック半導体開発に加えて光電融合等ゲームチェンジとなる将来技術の開発、革新メモリ、混載メモリの開発があげられている<sup>66</sup>。経済産業省は、最先端半導体のデバイス構造が Fin 型から GAA 型へと大きく変わり、今後の量産に向けて高度な生産技術が必要となる転換期と捉え、10 年前にFinFET の量産に至らなかった日本が改めて次世代半導体に参入するラストチャンスと捉え

6

<sup>64</sup> https://www.lstc.jp/

<sup>65</sup> https://www.meti.go.jp/policy/mono\_info\_service/joho/post5g/230425.pdf p3 次世代半導体プロジェクトのアップデート、令和5年4月、経済産業省

<sup>66</sup> https://www8.cao.go.jp/cstp////gaiyo/yusikisha/20230622/siryo2\_1.pdf p11.

ている<sup>67</sup>。また 2023 年 10 月には、LSTC に参画している国立研究開発法人産業技術総合研究 所が先端半導体研究センター(SFRC)を設立した<sup>68</sup>。ここでは GAA 構造を含む三次元デバイスを作製できる共用パイロットラインを運営すると発表されている。このように、国内産業界でも GAA の開発が加速される機運が出てきている。

これらの政策で示された 2nm 以下のロジック半導体など次世代の計算環境の整備に不可 欠な非常に高度な情報処理能力を発揮する次世代半導体の製造技術、光電融合技術および 次世代メモリ技術などは、本研究開発課題に関連するデバイス技術の方向性に一致してい る。これらへの支援が強化されることで、本研究開発課題の成果が将来の半導体分野におけ る研究開発へ波及していくと期待される。

一方、図 3-6 のように半導体集積回路分野のアカデミアに対する支援強化<sup>69</sup>が文部科学省より示されている。この政策により、前述の後継プロジェクトの次世代 X-nics 半導体創生拠点形成事業「スピントロニクス融合半導体創出拠点」の採択につながっている。この拠点では、革新的な集積回路のイメージを将来ニーズも見据えながら設定し、学術にとどまらない研究開発目標とその実現に向けた戦略策定を進めている。ここでは、スピントロニクス、ニューロモーフィックス、フォトニクス、トポロジー等の新しい切り口による、従来比 1/100倍の低電力を実現する半導体や AI やロボット等の特定用途を志向した半導体等の将来ビジョンを設定していく。この拠点では、人材育成を担っているが、この波及については 3.2.2 で述べる。

このように国内の半導体分野の産業界やアカデミアに関する政策の方向性は、本研究開発課題で示してきた開発技術の流れに沿っており、これら政策面でも波及効果がでていることがうかがえる。この流れは、次で述べる国際連携へもつながっている。

<sup>67</sup>

https://www.meti.go.jp/policy/mono\_info\_service/joho/conference/semiconductors\_and\_digital.pdf p157

<sup>68</sup> https://www.aist.go.jp/aist\_j/news/pr20231001.html

<sup>69</sup> https://www.tia-nano.jp/data/doc/1635309171\_doc\_66\_0.pdf

#### 半導体集積回路分野のアカデミアに対する支援強化に向けて 世界の半導体市場 ○ 半導体集積回路は全ての産業の根幹であり、今後のカーボンニュートラル2050の実現や デジタル社会を支える重要基盤。 S ×EU ○ 米国・欧州・中国等を筆頭とした諸外国では、自国技術開発、自国内での生産能力・基盤 の確保が至上命題となり、国際競争が激化。 方で、微細加工の技術競争が限界を迎えつつあり、主役が交代するゲームチェンジの可能性。 日本が蓄積してきた新旧の技術・知見を糾合し、 新しい原理や材料を活用した全く新しい次世代の半導体創生に向けた研究開発 ・将来の半導体産業を担う専門人材の育成 お部上がりで成高する中で の取組を強化することが、日本がこの分野で逆転シナリオを描くチャンス。 本事業では、アカデミアにおいて2035~2040年頃の社会で求められる"次世代"の半導体創生に向け、新しい原理、 アーキテクチャや新しい材料、素子を活用することにより挑戦する研究開発と将来の半導体分野を担う人材を育成する 拠点形成を推進。 【次世代X-nics半導体創生拠点形成事業】R4新規要求:9億円 支援期間:10年間 ・ロシック、メモリ、センサー等の集積回路の分野において、全く新しい次 世代半導体の創生に向け、オールジャバンのアカデミアの知見等を集約 する中核的な拠点形成を推進。 経済産業省 文部科学省 【例】エレクトロニクスの光やスピン等への置き換えや脳型アーキテクチャ 計・原理等により、従来比1/100倍の消費電力を実現する半導体等 キテクチャ等の新たな回路設・産業政策、経済安全保障政策の 界水準の研究環境を提供する 両面の観点を踏まえた総合戦略の 産業界にも関かれた影点の整備 次々世代半導体創生に向けた 基礎・基盤的研究関発の推進や 策定, 第行 材料開発、設計、試作までの一貫した研究開発体制を構築し、プロト NEDOによるファンディングや タイプの製作等を通じ、次世代を担う専門人材を育成。 産総研における研究開発の接進 人材育成の活性化 産業界の動員 等 国研、大学等の勧員 等 経産省等との間で連携を図りながら、産学官による協調領域から競争 領域への効果的な研究展開、産業界にも関かれた拠点形成を推進。 両者により \*X-nics=スピントロニクス、ニューロモルフィクス、フォトニクス、トボトロニクス等

図 3-6 半導体集積回路分野のアカデミア支援強化

#### 3.1.3 半導体分野の国際共同研究

国際共同研究については、CIES と関連のあるグローバル企業、大学との連携実績から、東北大学は前述の J-Innovation HUB 地域オープンイノベーション拠点の国際展開型<sup>70</sup>(図 3-7)に選抜されており、グローバル展開が進んでいる。さらに経済産業省、文部科学省から海外展開の活動が評価されて日米間連携へ東北大学が参画することになり、国際共同研究の強化へとつながっている。

<sup>70</sup> http://www.cies.tohoku.ac.jp/program/j-innovation\_hub.html

#### 国際展開型

特定の拠点において、海外・国内グローバル企 業等との産学連携活動を積極的に行い、今後 の更なる海外展開を目指している拠点

図 3-7 J-Innovation HUB 地域オープンイノベーション拠点(国際展開型)

さらに、2023 年 5 月に広島 G7 にあわせて教育分野での連携強化を確認する覚書が交わされ、今後米国の企業が日米の大学に、量子科学や半導体などの最先端技術の分野で合わせて 2 億ドル以上の投資を行うことが発表されている  $^{71}$ 。この日米大学間パートナーシップ UPWARDS  $^{72}$ の中で、半導体大手の米国マイクロン・テクノロジーは、半導体の研究開発のため、日米の 11 の大学に、今後 5 年間で 6,000 万ドルを拠出する。東北大学もこの支援を受けることになっている  $^{73}$ 。

このように、本研究開発課題の成果による国際連携への波及効果がうかがえる。

#### 3.1.4 半導体技術への波及のまとめと展望

本研究開発課題の成果である縦型 BC-MOSFET は半導体技術動向において、2nm 以下の次世代半導体デバイスの GAA 構造で横型 GAA の先の技術として 2035 年~2040 年頃に求められる次世代半導体創出へ波及していくと期待される。さらに、2023 年から日米間連携で最先端半導体での協力が加速される流れとなっている。また、半導体集積回路分野へのアカデミアへの人材支援強化にもつながっている。

#### 3.2 科学技術・社会経済への波及と展望

$<sup>^{71}\ \</sup>mathrm{https://jp.}$ usembassy.gov/ja/us-japan-launch-landmark-education-partnerships-ja

<sup>&</sup>lt;sup>72</sup> UPWARDS: U.S.-Japan University Partnership for Workforce Advancement and Research & Development in Semiconductors

<sup>&</sup>lt;sup>73</sup> https://www.tohoku.ac.jp/japanese/2023/05/news20230522-upwards.html

#### 3.2.1 IT 分野への波及

次世代の AI・ビッグデータの時代を支えるコンピューティングでは、データ量の膨大化 によるプロセッサなどのデバイスにおける消費電力の急激な増大の課題解決"4だけでなく、 様々な用途における環境で要求される IT 技術を支える高信頼性デバイスの開発が不可欠に なっている。

本研究開発課題終了後の成果である 25nm の i-PMA Hexa-MTJ は 1 桁 nm 世代 (Xnm 世代) の最先端半導体ロジックのデザインルールに適合する。これにより Double-MTJ では困難だ った Xnm 世代の最先端半導体集積回路と大容量 STT-MRAM を融合したアプリケーションプロ セッサーの実現が期待できる。これにより応用領域が、画像処理や AI システムなどのハイ エンドから IoT やセンサーネットワークシステムなどローエンドにまで広がり、低消費電 力・高性能化が進むと期待され、エッジデバイスのプロセッサやマイコンの低消費電力・高 性能化へ波及していくと予想される。加えて、熱安定性や高い書き換え性能など高い信頼性 性能を活用して自動車や産業用ロボットなどの耐環境応用へ波及していくと予想される。

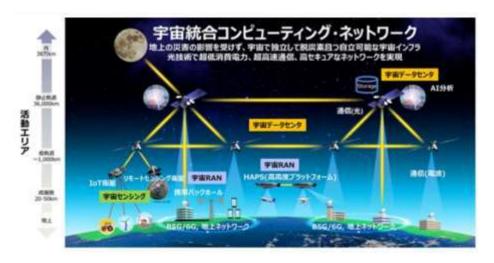

また、IT 分野で STT-MRAM 技術が期待される例として、総務省の事業として NTT が進めて いる成層圏でもポスト 5G に使われる次世代の新たな通信インフラとして成層圏 (上空約 20km) を飛行する高高度プラットフォーム (High Altitude Platform Station、HAPS) があ げられる<sup>75</sup> (図 3-8)。今まで地上で使われていた AI・IT の技術を宇宙空間へと展開するた めには、低消費電力だけでは対応できず、宇宙放射線耐性が必要である。STT-MRAM は、ス ピンの向きで動作するのでシリコンデバイスのように成層圏での宇宙放射線により発生す る電子ホール対に起因する電荷反転によるソフトエラーがないという特長がある76。さらに、 縦型 BC-MOSFET における三次元 Si ピラー構造は、宇宙放射線が通過する領域が極めて微小 で宇宙放射線との相互作用が小さく照射ダメージがほとんどないという効果が期待できる。

JAXA の後継プロジェクトでの宇宙放射線耐性に関する成果が注目され、株式会社 NTT ド コモ、ソフトバンク株式会社、エアバス (Airbus) 社も HAPS の検討を進めている。

<sup>&</sup>lt;sup>74</sup> https://www.jsme.or.jp/kaisi/1240-21/ デジタル社会を支える ICT システムとその省エネ化の動向

<sup>&</sup>lt;sup>75</sup> https://www.soumu.go.jp/main\_content/000692246.pdf <sup>76</sup> Watanabe K., Shimada T., Hirose K., Shindo H., Kobayashi D., Tanigawa T., Ikeda S., Shinada T., Koike H., Endoh T., Makino T., Ohshima T., IEEE International Reliability Physics Symposium Proceedings, 2022-March, P541-545.

図 3-8 衛星・HAPS による宇宙統合コンピューティング・ネットワーク構想"

#### 3.2.2 社会経済への波及

#### (1) カーボンニュートラル・Society 5.0 への貢献

2050 年カーボンニュートラルの実現は、エネルギー・産業部門の構造転換、大胆な投資によるイノベーションの創出といった取組を、大きく加速することが必要で、経済産業省が中心となり、「2050 年カーボンニュートラルに伴うグリーン成長戦略」を策定している<sup>78</sup>。半導体・情報通信産業分野では、次世代パワー半導体(従来の Si に加え、GaN や SiC といった次世代パワー半導体の研究開発)、グリーンデータセンター(光エレクトロニクス技術など技術開発等を通じて、データセンターを省エネ化)、エッジコンピューティング<sup>79</sup>(センサなどエッジ側のデータ処理技術を開発、情報通信インフラを省エネ化)の取組が始まっている<sup>80</sup>。特にデータセンターや情報通信インフラでは省エネ化が重要な課題となっている。本研究開発課題で開発した、デバイスの消費電力を 2~3 桁に低減する最先端の GAA の技術とスピントロニクスの融合技術は、カーボンニュートラルにおいて新しいゲームチェンジ技術となることが期待される。

またスマートフォンや IoT・AI プロセッサ等のエッジ側システムのポスト 5G 時代の低遅延性の実現のためには、電力供給制限環境下での高度なエッジコンピューティングを行う必要がある。しかしながら、従来のシリコン技術の延長線上での 1.5nm ノード以降の技術開発では継続して消費電力と演算性能のジレンマが課題となり、エッジシステムの性能向上

<sup>&</sup>lt;sup>77</sup> https://group.ntt/jp/newsrelease/2022/01/17/220117a.html

<sup>&</sup>lt;sup>78</sup> https://www.meti.go.jp/policy/energy\_environment/global\_warming/ggs/index.html 2050 年カーボンニュートラルに伴うグリーン成長戦略

<sup>&</sup>lt;sup>79</sup> エッジコンピューティングは、利用者や端末と物理的に近い場所に処理装置(エッジプラットフォーム) を分散配置して、ネットワークの端点でデータ処理を行う技術の総称。

<sup>&</sup>lt;sup>80</sup> https://www.meti.go.jp/policy/energy\_environment/global\_warming/ggs/06\_handotai.html 半導体・情報通信産業

や事業領域拡大に制限が生じている。開発した MRAM/CMOS 混載 LSI 技術により消費電力と 演算性能のジレンマを解決し、低消費電力性と低遅延性を有するエッジ側システムを社会 実装することで 2050 年カーボンニュートラルへの貢献につながる。

一方で、内閣府で策定した Society  $5.0^{81}$ では、フィジカル空間のセンサからの膨大な情報がサイバー空間に集積され、サイバー空間ではこのビッグデータを AI 解析し、その解析結果がフィジカル空間の人間に様々な形でフィードバックされる $^{82}$ 。これを実現するには要求されるビッグデータを扱う情報通信インフラの低消費電力化が必要となり、Society 5.0 においても貢献が期待される $^{83}$ (図 3-9)。

図 3-9 超低消費電力 MTJ/CMOS Hybrid IoT デバイス基盤技術の研究開発概要84

#### (2) 人材育成への貢献

東北大学は前述の文部科学省次世代 X-nics 半導体創生拠点形成事業で「スピントロニクス融合半導体創出拠点」<sup>85</sup>(図 3-10)がスタートしており、社会経済へ貢献する半導体技術を担う人材を育成している。今後、半導体・エレクトロニクスの市場のゲームチェンジの原動力となる省電力化へ貢献していくことが期待される。

84 https://www.nedo.go.jp/content/100942902.pdf p35

<sup>&</sup>lt;sup>81</sup> 狩猟社会 (Society 1.0)、農耕社会 (Society 2.0)、工業社会 (Society 3.0)、情報社会 (Society 4.0) に続く、新しい社会。サイバー空間 (仮想空間) とフィジカル空間 (現実空間) を高度に融合することで社会的な課題を解決するとされる、日本の「第5期科学技術基本計画」で提唱された。

<sup>82</sup> https://www8.cao.go.jp/cstp/society5\_0/index.html

<sup>83</sup> https://www.nedo.go.jp/content/100942902.pdf

$<sup>^{85}\ \</sup>text{https://www.tohoku.ac.jp/japanese/newimg/pressimg/tohokuuniv-press20220422\_01web\_x-nics.pd}$

#### 東北大学「スピントロニクス融合半導体創出拠点」(拠点長:遠藤哲郎)

#### 拠点構想の概要

- 我が国が先導してきた集積回路の省電力化のゲームチェンジ技術であるスピントロニクスを中核に弱え、新材料・素子の研究開発とその特性を引き出す回路・アーキテクチャ・集積化技術の研究開発を推進し、CMOS半導体の発展を加速させる動く省電力半導体チップに向けたプロトタイプ検証までを、連携・協力機関と共に総合的に展開する。

- スピントロニクス融合半導体研究の展開の中で、光・ニューロ・トボロジーとエレクトロニクスの融合領域や、医療・宇宙・情報セキュリティ等の新応用を開拓して新学理と情報社会の変革までを先導し、我が国の半導体に係る研究開発力の向上に寄与する。

- 本拠点に若手研究者や学生も積極的かつ戦略的に参画させて、実践力と俯瞰力を持った人材を育成する。

図 3-10 スピントロニクス融合半導体創出拠点86

#### (3) ベンチャー企業による社会経済への波及

東北大学 CIES とパワースピンは連携して本研究開発課題で開発した成果の社会経済への 貢献を推進している。

開発した縦型 BC-MOSFET は、従来の平面構造では PN 接合が平面的に広がり電源電圧を印加するだけでリーク電流が流れるのに対し縦型 MOSFET ではリーク電流をなくすことが可能、さらにセル面積を小さくでき、省エネ効果とコスト効果が非常に大きい。さらに、前述のSTT-MRAM と同様に宇宙放射線耐性の特長を持つ可能性も予想される。

先述の通り、ロジックではセル面積が半分、待機パワーが 1/10~1/100 となり省エネルギーデバイスとして応用範囲が広がることが期待される。身近な例として、ウェアラブルウォッチで充電間隔を1週間、スマートフォンや PC でも充電が1週間は持つようになると予想している。また、検温カメラなど社会実装へつながっている。

このように IT 分野における省エネルギーデバイスとして今後広く波及していくと予想される。

#### (4) Si ウェハ基板技術の産業界への波及

本研究開発課題で開発された Si ウェハ基板技術は、ロジック半導体デバイスの製造コスト削減となる。ロジックデバイス半導体デバイスへの展開をねらいに、国内の市場から開発した Si ウェハの導入を図り、社会実装を目指している。

. .

$<sup>^{86}</sup>$  https://www.tohoku.ac.jp/japanese/2022/04/press2020422-01.html  $\,$

また、酸化プロセス制御の概念は、直近の FinFET 製造プロセスでも効果が期待でき、今後半導体企業へ浸透していくことが予想される。

#### 3.2.3 科学技術・社会経済への波及のまとめと展望

本研究開発課題の三次元構造の GAA とスピントロニクスの融合技術は、低消費電力である強みがあり、カーボンニュートラルへ波及している。IT 分野でもメタバース、エッジコンピューティングなどでもキーデバイスの低消費電力化が必須であり、本研究開発課題の成果が Society 5.0 にも波及しており、カーボンニュートラルと両立しながら発展していくと予想される。これらの基盤技術は、後継プロジェクトやベンチャー企業により社会実装へ向けて発展を続けている。

これら日本発のキー技術が、その特長を活かして今後も科学技術・社会経済へ波及していくと期待される。

以上