プログラム名:無充電で長期間使用できる究極のエコ IT 機器の実現

PM 名: 佐橋 政司

プロジェクト名:スピン FET プロジェクト

# 委託研究開発 実施状況報告書(成果) 平成28年度

# 研究開発課題名:

磁性・非磁性体用デュアルゲート設計・作製

研究開発機関名:

国立研究開発法人産業技術総合研究所

研究開発責任者

遠藤 和彦

# I 当該年度における計画と成果

## 1. 当該年度の担当研究開発課題の目標と計画

本プロジェクトで開発に取り組むスピン FET は以下の動作原理を有する: (1) 強磁性ソース/ドレイン電極により半導体チャネルへスピン情報を有する電流を流し、それを検出する (2) 磁性体および非磁性体から成るデュアルゲート構造を有する。この内、非磁性ゲートにより FET の特長である高いオン・オフ比が確保され、磁性ゲートによりオン電流の不揮発的な変調効果が見込まれる。

当該年度は、昨年度に引き続き、上記のデュアルゲート構造の設計および作製を行う。まずはシングルゲート構造からの試作を行う。同時に、磁性ゲートを用いた電界効果の実証実験を行うために、半導体チャネルと Fe/MgO トンネル接合から構成される非局所測定用素子を作製する。スピン偏極電子の注入・検出を検証し、シリコンチャネルを流れるスピン偏極電流の制御を試みる。

### 2. 当該年度の担当研究開発課題の進捗状況と成果

### 2-1 進捗状況

# ・非局所測定素子の試作

非局所測定用素子作製プロセスを更に改良し、歩留まりよく非局所測定用素子が作製できるプロセスを確立した。

インプラ保護酸化 グロバールマーク形成 Pイオン注入 • 活性化アニール JL-FETsのチャネル部分以外のEBリソ インプラ保護膜エッチング ゲート部分のSOI薄膜化 保護膜酸化 メサのEB描画もしくはフォトリソ メサ加工 酸化膜除去 ゲート酸化 TiNスパッタ Poly-Si成膜 ハードマスクSiO2成膜 ゲートEBリソ

ハードマスク加工 レジスト除去

Polv-Si加工

TiN加工

- p-Si 100 nm

BOX

SiO,

n\*Si

BOX

Si SiO,

n\*Si

BOX

Si Sub.

SiO,

n\*Si

BOX

Si Sub.

BOX

Si Sub.

SiO,

n\*Si

BOX

Si Sub.

- TEOS-SiO<sub>2</sub>成膜(350°C)

グローバルマーク形成

TEOS-SiO<sub>2</sub>成膜(350°C)

Fin EBリソ

Fin加工

High-k絶縁膜成膜

50nm TiN形成

TEOS-SiO<sub>2</sub>成膜(350°C)

ゲート EBリソ

ゲート加工

High-k Stack膜除去

層間絶縁膜形成

活性化アニール

(400°C or 500°C, N<sub>2</sub>, 1min)

配線工程

図1 ジャンクションレス・トランジスタ作製フロー

図 2 ゲルマニウムトランジスタ フロー

・ジャンクションレス・トランジスタ試作 本年度より、トランジスタの作製に着手した。チャネル濃度 1E19cm<sup>3</sup> 程度のドーピング濃度で動作し、磁性ゲートのインテグレーションに適するジャンクションレ ス・トランジスタ構造を設計し、シリコン SOI 基板を用いた試作プロセスフローの構築を行い、試作を終了した。

### ゲルマニウムトランジスタ試作

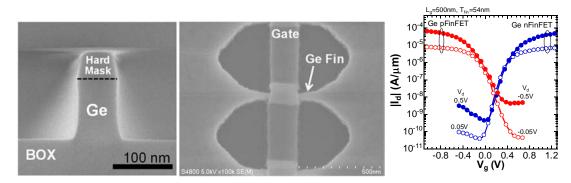

シリコンよりも高い移動度を持ち、より効率的にスピン注入が行える基板として、ゲルマニウム基板が大きく注目されている。特に、絶縁膜上にゲルマニウム薄膜が積層される GeOI (Ge on Insulator) 構造は、スピントランジスタとして適した構造を持つ。しかしながら、これまでゲルマニウムトランジスタの作製プロセスが確立しておらず、スピントランジスタとしての実現を阻んでいた。そこで、ゲルマニウムを用いたスピン MOSFET を実現するために、GeOI 基板を用いたゲルマニウムトランジスタの試作に新規に着手した。Fin 型ダブルゲート構造を持つトランジスタの設計、プロセスフローの構築および試作を試みた。

### 2-2 成果

非局所測定用素子をスピントロニクスセンターに供給し、スピントロニクスセンターにて、スピン偏極電子の注入実験サンプルとして活用され、スピン偏極電子の注入にも成功した。ジャンクションレス・トランジスタは、数ボルト程度の印加電圧でゲートが ON となるので、今後の磁性ゲートによる電界効果検証への活用が見込まれる。ゲルマニウムトランジスタに関しては、加工ダメージに非常に敏感であり、過去のシリコンプロセスを全て見直して、ダメージレスの作製プロセスを構築した。特にゲルマニウム

(a) Fin 構造断面 (b) Fin 型デュアルゲートトランジスタ (c) ドレイン電流-ゲート電圧特性 図 3 ゲルマニウムトランジス試作結果

のフィン構造の作製に新しいエッチング手法を適用したところ、ダメージによる劣化なく加工が可能となり、nMOS、PMOS ともにオン電流の大幅な改善が見られることが分かり、スピン注入に適したトランジスタプロセスの構築が完了した。今後磁性ゲートを付与し、スピントランジスタとしての動作が期待される。

### 2-3 新たな課題など

ゲルマニウムトランジスタへの磁性ゲート付与に関しては、実施期間中に完了せず、今度の課題となった。

3. アウトリーチ活動報告 該当なし