プログラム名:「無充電で長期間使用できる究極のエコ IT 機器の実現」

PM 名: 佐橋 政司

プロジェクト名:電圧駆動 MRAM 開発タスクフォース

# 委託研究開発 <u>実施状況報告書(成果)</u> <u>平成28年度</u>

研究開発課題名:

電圧駆動 MRAM のための回路設計

研究開発機関名:

株式会社東芝 研究開発センター

研究開発責任者

藤田 忍

# I 当該年度における計画と成果

#### 1. 当該年度の担当研究開発課題の目標と計画

# 目標

項目1: 高速型電圧駆動 MRAM の回路設計

高速 Write・Read のために第一次設計した回路において、エラーレート〈1x10<sup>-10</sup>を達成する。

項目2: 大容量型電圧駆動 MRAM の回路設計

高速 Write・Read のために第一次設計した回路において、エラーレート<1x10<sup>-10</sup>を達成する。

#### 計画

### ➡ 項目1:高速型電圧駆動 MRAM の回路設計

高速型電圧駆動 MRAM を実現するためには、書き込み回路と読み出し回路の高速性とエラー率の低減を同時に達成する必要がある。このためには、(i)集積回路における書き込みエラー率 (WER) の低減、および(ii) 読み出しの高速化(同時に ER の低減)の 2 点が特に重要となる。(i)については、たとえ単一 MTJ 素子において WER<10-10 が実現できても、集積回路中では高速の書き込み電圧パルスがバラつくことによる WER の増大が懸念される。このため、集積回路中に書き込み電圧パルスを制御する回路を設計し、書き込み回路の原理改良等により、WER<10-10 が実現できる新型回路を設計する必要がある。(i)については、書き込みの前にまず読み出しを行って、素子の状態("0"または"1")を確認してからパルス幅を調整する必要がある。さらに、必要に応じてベリファイ(書き込んだ後にエラーの有無を確認するために読み出しを行い、書き込みエラーがあった場合は再度書き込みを行う動作)も行う必要がある。この方式実現のための回路設計も行う。(ii)とベリファイ動作のため、高抵抗 MTJ 素子専用の新たな読み出し回路の開発が必要となる。電圧駆動 MRAM MTJ 素子の素子抵抗は STT-MRAM 用 MTJ 素子に比べて約 10~100 倍高いため、通常の読み出し回路では読み出し時間が約 10~100 倍長くなってしまい高速性が実現できないためである。当該年度では、まずこれらの書き込み、読み出し回路の第一次設計を行う。目標とするメモリアクセス時間は、読み出し書き込みともに概ね 10ns 以下である。なお、性能の検証は、半導体製品開発に使われる高精度の回路シミュレータを用いて行う。

#### ➡ 項目2:大容量型電圧駆動 MRAM の回路設計

大容量型電圧駆動 MRAM を実現するために、メモリ回路面積の最小化と、エラー率低減が重要となる。このためには(i)課題2で開発される複数ビットー括書き込み方式用の書き込み回路、(ii)高抵抗 MTJ 素子の読み出しを実現するための読み出し回路を設計する。(i)は課題2で開発される MTJ 素子実験データと MTJ アレイプロセス情報をベースに設計する。(ii)は、項目1の開発手法をある程度共用しながら設計する。目標とするメモリアクセス時間は、読み出し書き込みともに概ね40ns以下である。当該年度では、これらの書き込み、読み出し回路の第一次設計を行う。この場合も、性能の検証は、半導体製品開発に使われる高精度の回路シミュレータを用いて行う。

#### 2. 当該年度の担当研究開発課題の進捗状況と成果

#### 2-1 進捗状況

# ➡ 項目1: 高速型電圧駆動 MRAM の回路設計

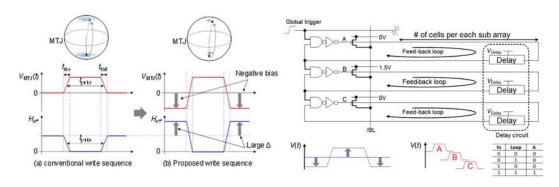

書き込みの問題を解決するために、書き込み前と書き込み後の両方に、書き込みと逆極性の電圧をかける回路(Verify-Sandwiched-Write 回路)を開発した。前後を逆極性にするとスピン回転の止まり易さが増して、エラー率が数桁のオーダーで改善できることに着目した技術である(図 1)。ここではデータを書き込む前にMTJのデータを読んで、書き込む必要が無い場合には書き込みをスキップするという方式を使う(書き込み前の Verify)。これによって、無駄な書き込みエラーが抑えられる。また、書き込み後に再度読み出し、エラーが発生していたら再度書き込むことで、さらに書き込みエラーが低減できる(書き込み後の Verify)。この Verify-Sandwiched-Write 回路で、書き込み前後の Verify+書き込みと逆極性の電圧の効果で、二重の書き込みエラー低減が実現できる。

ただし、これで低減できるのはメモリセル内部のエラーのみである。メモリ容量が大きなものになると、配線を伝送する書き込み電圧パルスが鈍ってしまい、それが読み出しエラーを再度損ねてしまう。本研究ではデバイス特性の実験データからの予測で 350fJ/Vm 程度の VCMA 効果を想定して設計しており、1<sup>2</sup>Gb の巨大ラストレベルキャッシュへの適用が可能と見込んでいる。それを超える大容量メモリ実現のためには、これを一桁程度上回る巨大 VCMA 効果が必要になると予想している。

図1: VC-MRAM の書き込みエラーを低減するための逆極性引加方式とそれを実現するための回路 (Verify-Sandwiched-Write 回路)

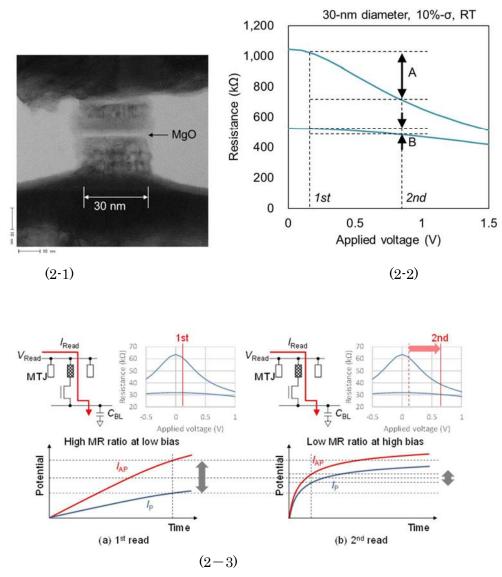

また、読み出しの問題を解決するために、読み出し電圧に対して MTJ 素子の抵抗が変化する現象に着目した読み出し回路 (Read Disturb Free Self-Reference Read 回路)を開発した (図 2 参照)。作製した直径 30nmのメモリ素子の実測データ (産総研、野崎 PI グループの実験データ)をもとに、書き込み・読み出しのエラー率が大幅に改善されることを先端 CMOS の回路シミュレーションで示した。図 2-2 の読み出し原理:高抵抗状態の MTJ (上側)と抵抗状態の MTJ (下側)では、読み出し時に MTJ にかける電圧に対する「変化率」が大きく異なる。低い電圧での読み出し(図中の 1st)と、高い電圧での読み出し(図中の 2nd)で、変化率の差を 0と1のデータに変換する。従来の STT-MRAM の場合、読み出し電圧を高くすると、書き込まれるデータが反転してしまうため (Read Disturb) この方式は使えない。しかし、VC-MRAM では、Read と Write にかける電圧を逆にすることができるため、Read Disturb が起こらない点に着目した。(図 2-3) 読み出し回路動作:図 aの変化率の大 (高抵抗状態、図中の AP)と小 (低抵抗状態、図中の P)が、低い電圧での1回目の読み出し

(1st Read) と、高い電圧での読み出し(2nd Read)の出力差を使った。ビットライン容量(図中 CBL)に充電する回路機構を使い、出力電圧がそれぞれ上昇、下降する回路を設計した。先端 CMOS を用いた回路シミュレーションにより、Gb クラスのキャッシュメモリに必要な高速 Read と高い読み出しマージンを実現することが分かった。

また、理想的な回路シミュレーションにおいては、VC-MRAM の VCMA が 400fJ/Vm 程度を超える大きな値を得られる場合で、読み出しと、書き込みともに正味エラー率〈1x10<sup>-10</sup>となることを確認している。ただし、ここではまだ VC-MRAM 素子の実験データや、理論予測値は反映させておらず、標準的な素子特性ばらつきファクタのみしか考慮していない。この部分に関しては、来年度以降に取り組む計画である。

図2:作製した VC-MRAM 素子の断面写真(2-1)と、読み出し電圧に対する素子抵抗の変化(2-2)と読み出しエラーを低減するための Read Disturb Free Self-Reference Read 回路動作 (2-3)

本成果は、2016年12月7日水曜日@米国サンフランシスコに半導体国際会議 IEDMにて、技術発表を行った。

さらに素子特性の大幅な改善が可能となれば、より大きな容量のメモリへの適用も期待される。今後これらの課題解決に取り組んでいく。

#### ➡ 項目2: 大容量型電圧駆動 MRAM の回路設計

與田 PI のグループからコンセプト提案された VoCMS をベースとして、メインメモリ用途を狙った大容量型電圧駆動 MRAM の回路設計を行った。まず、読み出し回路について。VoCSM では、読み出しは VC-MRAM と同様に電圧効果 MTJ のデータを Read するので、高速読み出し回路としては、項目 1 で開発した読み出し回路 (Read Disturb Free Self-Reference Read 回路) をそのまま利用することが可能と考えている。速度スペックは、項目 1 のほうが高速(約 10ns アクセス)であり、項目 2 のほうが低速で十分マージンがある(ターゲットは約 40ns)。

次に書き込み回路について。単一ビットのみ書き込みする条件と、8ビット等のブロック一括書き込みの条件別に、書き込み回路のアレイ設計を行った。速度とエラー率については、SOT素子の実験と理論計算の土台となる基盤技術が揃った段階で、計算できる回路シミュレーション環境も作った。また、現存のDRAMの設計ルールに倣った形で、メモリの中核となるメモリセルアレイ部の設計を何通りか行い、先端DRAMに近いメモリセルアレイ面積に出来ることも詳細なレイアウト設計とプロセス設計との組み合わせで理論実証している。さらに素子への電圧印加するビットラインワードライン等配線の伝送系統を多層化することで、面積効率が向上する案も取り入れた。さらに、H28年度中に、周辺回路部も含めた全体の回路構成を設計し、第一次の面積と性能を見積もる予定。

また、理想的な回路シミュレーションで、読み出し回路に関しては VC-MRAM と同様の回路になるので、VCMA が大きな値を得られる場合を想定すれば、読み出しエラー率 $\langle 1x10^{-10}\rangle$  となる。また、書き込み(単一ビット書き込み)ともにエラー率= $0(\langle 1x10^{-10}\rangle)$  となることも確認している。ただし、ここではまだ MRAM 素子の実験データや、微細素子の理論予測値は反映させておらず、回路動作マージンのみの評価である。現実的な素子特性ばらつきファクタも考慮していない。そのため多ビットー括書き込みのエラー率はまだ算定できてない。これは、H29 年 3 月までに理想条件下で算定し、さらに H29 年度以降に精度をあげて評価する計画である。そのために、素子実験データを高い精度で反映させ、シリコン回路部も実製品により近い設計ルールで詳細設計を行い、速度性能とエラー率の精査と回路による改善のための設計を行っていく。そのために、課題 5 の項目(5)として切り出し、回路開発に特化していく予定。

#### 2-2 成果

- 4 項目1: Gbクラスの巨大容量ラストレベルキャッシュを想定した高速 MRAM 用途向けに、新規の書き込み回路 (Verify-Sandwiched-Write 回路) と新規の読み出し回路 (Read Disturb Free Self-Reference Read 回路)を提案し、将来実現可能と予測される VCM 素子を基に一次回路を設計した。理想的な回路シミュレーションを行い、動作条件の本年度目標(書き込み・読み出しエラー率<1x10⁻¹⁰)を達成した。

- 4 項目2: DRAM と同等の容量をもつメインメモリをターゲットして、VoCSM メモリアーキテクチャをベースに、メモリセルアレイ回路の一次設計を完了。さらに、速度性能とエラー率を計算する 土台となる回路シミュレーション技術も開発した。1ビットごとの書き込み・読み出しエラー率

を、素子ばらつきが無視できる理想的な条件で回路シミュレーションを行い、どちらのエラー率についても<1x $10^{-10}$ を達成した。

# 2-3 新たな課題など

キャッシュメモリやメインメモリアプリケーションという単純な既存メモリ置換だけでなく、ストレージクラスメモリや、他の新たな不揮発メモリ用途を、電圧駆動 MRAM の特徴をより生かせるアプリケーション開拓を意識して、検討していく必要がある。

# 3. アウトリーチ活動報告

特になし。