#### Dependable VLSI

National Institute of Advanced Industrial Science and Technology AIST MITSUBISH Tamper Resistance

2012.12.1 DLSI International Symposium

# The Design and Evaluation Methodology of Dependable VLSI for Tamper Resistance

Focusing on the security of hardware modules

- Tamper resistant cryptographic circuit

- Evaluation tools for tamper resistance

- Physical Unclonable Function (PUF)

Takeshi Fujino @ Ritsumeikan Univ. Yohei Hori @ AIST Masaya Yoshikawa @ Meijo University Daisuke Suzuki @ Mitsubishi Electric

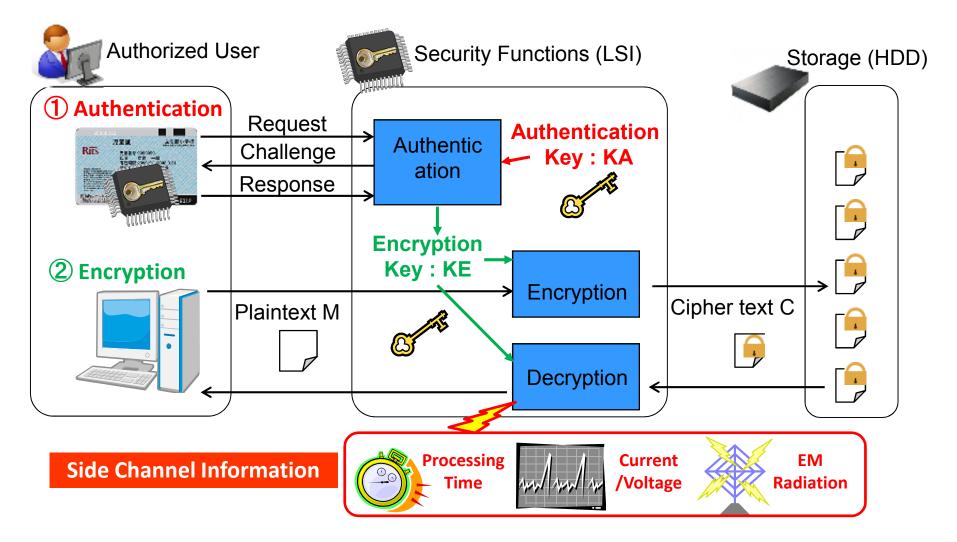

## **Cryptographic module and Side Channel Information** <sup>2</sup>

### Cryptography for Realizing Security Functions (exam.)

Authentication: Read/write permissions to HDD are granted to authorized users

Encryption: HDD are encrypted in case of loss or theft

Dependable VLSI

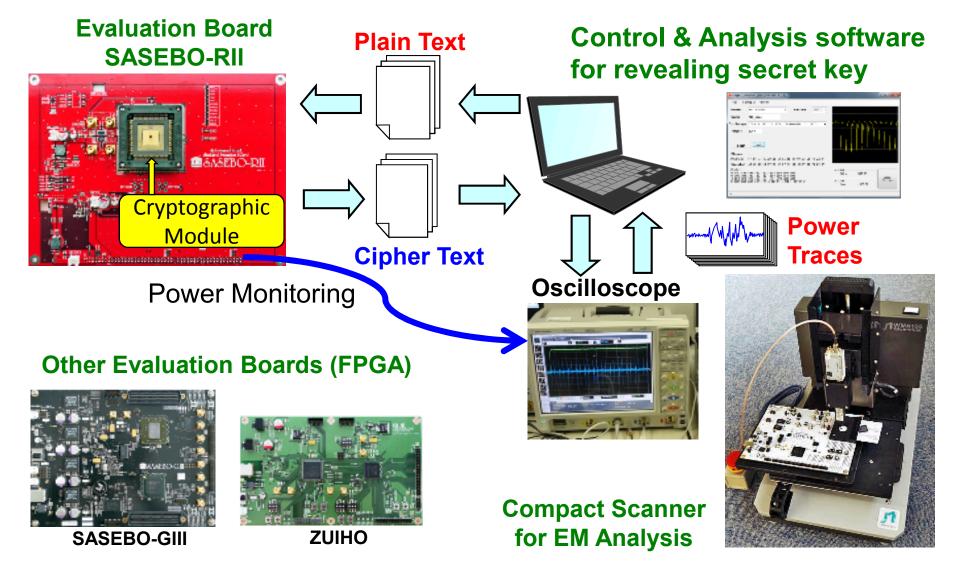

## Side Channel Attack (Differential Power Analysis)

Secret key is revealed by exploiting power traces from crypto module

The evaluation tools are also developed in this project

#### Dependable VLSI

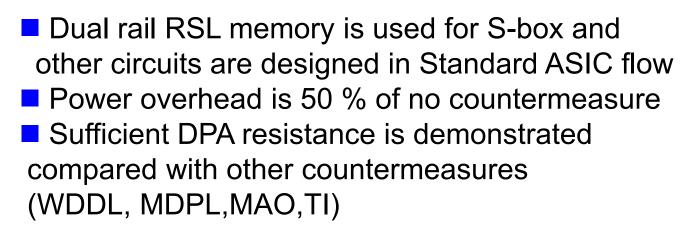

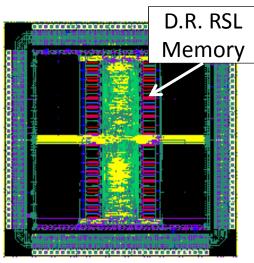

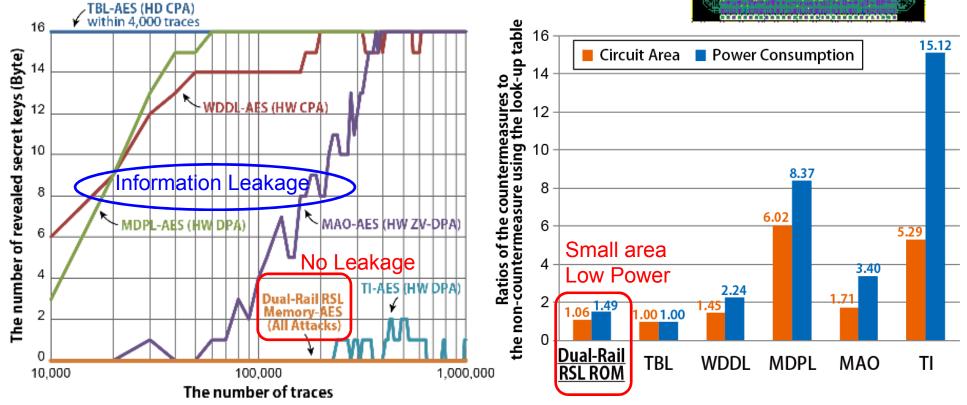

## DPA resistant AES circuit using dual-rail RSL memory

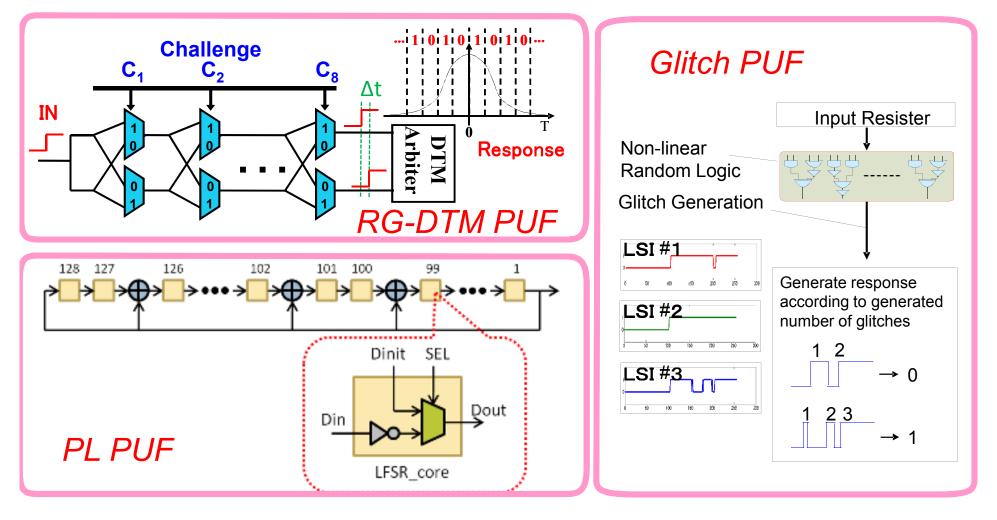

## Physical Unclonable Function for anti-counterfeiting

### PUF exploit the random process variations which make each chip unique and unclonable

- The authentication using PUF is useful for anti-counterfeiting

- RG-DTM Arbiter PUF, Glitch PUF, and PL PUF are developed