# フィールド高信頼化のための 回路・システム機構

### CREST DVLSI ワークショップ 2011年3月5日

研究代表者:梶原誠司(九州工業大学)

主たる共同研究者:藤原秀雄(奈良先端科学技術大学院)

主たる共同研究者:三浦幸也(首都大学東京)

# 研究の背景と狙い

2

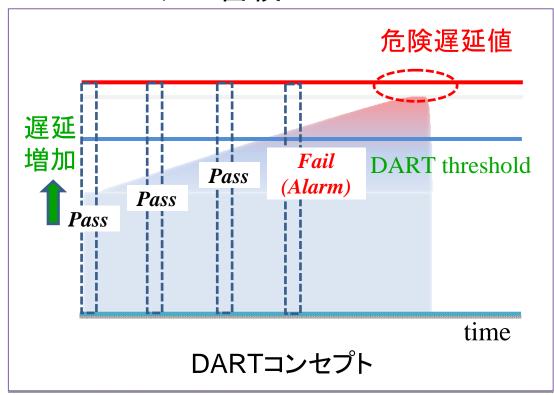

DART:本研究で提案するフィールドテスト技術 システム運用中の自己テスト・遅延測定による故障検出/劣化検知 ~突然のシステムダウンを回避・・・安全・安心~

# DARTコンセプトと効果

- ■フィールドテストによる故障検知・劣化検知

- ■劣化による増加する遅延を繰り返し測定

- ■ログの蓄積

#### システム信頼性向上

- ■故障の事前検知

- ■誤動作時の診断情報提供

- ■遅延値変化履歴

- 環境(温度・電圧)履歴

#### システム開発効率向上

- ■LSI設計マージンの把握

- ■LSI劣化度合いの把握

- ■システム診断情報提供

# DARTコンセプトと技術課題

- ■フィールドテストによる故障検知・劣化検知

- ■劣化による増加する遅延を繰り返し測定

- ■ログの蓄積

#### システム化

■DART アーキテクチャ

#### 遅延測定

■温度&電圧モニタ回路

#### テスト制約

- ■温度均一化テスト

- ■LSI劣化度合いの把握

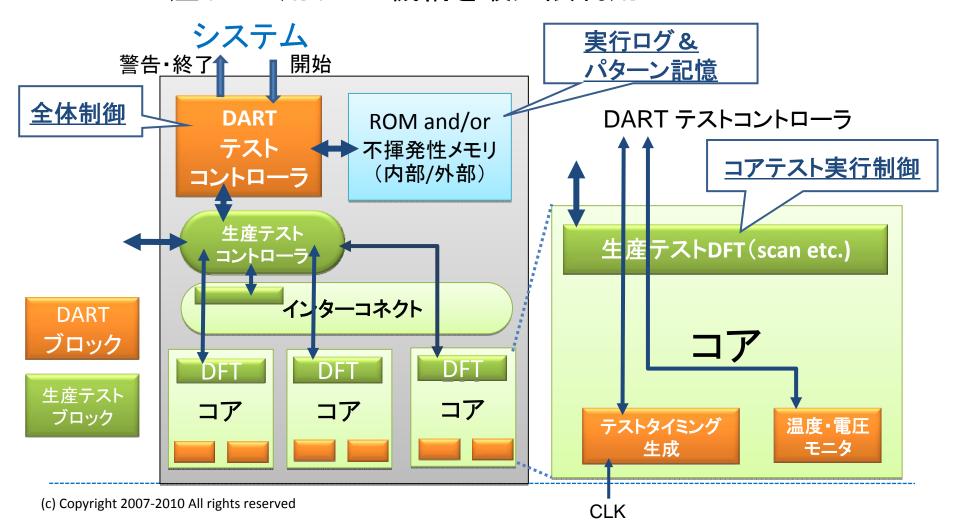

## DARTのアーキテクチャ

5

- ■フィールドテストによる故障検出/劣化検出

- ■生産テスト用テスト機構を最大限利用

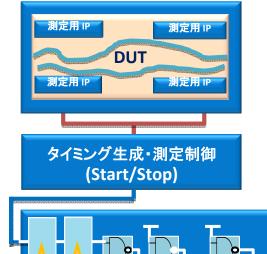

# モニタ回路

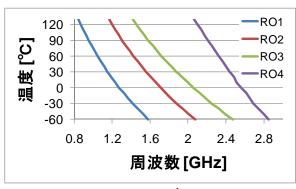

| ねらい | FF間の遅延テストで測定された論理パスの遅延値に対して,<br>温度や電圧の影響を補正するために, テスト時環境をモニタする.                                                             |

|-----|-----------------------------------------------------------------------------------------------------------------------------|

| 目標  | 温度, 電圧の推定精度:3~5%程度を目標に検討中.                                                                                                  |

| 内容  | ・モニタ回路は劣化の影響を受けないよう工夫する. ・テスト時に、RO(Ring Oscillator) ベースの回路で発振周波数を測定. ・出力の周波数は、上位階層の全体制御IPで、遅延値補正に用いる. (補正方法を含めて本技術研究で検討を行う) |

#### 測定回路系の概略図

- ROの温度変化に対する 線形性活用

- 異なる特性RO併用による 推定精度向上

$$\begin{bmatrix} Te \\ Ve \end{bmatrix} = \begin{bmatrix} a_1 & b_1 \\ a_2 & b_2 \end{bmatrix}^{-1} \begin{bmatrix} k_1 F_{d1} - k_2 F_{d3} \\ k_3 F_{d2} - k_4 F_{d3} \end{bmatrix} + \begin{bmatrix} c_1 \\ c_2 \end{bmatrix}$$

$F_d(T,V) \equiv F(T,V) - F(T_0,V_0)$

初期値と測定周波数の差分から 温度, 電圧を推定(特願2010-057310)

(c) Copyright 2007-2011 All rights reserved

Counter

測定用IP

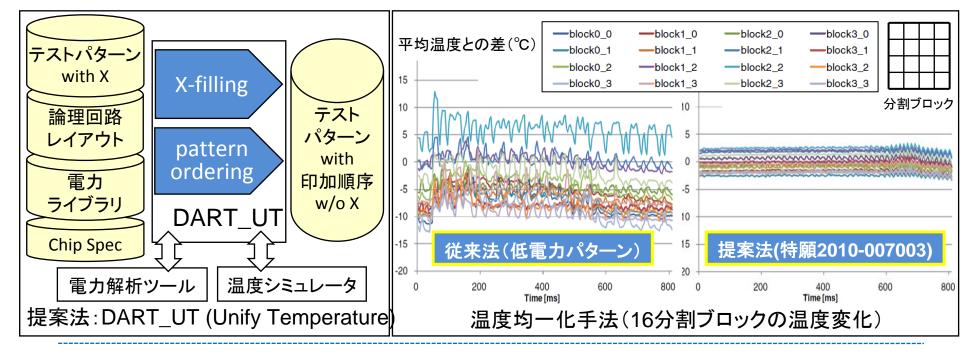

# 温度均一化テスト

| ねらい | テスト時のチップ内温度を均一化し、温度による遅延変動量を<br>低減することにより、高精度な遅延故障テストを実現する.               |

|-----|---------------------------------------------------------------------------|

| 目標  | (1) テスト時のチップ内位置による温度差:10℃以内<br>(2) テスト時の同一位置の温度差:5℃以内 *テスト開始直後の急激な温度上昇は除く |

| 内容  | 入力:ドントケア付きテストパターン、論理回路、レイアウト<br>出力:温度均一化テストパターンと印加順序(故障検出率は維持)            |

8

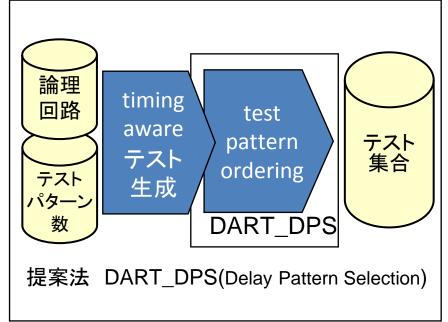

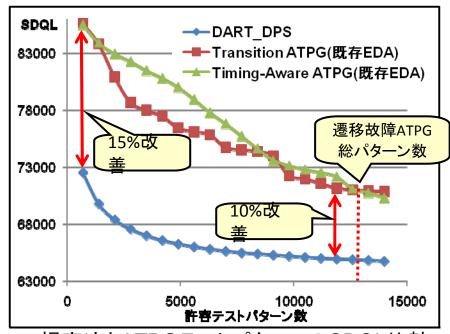

# 高品質遅延テスト集合

| ねらい | 許容テストパターン数に応じて高品質遅延テスト集合を生成する                                                                      |

|-----|----------------------------------------------------------------------------------------------------|

| 目標  | 許容テストパターン数に対し、SDQL(未検出の微小遅延量)を最適化<br>遷移故障ATPGパターン集合に対するSDQL改善値:<br>許容パターン数小の場合:15%,許容パターン数大の場合:10% |

| 内容  | 入力:論理回路、テストパターン数<br>出力:遅延故障用テストパタン集合                                                               |

提案法とATPGテストパターンのSDQL比較