SCIS 2013 The 30th Symposium on Cryptography and Information Security Kyoto, Japan, Jan. 22-25, 2013 The Institute of Electronics. Information and Communication Engineers

# 認証と乱数生成利用のための遅延時間差検出型アービターPUF の最適化手法 Optimization Method of RG-DTM PUF for Authentication and Random Number Generation

寺村 匡弘\* 岡本 卓朗# 汐崎 充† 村山 貴彦# 藤野 毅\* Masahiro Teramura Mitsuru Shiozaki Takuro Okamoto Takahiko Murayama Takeshi Fujino

あらまし LSI の複製偽造防止技術として製造時の物理ばらつき情報から複製困難なデバイス固有情 報を生成する Physical Unclonable Functions (PUF)が注目されている. 本研究室ではセレクタチェー ン回路で生じる遅延時間差を測定し、複数区間に分割された遅延時間差情報からレスポンスを生成す る遅延時間差検出型アービターPUF (RG-DTM PUF)を提案してきた. 今までの検討で, RG-DTM PUF は、機械学習攻撃耐性に強いチャレンジ―レスポンス認証に適用できる一方、乱数発生にも応用でき る可能性を示してきた. RG-DTM PUF においては、セレクタチェーンの段数と、アービター回路に おける遅延時間差分割数の2つのパラメータにより、認証性能や発生した乱数の質が変化する。そこ で、今回これらの2つのパラメータの最適化を行うために、セレクタ段数によって変化する遅延時間 の分散を最適分割できるアービター回路を搭載したチップを 0.18 μ m CMOS プロセスを用いて試作 した.  $8\sim128$  のセレクタ段数と  $4\sim32$  の遅延時間差分割数を持つ試作チップを用い、チャレンジーレ スポンス認証の評価指標としては、本物を偽物と認証してしまう確率 (FNR)と偽物を本物と認証して しまう確率 (FPR)を導出して評価し、乱数生成評価指標としては NIST 検定と DIEHARD 検定を用い た評価を行った、これらの実験結果より、RG-DTM PUF における、認証用途と乱数生成用途に最適 なセレクタ段数と時間差分割法について考察した結果を報告する.

## キーワード PUF, 遅延時間差検出型アービターPUF, 認証, 乱数生成

#### 1 はじめに

近年,電子部品の模造品が深刻な問題となっている. 半導体の模造品市場は世界の半導体市場の 5%にまで達 するとの報告もある[1]. 実際に国内でも模造品の被害は 発生しており、海外だけの問題ではない. 模造品は金銭 被害だけではなく, ブランドイメージの低下といった 2 次的な被害も引き起こしてしまう. 自動車や医療機器に 模造品が使用されると人命にかかわる問題にまで発展す る恐れがある. また、セキュリティ内蔵のチップであっ ても消費電力や発生した電磁波を分析すれば機密情報を

盗むことができ、偽造・複製される危険性があるため早 急な対策が必要とされている. この対策として複製が困 難なデバイス固有の ID を生成できる Physical Unclonable Function (PUF)という技術が注目されてい る. PUF は入力信号 (チャレンジ) に応じて、デバイス ごとに内在する物理的な差異が出力信号(レスポンス) として抽出されるチャレンジ&レスポンス方式のデバイ スである. LSI に実装される PUF[2]は、トランジスタ や配線のサイズなどの製造ばらつきによる僅かに異なる 物理量を抽出して、デバイス固有のレスポンスを生成す る. 製造ばらつきはランダムで人工的に制御することが 困難なので、PUFが生成するレスポンスは複製・偽造が 困難なデバイス固有の ID となる.

LSI に実装される PUF の 1 つとして, 2 つのセレクタ チェーン間で製造ばらつきによって生じる遅延時間差の 正負をレスポンスへと変換するアービターPUF[3]があ る. アービターPUF は非常に多くのチャレンジとレスポ ンスのペアを持ち、レスポンスを生成するタイミングに 制約がなく、設計が比較的容易という利点がある。しか

<sup>\*</sup> 立命館大学理工学部, 〒525-8577, 滋賀県草津市野路東 1-1-1, 上 中語大学経上手部、「525 6577, 佐賀宗早年市月昭末 111, Department of Science and Engineering, Ritsumeikan University, 1-1-1 Noji-higashi, Kusatsu, Shiga, Japan, {ri0004@ed,fujino@se}.ritsumei.ac.jp †立命館大学総合理工学研究機構、〒525-8577, 茂賀県草津市野路東 111-11 Persented Organization of Science & Fraciocopius

<sup>1-1-1,</sup> Research Organization of Science & Engineering, Ritsumeikan University, 1-1-1 Noji-higashi, Kusatsu, Shiga,

Japan, mshio@fc.ritsumei.ac.jp · 立命館大学大学院理工学研究科, 〒525-8577, 滋賀県草津市野路 東 1-1-1, Graduate School of Science and Technology, Ritsumeikan University, 1-1-1 Noji-higashi, Kusatsu, Shiga, Japan, {ri009072, ri002072}@ed.ritsumei.ac.jp

し、アービターPUFは生成するIDに偏りを持つためユニーク性が低く、さらに機械学習攻撃を用いた攻撃が可能という問題がある.

これらの問題点を解決した遅延時間差検出型アービターPUF (RG-DTM PUF)を我々は提案してきた[4]. RG-DTM PUFは2経路間に生じる遅延時間差の正負だけでなく、遅延時間差を一定時間ごとに分割しレスポンスを出力することでユニーク性を向上させた。そして、機械学習攻撃耐性の評価し、認証や乱数生成に利用可能であることを示してきた。しかし、今まで評価してきたRG-DTM PUFは遅延時間差をセレクタ段数に合わせて最適な分割刻みで設計したものでなかった。そこで、セレクタ段数に合わせて最適な遅延時間差を分割する遅延時間差検出型アービター回路の再設計を行い。試作チップにより認証と乱数生成が同一回路で実現できることを示すための評価を行った。

本論文の構成は、第2章でRG-DTM PUF について説明し、セレクタ段数ごとに分割時間を最適設計した内容について述べる。そして、第3章で再設計したRG-DTM PUF の実測結果から認証と乱数生成に最適なセレクタ段数と分割数の評価を行った結果を示し、第4章でまとめる。

## 2 RG-DTM PUF の最適化

## 2.1 RG-DTM PUF

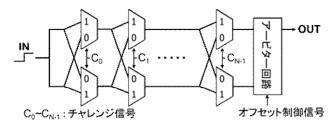

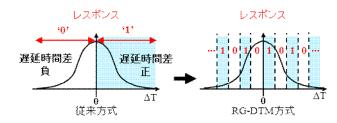

RG-DTM PUF は図1に示すように多段接続されたセレクタチェーンとアービター回路で構成される。セレクタチェーンはチャレンジ信号に応じて IN からアービター回路までの2つの経路の選択を行う。各セレクタは製造ばらつきによって異なる遅延時間を生じるので、最終段での伝達信号の遅延時間差はチャレンジごとに異なる。セレクタチェーンの最終段における遅延時間差の分布は正規分布となっており、従来型のアービターPUFでは図2のように遅延時間差の正負をレスポンスに変換していたのに対し、RG-DTM PUFでは遅延時間差の分布を複数区間に分割し、領域ごとに割り当てた0/1の値をレスポンスに変換する。これにより、IDの偏りをなくしユニーク性を向上させることができた。

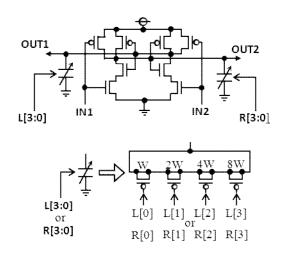

RG-DTM PUF のアービター回路は図3に示すように、センスアンプと可変容量で構成されている。可変容量はゲート幅サイズの異なる4つのPMOSトランジスタで構成され、オン・オフを制御することで、0/1の判定基準にオフセットを設定できる。この0/1の判定基準をシフト制御することで、伝達信号の遅延時間差がレスポンス0/1のどちらの領域に存在するかを調べ、レスポンスに変換する。

図 1. RG-DTM PUF の構成

図 2. レスポンスの生成方法

図3. アービター回路の構成

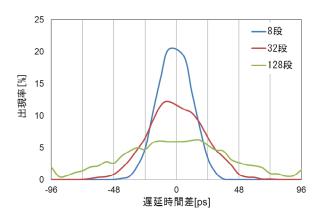

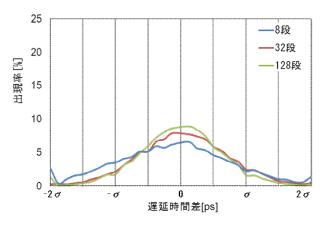

以前、遅延時間差分布がセレクタ段数の増加に伴って 広がっていくのかということと、その分布の広がりは分 散の加法性が成り立っているのかということを調べる目 的で RG-DTM PUF の設計・試作を行った、そのため、 アービター回路はセレクタチェーンの段数に関係なく全 て同一の回路を用いた. 分割する時間刻みはセレクタ 8 段から 128 段の遅延時間差分布が分割できるように 6ps 刻みで最大90psとなるように設計した。20個の試作チ ップに対し、可変容量のオフセット機能を用いて、セレ クタ段数8段,32段,128段におけるセレクタチェーン で生じる遅延時間差分布を導出した結果を図 4 に示す. セレクタ段数が増加に伴って遅延時間差分布が広がって いることがわかる. 8段, 32段, 128段の分布の標準偏 差はそれぞれ 14.48ps, 25.56ps, 43.00ps と、セレクタ 段数が N 倍になれば標準偏差は $\sqrt{N}$  倍となり、分散の加 法性が確認できていた.

図 4. セレクタ段数ごとの遅延時間差分布

### 2.2 RG-DTM PUF の再設計

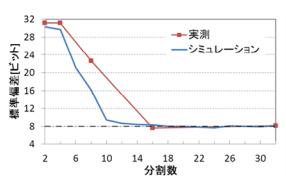

本来, RG-DTM PUF のアービター回路はセレクタ段 数に合わせて最適な分割刻みで設計する必要がある. そ こで、高いユニーク性を保持するために、どの程度遅延 時間差分布を分割すれば良いか検討を行った. 図5にセ レクタ段数8段の分割数とユニーク性の指標として標準 偏差の関係を示す. 横軸はセレクタ段数8段で生じる遅 延時間差分布±6σ(セレクタ段数8段で生じている遅延 時間差分布の標準偏差o=15.40ps) を何分割しているか を表している. 縦軸は、複数の PUF から生成された ID 間のハミングディスタンス(HD)分布の標準偏差を表し ている. ID のビット長は全 256 種類のチャレンジを与 えて得た 256 ビットである. PUF から全種類の ID が等 確率で出現するとき、ID 間 HD 分布の標準偏差は8ビ ットとなることから、高いユニーク性の指標として標準 偏差値8ビットを目標値としている.2分割はアービタ -PUF を意味し、4 分割は $\pm 3\sigma$ の箇所でも領域分割を行 っていることを意味する. 分割数の増加に伴い標準偏差 は低下していき, 高いユニーク性を保持するには 16 分 割(=0.75σ刻み)以上が必要であることがわかる. つま り、十分なユニーク性をもつ RG-DTM PUF を設計する には遅延時間差分布の標準偏差σを求め、アービター回 路により 0.75 σより細かく領域分割すればよい.

図5. セレクタ段数8段の分割数と標準偏差

この結果から、分割方法をセレクタ段数に合わせて最適設計を行った RG-DTM PUF を試作した。遅延時間差分布の機械学習攻撃の観点から 4分割以上することを想定し、 $\pm 2\sigma$  を最大 32 分割するように設計を行った。 $\pm 2\sigma$  より外の遅延時間差を無視したのは、分割効果が全く無かったためである。セレクタ段数 8 段、32 段、128 段の遅延時間差分布の  $2\sigma$  値はそれぞれ、31ps、62ps、123ps であった。結果を表 1 にまとめる。そして、それぞれの値に合わせてアービター回路の PMOS サイズを設計した。

表 1. セレクタ段数ごとの 2σ値

| セレクタ段数 | 8段 | 32段 | 128段 |

|--------|----|-----|------|

| 2σ[ps] | 31 | 62  | 123  |

## 3 改良版 RG-DTM PUF の実測評価

#### 3.1 ユニーク性と再現性の評価

最適設計した改良版 RG-DTM PUF の遅延時間差分布の実測結果を図6に示す.30個のPUF回路を実測評価した結果である。セレクタ段数ごとに分割間隔を最適化したため、セレクタ段数が異なっていても遅延時間差分布(32の各領域における出現頻度)が一致していることが確認できた.

図 6. 段数と遅延時間差分布

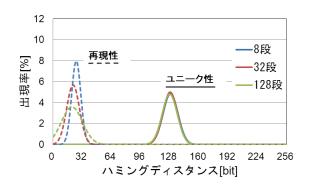

改良版 RG-DTM PUF の性能評価としてユニーク性と再現性の評価を行った。ユニーク性は、2 つのチップの ID を比較したときどれだけ異なるかを示す指標であり、異なる2つのチップに対して同一のチャレンジを入力し生成された256 ビット長の ID 間の HD を算出することで得られる。ID 長を N とした場合、ユニーク性の HD の分布の平均が N/2、標準偏差が $\sqrt{N}$  /2 が理想値となる。再現性とは、あるチップが生成する ID の安定性を表しており、同一のチップに対して同一のチャレンジを入力して生成された ID 間の HD を算出することで得

られる. 安定した ID を生成するためには、再現性のグラフが HD0 に多く分布していることが理想となる.

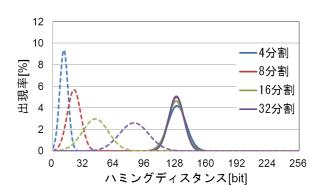

まず、8分割でセレクタ段数を8段、32段、128段と変化させたときのユニーク性と再現性の分布を図7に示す。実線がユニーク性、点線が再現性を表す。8分割では十分なユニーク性が得られるので、段数に関係なく平均128ビット、標準偏差8ビットの理想的な正規分布となっていた。一方、再現性は分布の平均値が段数の増加に伴って減少しているのに対して、分散は増加する傾向が得られた。

図7.8分割のユニーク性と再現性

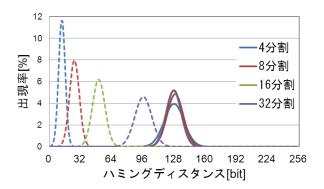

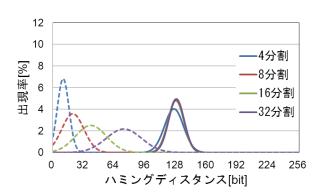

次に、セレクタ段数ごとに分割数を変化させたときの ユニーク性と再現性の分布を図8~10に示す。これらの 図でも実線がユニーク性, 点線が再現性を表す. 図8の セレクタ段数8段ではユニーク性の平均は4分割から順 に 127.54 ビット, 128.70 ビット, 126.90 ビット, 127.45 ビット,標準偏差は10.10ビット,8.22ビット,7.74ビ ット、7.66 ビットであった. 4 分割のみ 1σ 刻みと 0.75σ を超えているので、わずかに分散が広がり、生成される ID に多少なりとも偏りがあると考えられる. 再現性は平 均が4分割から順に12.54ビット,25.39ビット,50.24 ビット,96.03 ビットとなり,分割数が N 倍になれば平 均も N 倍となる関係性があった. これは単純に分割数が 増えた影響だと考えられる. 標準偏差は4分割から順に 3.41 ビット, 5.00 ビット, 6.44 ビット, 8.68 ビットと なり、分割数を増加することで標準偏差も増加する傾向 が確認できた. これらの傾向は図 9 のセレクタ段数 32 段,図10のセレクタ段数128段においても確認できた. 各平均と標準偏差は表2にまとめる. また, 分割数に関 係なく再現性分布はセレクタ段数の増加に伴って平均は 減少,分散は広がる傾向が確認できた.

図8. セレクタ段数8段のユニーク性と再現性

図 9. セレクタ段数 32 段のユニーク性と再現性

図 10. セレクタ段数 128 段のユニーク性と再現性

表 2. 再現性とユニーク性の平均と標準偏差

|      |       | 再現性   |       | ユニーク性  |        |        |  |

|------|-------|-------|-------|--------|--------|--------|--|

| 平均   | 8段    | 32段   | 128段  | 8段     | 32段    | 128段   |  |

| 4分割  | 12.54 | 11.34 | 10.61 | 127.54 | 128.91 | 125.81 |  |

| 8分割  | 25.39 | 21.91 | 20.66 | 128.70 | 128.28 | 127.82 |  |

| 16分割 | 50.24 | 44.16 | 39.48 | 126.90 | 128.04 | 127.88 |  |

| 32分割 | 96.03 | 84.28 | 73.72 | 127.45 | 128.22 | 128.36 |  |

| 標準偏差 | 8段    | 32段   | 128段  | 8段     | 32段    | 128段   |  |

| 4分割  | 3.41  | 4.27  | 6.04  | 10.10  | 9.49   | 9.88   |  |

| 8分割  | 5.00  | 7.01  | 11.49 | 8.22   | 7.98   | 8.28   |  |

| 16分割 | 6.44  | 13.38 | 15.98 | 7.74   | 8.61   | 8.07   |  |

| 32分割 | 8.68  | 15.26 | 18.34 | 7.66   | 7.85   | 8.06   |  |

#### 3.2 認証評価

PUF を用いた簡易認証は、あらかじめ登録してある IDとPUFが生成したIDとの一致度から認証する.PUF には再現性の結果からわかるようにビットの 0/1 が安定 しない不安定ビットが複数存在する. そのため、認証に はある程度の誤りを許容する必要がある. 本節では、改 良版 RG-DTM PUF が認証に使用できるかを評価する ため、ユニーク性と再現性から False Positive Rate (FPR) と False Negative Rate (FNR) の 2 つの指標 を導出する. FPR は誤り許容ビットを大きく設定したた め、偽物を本物と認識する確率を表し、FNR は誤り許 容ビットを小さく設定したため、本物であるのに偽物と 認識する確率を表す. 認証に用いる ID 長を N, ユニー ク性の HD が M ビットとなる確率を Pu(M), 再現性の HD が M ビットとなる確率を Ps(M)とすると, 誤り許容 ビット T と設定したときの FNR と FPR は以下の式で 導出できる.

$$FPR(T) = \sum_{i=0}^{T} P_{U}(i)$$

$$FNR(T) = 1 - \sum_{i=0}^{T} P_{S}(i)$$

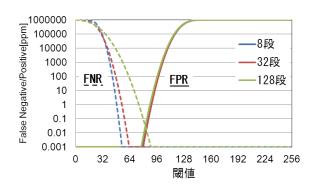

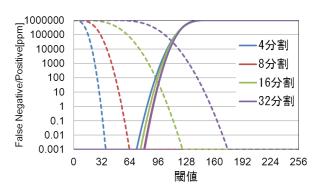

まず、3.1 節同様、8 分割でセレクタ段数を8段、32段、128段と変化させたときの導出したFPRとFNRの結果を図11に示す。実線がFPR、点線がFNRを示す。横軸は誤りを許容するビット数(認証における閾値)を表し、縦軸はそのときのFPR、FNRを表している。FPRはユニーク性から導出するため、セレクタ段数に依存せず同じ曲線を描いているのがわかる。一方、再現性から導出するFNRは段数の増加に伴って悪化し、より多くの誤りビットを許容する必要がある。0.001ppm以下の誤認率を達成しようとするとセレクタ段数128段は使用できないことがわかる。この結果より安定した認証システムを構築するにはセレクタ段数は少ない方が良いことがわかる。

図 11.8 分割の FNR と FPR

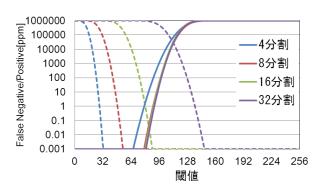

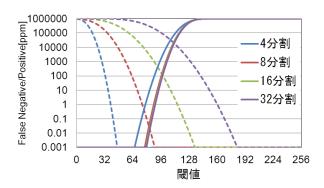

次に、セレクタ段数ごとに分割数を変化させたときの FNR と FPR の結果を図 12~14 に示す. これらの図に おいても実線が FPR、点線が FNR を示す.

図12のセレクタ段数8段では、図8の結果からも確認できていた理想的なユニーク性が得られていない4分割のみFPRが悪化しているのがわかる.FNRは分割数の増加に伴って大きく悪化しており、16分割であれば良くて誤認率0.1ppm、32分割に至っては1割の確率で誤認してしまい、誤認率0.001ppm以下が全く達成できないことがわかる.これらの傾向は図13のセレクタ段数32段、図14のセレクタ段数128段においても確認できた.

以上の結果より PUF を用いて安定した認証を行うにはセレクタ段数、分割数共に少なく設定した方が良いしかし、4 分割であるとユニーク性に問題がある上、分割数が少ないと機械学習攻撃に脆弱になり、ID が予測されてしまう恐れがある。そのため、分割数は8~16分割ぐらいに設定した方が良い。使用回数や用途、コストにもよるが、より安定した認証を行うには ID 生成に多数決を導入する、ID のビット長を増やすといった対策が必要だと考えられる。

図 12. セレクタ段数 8 段の FNR と FPR

図 13. セレクタ段数 32 段の FNR と FPR

図 14. セレクタ段数 128 段の FNR と FPR

## 3.3 乱数評価

改良版 RG-DTM PUF を乱数生成に用いた場合、統計 的に乱数として適しているかを評価するため、改良版 RG-DTM PUF に疑似乱数を用いてチャレンジを与えて 1G ビット分のレスポンス生成し、乱数評価ツールであ る DIEHARD 検定と NIST 検定を用いて乱数生成評価 を行った. DIEHARD 検定とは、フロリダ州立大学 Marsaglia 博士により提唱され、乱数列の長さは、80~ 88M ビット 程度必要となるので、1G ビットのレスポ ンスを 10 分割し 100M ビットずつ評価した. 検定の種 類は 18 種類あり、約 200 の p-value を出力する. 良い 乱数列の場合は p-value は[0; 1) に一様に分布し、良く ない乱数列の場合はp-value の分布が偏ってしまう. た だし、多数の p-value が得られるだけで、検定対象を良 い乱数と判断するための基準は述べられていない. そこ で、一様性を評価するため、得られた p-value の総数 n を 10 分の 1 となるよう 10 区分に分け、各区分での度数  $C_{\chi^2}$ 検定を検定行った.  $\chi^2$ 値は次式を用いて導出でき る.

$$\chi^2 = \sum_{i}^{10} \frac{(F_i - \mathbf{n}/\mathbf{10})^2}{n/\mathbf{10}}$$

n は標本数 (p-value),Fi は i 番目の区間に入った p-value の個数を表す.このとき, $\chi^2$ 分布の自由度は 9 となり,有意水準をNIST検定に合わせ1%としたので,対応する  $\chi^2$  値が  $\chi^2 \le 21.66$  となれば合格と判断する. DIEHARD 検定の評価結果を表 3 に示す.まず,セレクタ段数 8 段では全ての分割数で合格数が 0 となっており,乱数としては使えないことがわかった.セレクタ段数を 32 段,128 段と増やし,更に分割数を 16 分割以上に増やすと DIEHARD 検定に合格する.傾向としては図 7~10 の再現性より,不安定なビットが増加するように RG-DTM PUF を設定すれば乱数生成用途には良いと言える.また,セレクタ段数 128 段の 8 分割のときに 10回中 6 回は検定に合格していることから,再現性の平均よりも標準偏差による影響が大きい.

表 3. DIEHARD 検定の合格数

|      | 4分割  | 8分割  | 16分割  | 32分割  |

|------|------|------|-------|-------|

| 8段   | 0/10 | 0/10 | 0/10  | 0/10  |

| 32段  | 0/10 | 0/10 | 10/10 | 10/10 |

| 128段 | 0/10 | 6/10 | 10/10 | 10/10 |

次に、NIST 検定による評価を示す。NIST 検定とは、 米国国立標準技術研究所が公開している乱数検定ツールでプログラム NIST SP800-22 を用いて評価される。 NIST 検定は本来 15 種類のテスト項目が存在するが、その中のひとつである FFT テストにはプログラムに誤りがあることが報告されているため除外して評価を行っている[5]。NIST 検定の結果を表 4 に示す。DIEHARD 検定と同様、セレクタ段数 8 段や、4 分割や 8 分割ではほとんどの検定項目で不合格となっている。それに対して、セレクタ段数 32 段、128 段且つ、16 分割や 32 分割では多くの検定項目に合格している。この結果より、乱数生成で利用するには、セレクタ段数を 32 段以上で分割数を 16 分割以上で用いるのが良いと言える。

しかし、ここで示しているチップはNIST検定のRuns Test 検定に全く合格することがなかった. Runs Test は 入力数列内に連(1または0が連続している部分)がい くつあるかを数えて、その数の偏りを調べる検定である. そこで、本研究室で提案した手法の PUF のレスポンス に疑似乱数の線形帰還シフトレジスタ (LFSR) と XOR 演算を行い、得られたデータに対しても NIST 検定を行 った. 結果を表5に示す. セレクタ段数8段ではLFSR と XOR 演算を行なっても NIST 検定結果は殆ど変わら なかったのに対して、セレクタ段数32段では全ての検 定項目に合格した. まず, セレクタ段数8段はチャレン ジの全種類が 256 (=28) なので 256 ビットごとに同じ ようなビット列が少なくとも出現し,評価に使用する1G ビットに対してビット長が圧倒的に少ないことが検定に 合格しない理由であると考えられる. セレクタ段数 32 段について考えると、PUFは全てのIDを生成する観点 からすると、1または0が連続且つ安定して出力する可 能性は少なくともある。そこに LFSR の出力と XOR 演 算することで安定した 0/1 のデータ列も周期が非常に長 い疑似乱数値に置き換えることができるので合格しなか った Runs Test 検定も含めて合格するようになったと推 測する.

以上の結果より、RG-DTM PUF はセレクタ段数と分割数を増やす設定にし、更に LFSR の出力と XOR 演算したデータを使えば統計的に乱数として十分利用可能だと言える.

表 4. NIST 検定結果

| 検定項目                    | 4分割  |      | 8分割  |      | 16分割 |      |      | 32分割 |      |      |      |      |

|-------------------------|------|------|------|------|------|------|------|------|------|------|------|------|

| 快走項目                    | 8段   | 32段  | 128段 |

| Frequency               |      |      |      |      |      |      |      | Pass |      |      |      | Pass |

| BlockFrequency          | Pass |      |      |      | Pass | Pass | Pass | Pass | Pass |      | Pass | Pass |

| CumulativeSums          |      |      |      |      |      |      |      | Pass |      |      |      | Pass |

| Runs                    |      |      |      |      |      |      |      |      |      |      |      |      |

| LongestRun              |      |      |      |      |      | Pass |      | Pass | Pass |      | Pass | Pass |

| Rank                    | Pass |

| NonOverlappingTemplate  |      |      |      |      | Pass | Pass |      | Pass | Pass |      | Pass | Pass |

| OverlappingTemplate     |      |      |      |      |      |      |      | Pass | Pass |      | Pass | Pass |

| Universal               |      |      |      |      | Pass | Pass |      | Pass | Pass |      | Pass | Pass |

| ApproximateEntropy      |      |      |      |      |      |      |      | Pass |      |      | Pass | Pass |

| RandomExcursions        |      |      |      | Pass | Pass | Pass |      | Pass | Pass |      | Pass | Pass |

| RandomExcursionsVariant |      |      |      | Pass | Pass | Pass |      | Pass | Pass |      | Pass | Pass |

| Serial                  |      |      |      |      | Pass | Pass |      | Pass | Pass |      | Pass | Pass |

| LinearComplexity        | Pass |

表 5. LFSR との XOR 演算での乱数生成評価

|                                 |                         | ,    | ,     |       |       |       |  |

|---------------------------------|-------------------------|------|-------|-------|-------|-------|--|

| 検定                              | 検定項目(NIST)              | 8段   | 32段   |       |       |       |  |

|                                 | 快 <b>企</b> 填口(NIST)     | 32分割 | 4分割   | 8分割   | 16分割  | 32分割  |  |

| DIEHARD                         | 合格数                     | 0/10 | 10/10 | 10/10 | 10/10 | 10/10 |  |

| :<br>:<br>:                     | Frequency               |      | Pass  | Pass  | Pass  | Pass  |  |

| , i                             | BlockFrequency          | Pass | Pass  | Pass  | Pass  | Pass  |  |

| \$<br>\$<br>\$                  | CumulativeSums          |      | Pass  | Pass  | Pass  | Pass  |  |

| ž<br>t                          | Runs                    |      | Pass  | Pass  | Pass  | Pass  |  |

| NIST                            | LongestRun              |      | Pass  | Pass  | Pass  | Pass  |  |

|                                 | Rank                    | Pass | Pass  | Pass  | Pass  | Pass  |  |

|                                 | NonOverlappingTemplate  |      | Pass  | Pass  | Pass  | Pass  |  |

| IATO                            | OverlappingTemplate     |      | Pass  | Pass  | Pass  | Pass  |  |

| 2<br>2                          | Universal               |      | Pass  | Pass  | Pass  | Pass  |  |

| t<br>t                          | ApproximateEntropy      |      | Pass  | Pass  | Pass  | Pass  |  |

| 6<br>6<br>7<br>7<br>8<br>8<br>8 | RandomExcursions        |      | Pass  | Pass  | Pass  | Pass  |  |

|                                 | RandomExcursionsVariant |      | Pass  | Pass  | Pass  | Pass  |  |

|                                 | Serial                  |      | Pass  | Pass  | Pass  | Pass  |  |

| ,                               | LinearComplexity        | Pass | Pass  | Pass  | Pass  | Pass  |  |

#### 3.4 認証評価と乱数評価のまとめ

セレクタ段数に合わせて最適設計した RG-DTM PUF を測定評価した結果,同一回路で設定を変えることで認証にも乱数にも利用できることがわかる.使用回数や用途,コストを考えてセレクタ段数を決定し,認証デバイスとして利用するときには,分割数を8分割程度と比較的少なく設定してRG-DTM PUFを動作させれば良い.そして,乱数発生器として利用するときには,分割数を32分割と増やす設定にしてRG-DTM PUFを動作させれば良い.

### **4** まとめ

セレクタ段数ごとに最適な分割数になるよう RG-DTM PUF を再設計した. 過去の評価結果より遅延

時間差分布を標準偏差σに対して 0.75σ刻みより細かく 分割すれば ID に偏りのない高いユニーク性が実現でき るため、遅延時間差分布の±2gを最大32分割できるよ うに設計した. そして, 試作チップを実測してユニーク 性や再現性を評価したところ、4分割(1σ刻み)以上の 分割数であればセレクタ段数に関係なく理想的なユニー ク性の分布が得られた. 一方, 再現性は特に分割数の増 加に伴って不安定なビット数が増え悪化する結果が得ら れた. そして、認証用途の評価として FPR と FNR を導 出, 乱数生成用途の評価として DIEHARD 検定と NIST 検定を行った. その結果, 認証用途には再現性をなるべ く良くしたいので、分割数を4分割や8分割と少ない分 割数に設定することが適しているとわかり、乱数生成用 途には再現性をなるべく悪くして 0/1 の出現をランダム にしたいので分割数を16分割や32分割と多く設定する ことが適しているとがわかった. 結果を表6にまとめる. 以上より、同一の RG-DTM PUF 回路を用いて認証にも 乱数発生器として利用可能できることを示した. ただし、4 分割のときは、ユニーク性が悪く ID の出現に偏りがあることと、機械学習攻撃によってチャレンジ・レスポンス・ペアが窃取されるとモデル化されて出力が予測されることから使用できるケースは限られると考えられる.

表 6. 認証と乱数の分割数ごとの適正

|      | 4分割 | 8分割 | 16分割 | 32分割 |

|------|-----|-----|------|------|

| 認証   | Δ   | 0   | ×    | ×    |

| 乱数生成 | ×   | ×   | 0    | 0    |

## 謝辞

本研究は JST, CREST「ディペンダブル VLSI システムの基盤技術」の一環として行われた。また、チップ試作は東京大学大規模集積システム設計教育研究センターを通じ、ローム(株)の協力で行われた。関係各位に感謝いたします。

## 参考文献

pp.21-27

[1] 木村雅秀, Phil Keys, 内田奏, 「巷にあふれる模倣電子部品」, 日経エレクトロニクス, No.2010.04.19, pp.30-50, 2010

[2] B. Gassend, D. Clarke, M. van Dijk, and S. Devadas, "Silicon Physical Random Functions," CCS2002, pp.148-160, 2002.

[3] Jae W. Lee, D. Lim, B. Gassend, G. E. Suh, M. van Dijk, and S. Debadas, "A Technique to Build a Secret Key in Integrated Circuits for Identification and Authentication Applications," In Proceedings of the IEEE VLSI Circuits Symposium, pp.176-179, 2004.

[4] Kota Furuhashi, Mitsuru Shiozaki, Akitaka Fukushima, Takahiko Murayama, Takeshi Fujino, "The Arbiter-PUF with High Uniqueness utilizing Novel Arbiter Circuit with Delay-Time Measurement," ISCAS2011, pp.2325-2328, July 2011 [5] 金成主, "NIST のランダム性評価テストについて," 電子情報通信学会技術報告書 ISEC2003-87(2003-12),