## Development of Three–Dimensionally (3D) Stacked Graphics Processor for Automobile Application

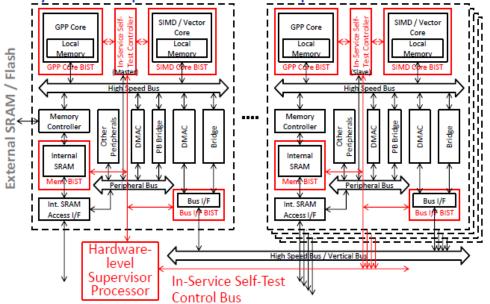

## System level design of 3D-stacked processor System-Level Supervisor Processor Computational Cores

## Specification of 3D-stacked processor

| System Configuration        | 4 stacked layers (1 SVP core + 3 PE cores)                                                                                                                                                                                                              |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Processor<br>Configuration  | SH-4A core+ on-chip memory<br>(Chip size: 5mm × 5mm)                                                                                                                                                                                                    |

| Bus Architecture<br>(64bit) | Super Hyway bus (on-chip)<br>Vertical bus with bus bridge (TSV)                                                                                                                                                                                         |

| Dependability<br>Function   | Self-test and self-repair by SVP, Multiplexed<br>system control (Health data transmission by<br>Heartbeat method), Self-test and self-repair<br>built-in circuits (BIST, ScanPath, Majority circuit,<br>TMR, BISR), TSVs with self-test and self-repair |

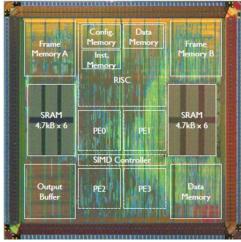

Design, fabrication and evaluation of processor test chip used for optimizing 3D stacking technology

Chip specification: Reconfiguration PE x 4 RISC controller x 1 Frame memory x 2 Output buffer x 1 Data memory x 1

0.13µm CMOS 1 poly/ 8 metal (Cu) 5mm x 5mm 980Kgates

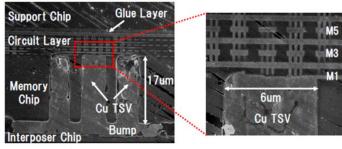

## SEM Cross-sectional view of 3D test chip with Cu-TSVs

TEG chip: 130nm technology node TSV size: diameter 5μm, depth 15μm \*1: SVP (Supervisor Processor) \*2: TSV (Through Si Via)