Development of Dependable Network-on-Chip Platform

Principal Investigator

Tomohiro Yoneda (The National Institute of Informatics / Professor)

Research Theme:

Closeup by click

In order to obtain large and complex VLSI systems using advanced semiconductor process technologies, problems of how to increase utilization of collected many cores and how to tolerate delay variation due to process variation, delay faults caused during operation, changes of environmental parameters, and so on should be solved.

In order to obtain large and complex VLSI systems using advanced semiconductor process technologies, problems of how to increase utilization of collected many cores and how to tolerate delay variation due to process variation, delay faults caused during operation, changes of environmental parameters, and so on should be solved.

This project is developing several core technologies to overcome those problems and proposes a design methodology to construct highly dependable, adaptable, and

efficient network-on-chip (NoC) platform. In order to demonstrate the proposed methodology, a prototype NoC platform is being developed, and almost actual automotive applications are planned to be run on it.

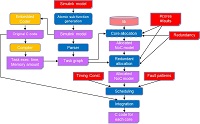

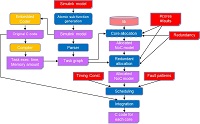

Duplicated task execution with dynamic pair reconfiguration:

For achieving sufficient dependability for automotive applications, two copies of each task are executed in different CPU cores (called a pair), and the results are compared to detect transient/permanent faults. When a mismatch happens, the same task is temporally executed in three CPU cores to find a faulty CPU core. Then, a new pair is reconfigured excluding the faulty CPU core.

Redundant task allocation and redundant scheduling:

Closeup by click

In order to implement the above duplicated task execution with dynamic pair reconfiguration, it is needed

to allocate tasks to CPU cores redundantly, and the scheduling for duplicated execution should be performed. We are now developing a tool that accepts a non-redundant Simulink model and produces the task allocation/scheduling results for a given redundancy of allocation and scheduling.

In order to implement the above duplicated task execution with dynamic pair reconfiguration, it is needed

to allocate tasks to CPU cores redundantly, and the scheduling for duplicated execution should be performed. We are now developing a tool that accepts a non-redundant Simulink model and produces the task allocation/scheduling results for a given redundancy of allocation and scheduling.

|

Open Documents

2008 Program Review (October 2008) (PDF 110kB)

DVLSI Workshop 2008 (December 2008) (PDF 272kB)

2009 Program Review (April 2009) (PDF 110kB)

DVLSI Workshop 2009 (December 2009) (PDF 78kB)

2010 Program Review1 (June 2010) (PDF 260kB)

2010 Program Review2 (October 2010) Prof. Yoneda NII (PDF 122kB)

DVLSI Workshop 2011/3 (March 2011) (PDF 1,590kB)

DVLSI Workshop 2011/12 (December 2011) (PDF 1,469kB)

DVLSI Workshop 2012/6 (June 2012) (PDF 1,018kB) (English document)

DVLSI International Symposium 2012/12 (December 2012) (PDF 1,592kB) (English document)

Annual Reports

2008 Annual Report (PDF 793kB)

2009 Annual Report (PDF 1,191kB)

2010 Annual Report (PDF 1,018kB)

2011 Annual Report (PDF 672kB)