US008295079B2

# (12) United States Patent

# Yamamoto et al.

# (10) Patent No.: US 8,295,079 B2 (45) Date of Patent: Oct. 23, 2012

### (54) NONVOLATILE SRAM/LATCH CIRCUIT USING CURRENT-INDUCED MAGNETIZATION REVERSAL MTJ

(75) Inventors: **Shuichiro Yamamoto**, Kanagawa (JP);

Satoshi Sugahara, Kanagawa (JP)

(73) Assignee: Tokyo Institute of Technology, Tokyo

(JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 284 days.

(21) Appl. No.: 12/674,860

(22) PCT Filed: Jul. 31, 2008

(86) PCT No.: **PCT/JP2008/063787**

§ 371 (c)(1),

(2), (4) Date: Feb. 23, 2010

(87) PCT Pub. No.: WO2009/028298

PCT Pub. Date: Mar. 5, 2009

#### (65) **Prior Publication Data**

US 2011/0273925 A1 Nov. 10, 2011

# (30) Foreign Application Priority Data

| Aug. 31, 2007 | (JP) | <br>2007-225697 |

|---------------|------|-----------------|

| Sep. 3, 2007  | (JP) | <br>2007-227261 |

(51) **Int. Cl.** *G11C 11/00* (2006.01)

(52) **U.S. Cl.** ....... **365/154**; 365/145; 365/158; 365/157;

365/170

See application file for complete search history.

# (56) References Cited

# U.S. PATENT DOCUMENTS

#### FOREIGN PATENT DOCUMENTS

| JP | A-2004-103174     | 4/2004 |

|----|-------------------|--------|

| JP | A-2006-19008      | 1/2006 |

| JP | A-2008-85770      | 4/2008 |

| WO | WO 2004/079827 A1 | 9/2004 |

#### OTHER PUBLICATIONS

Abe et al.; "Novel Nonvolatile Logic Circuits with Three-Dimensionally Stacked Nanoscale Memory Device:" *Technical Proceedings of the 2005 NSTI Nanotechnology Conference and Trade Show*; May 12, 2005; pp. 203-206; vol. 3.

Sugahara; "Spin Transistors for Integrated Spin-electronics;" Journal of the Institute of Electronics; 2005; pp. 541-550; vol. 88; No. 7 (with abstract).

Aug. 26, 2008 International Search Report issued in corresponding International Application No. PCT/JP2008/063787.

Dec. 1, 2009 translation of substantive portion of International Preliminary Report on Patentability issued in corresponding International Application No. PCT/JP2008/063787.

\* cited by examiner

Primary Examiner — Thong Q Le (74) Attorney, Agent, or Firm — Oliff & Berridge, PLC

#### (57) ABSTRACT

The present invention is a memory circuit that includes a bistable circuit that stores data; and a ferromagnetic tunnel junction device that nonvolatilely stores the data stored in the bistable circuit according to a magnetization direction of a ferromagnetic electrode free layer, the data nonvolatilely stored in the ferromagnetic tunnel junction device being able to be restored in the bistable circuit. According to the present invention, writing data to and reading data from the bistable circuit can be performed at high speed. In addition, even though a power source is shut down, it is possible to restore data nonvolatilely stored in the ferromagnetic tunnel junction devices to the bistable circuit.

#### 38 Claims, 81 Drawing Sheets

FIG. 1

FIG. 2

FIG. 3

FIG. 4A

FIG. 4B

FIG. 4C

FIG. 5

FIG. 6A

FIG. 6B

FIG. 7A

FIG. 7B

FIG. 8

FIG. 9A

FIG. 9B

FIG. 9C

FIG. 10

FIG. 11A

FIG. 11B

FIG. 110

FIG. 12

FIG. 13A

FIG. 13B

FIG. 14A  $V_{sp3}$   $V_{Q}=V_{Q}$   $V_{Q}=V_{Q}$

FIG. 14B

F I G.

FIG. 16

FIG. 18

FIG. 20A

FIG. 21A

FIG. 21B

FIG. 22A

F1G. 22B

FIG. 23A

FIG. 23B

FIG. 24

FIG. 25

F1G. 26

FIG. 28

FIG. 30

FIG. 31

FIG. 32

FIG. 34

FIG. 35A

FIG. 36A

Oct. 23, 2012

FIG. 36B

FIG. 37

FIG. 38A

FIG. 38B

FIG. 38C

FIG. 39

FIG. 40A

FIG. 40B

FIG. 41A

FIG. 41B

FIG. 41C

FIG. 41D

16. 4.

FIG. 45

FIG. 47A

FIG. 47B

Oct. 23, 2012

FIG. 48A

FIG. 48B

FIG. 49A

FIG. 49B

FIG. 50A

Oct. 23, 2012

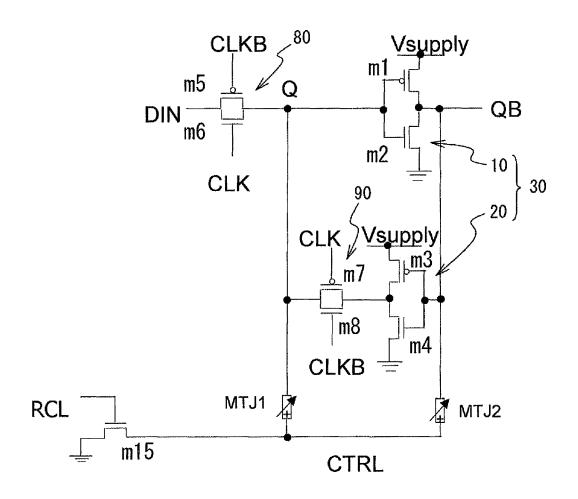

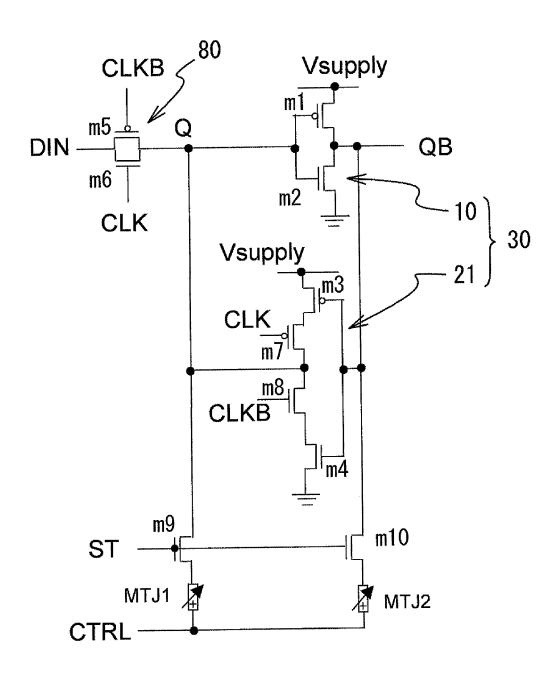

FIG. 50B CLKB Vsupply DIN m5 QB m6 CLK 30 30 Vsupply m7 m8 **m4** CLKB CTRL

FIG. 51

FIG. 52

F16. 53

FIG. 55

FIG. 57

FIG. 58

F1G.

FIG. 60

FIG. 61A

FIG. 61B

FIG. 62

F1G.

# NONVOLATILE SRAM/LATCH CIRCUIT USING CURRENT-INDUCED MAGNETIZATION REVERSAL MTJ

#### TECHNICAL FIELD

The present invention relates to a memory circuit, a latch circuit, and a flip-flop circuit, especially relates to a memory circuit, a latch circuit, and a flip-flop circuit including a bistable circuit and a ferromagnetic tunnel junction device.

## **BACKGROUND ART**

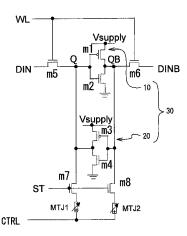

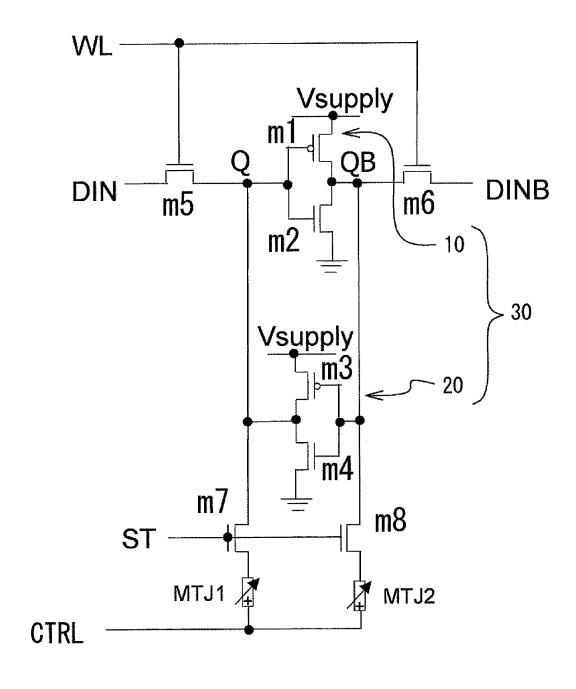

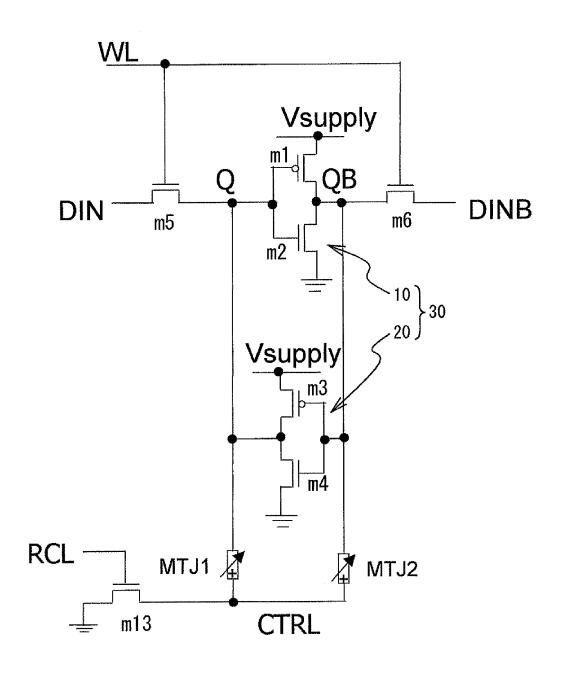

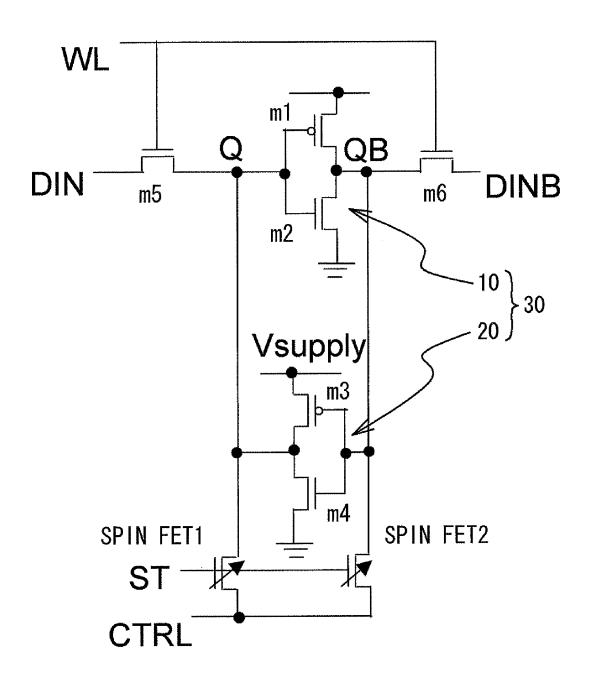

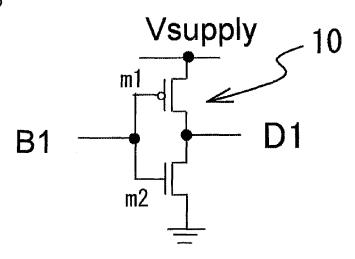

An SRAM (Static Random Access Memory) has been well known as a volatile memory circuit used for an electronic apparatus. FIG. 1 is a circuit diagram illustrating a memory cell of an SRAM using MOS (Metal Oxide Semiconductor) Field Effect Transistor (FET). The memory cell has a bistable circuit 30, two input/output transistors m5 and m6. A CMOS inverter 10 (a first inverter circuit) and a CMOS inverter 20 (a second inverter circuit) are coupled in a ring shape in the bistable circuit 30. The inverter 10 includes a p-type MOS-FET m1 and an n-type MOSFET m2. In the FET m1 and the FET m2, sources are coupled to a power source Vsupply and 25 a ground respectively, gates are commonly-coupled to a node Q, and drains are commonly coupled to a node QB. The inverter 20 includes a p-type MOSFET m3 and an n-type MOSFET m4. In the FET m3 and the FET m4, sources are coupled to a power source V supply and a ground respectively, 30 gates are commonly-coupled to the node QB, and drains are commonly-coupled to the node Q. As described above, the inverter 10 is coupled to the inverter 20 in a ring shape. The node Q is coupled to a data input/output line DIN via an n-type FET m5, and the node QB is coupled to a data input/ 35 output line DINB via an n-type FET m6. Gates of FETs m5 and m6 are coupled to a word line WL.

According to above composition, it is possible to write and hold data in the bistable circuit 30, and read data from the bistable circuit 30. However, an SRAM consumes power 40 while holding data. In addition, when the power source is shut down, data stored in the bistable circuit 30 is lost. Since the bistable circuit 30 has a symmetrical structure, and symmetrically-operates, once nodes Q and QB have the same potential after the power source is shut down, it is impossible to restore 45 data even though the power source is restored. This is because potentials of nodes Q and QB remain at the same potential and data is determined by external noise and the like at certain timing regardless of the data stored before the power source is shut down when the power source is restored.

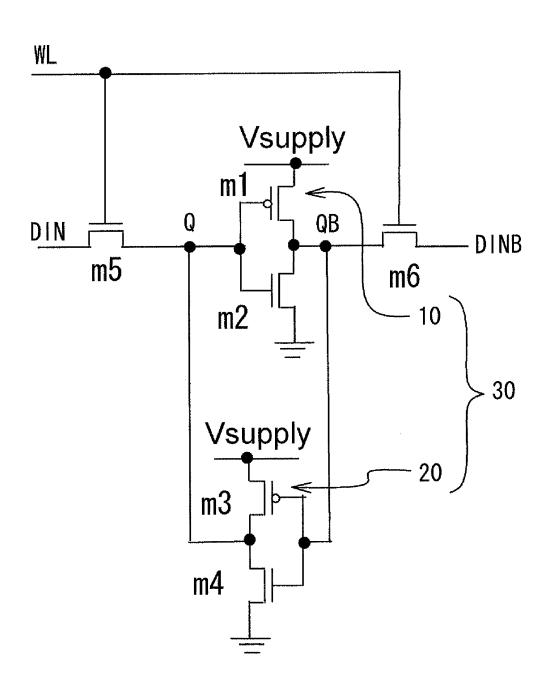

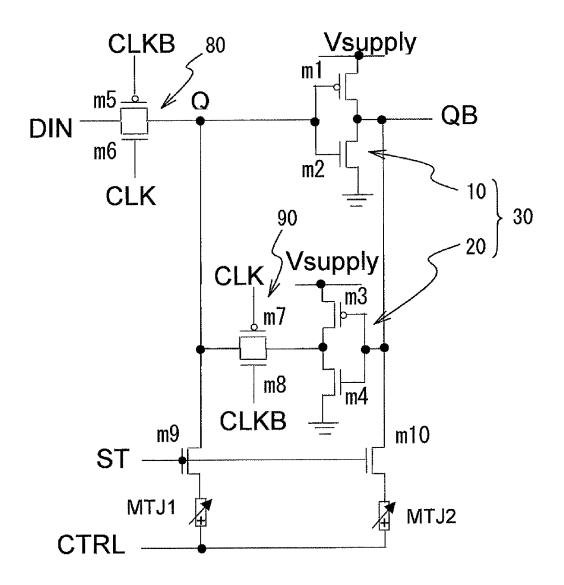

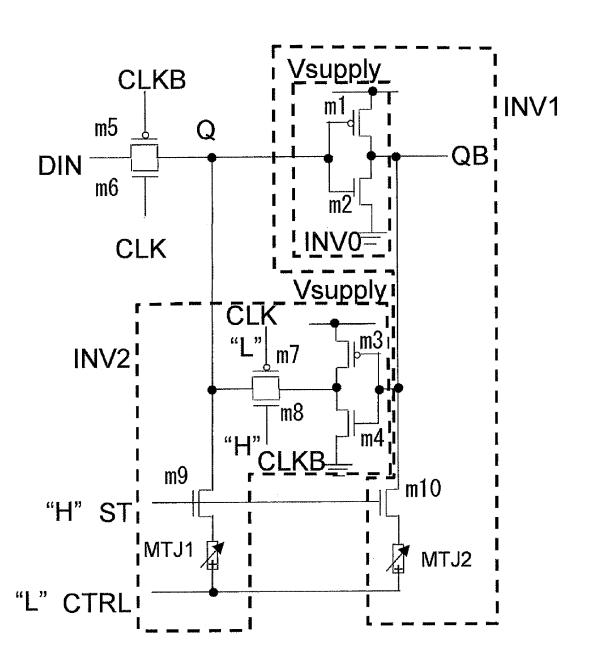

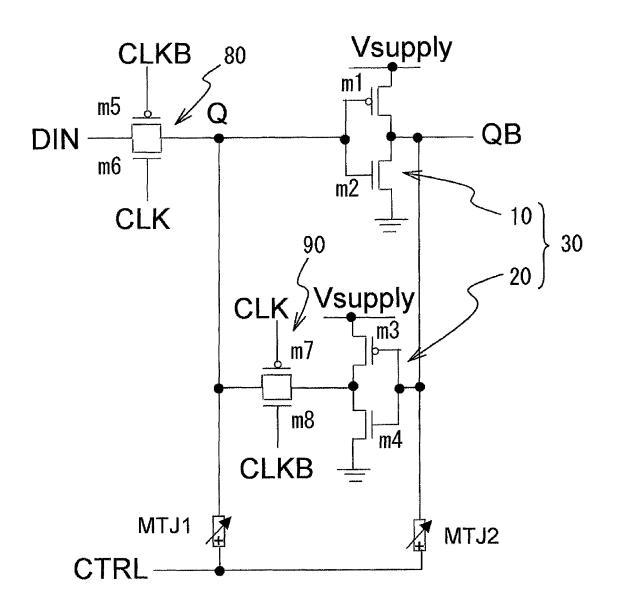

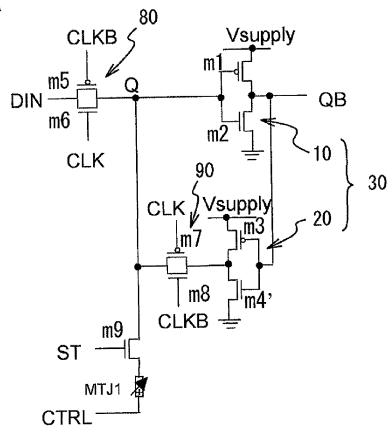

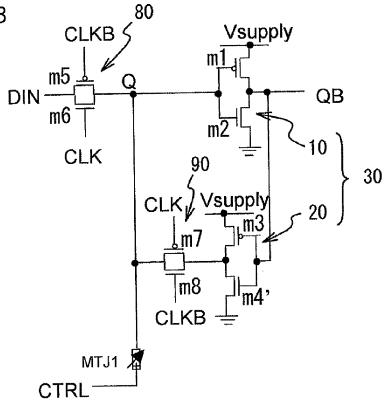

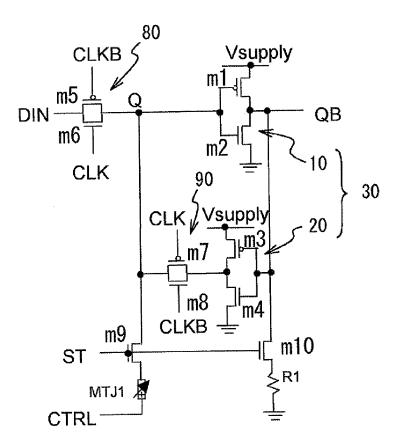

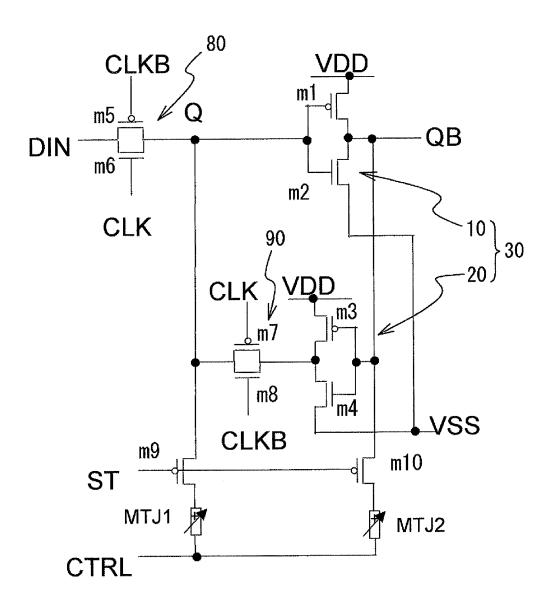

A volatile latch circuit used for an electronic apparatus is well known. FIG. 2 is a circuit diagram illustrating a D latch circuit using a MOS (Metal Oxide Semiconductor) Field Effect Transistor (FET) as an example of a latch circuit. The D latch circuit includes the bistable circuit 30, and pass gates 55 80 and 90. The CMOS inverter 10 (the first inverter circuit) and the CMOS inverter 20 (the second inverter circuit) are coupled to the bistable circuit 30 via the pass gate 90 in a ring shape. The inverter 10 includes the p-type MOSFET m1 and the n-type MOSFET m2. In the FET m1 and FET m2, sources 60 are coupled to the power source Vsupply and ground respectively, gates are commonly-coupled to the node Q, and drains are commonly-coupled to the node QB. The inverter 20 includes the p-type MOSFET m3 and the n-type MOSFET m4. In the FET m3 and the FET m4, sources are coupled to the 65 power source Vsupply and a ground respectively, gates are commonly-coupled to the node QB, and drains are com2

monly-coupled to the node Q via the pass gate 90. As described above, the inverter 10 is coupled to the inverter 20 in a ring shape.

The pass gate 80 (a first input switch) is coupled between the input line DIN and the node Q. The pass gate 80 includes the p-type MOSFET m5 and the n-type MOSFET m6. The source and drain of the FET m5 are coupled to the source and drain of the FET m6 respectively. An inverted clock signal CLKB is input to the gate of the FET m5, and a clock signal CLK is input to the gate of the FET m6. When the clock signal CLK at a high level is input, both FETs m5 and m6 become conductive, and the pass gate 80 becomes conductive. The pass gate 90 (a second input switch) is coupled between the node Q and the inverter 20. The pass gate 90 includes a p-type MOSFET m7 and an n-type MOSFET m8. The clock signal CLK is input to the gate of the FET m7, and the inverted clock signal CLKB is input to the gate of the FET m8. When the clock signal CLK at a low level is input, both FETs m7 and m8 become conductive, and the pass gate 90 becomes conductive. Other connections and behavior are same as the pass gate

According to above composition, when the clock signal CLK is at a high level, the pass gate 80 becomes conductive, and the pass gate 90 becomes non-conductive. This makes data of the input line DIN written in the bistable circuit 30. When the clock signal CLK is at a low level, the pass gate 80 becomes non-conductive, and the pass gate 90 becomes conductive. This makes the bistable circuit 30 hold data. The data stored in the bistable circuit 30 can be output from the node Q or QB. A volatile D latch circuit consumes power while holding data. In addition, if the power source is shut down, the data stored in the bistable circuit 30 is lost. The bistable circuit 30 does not function as a bistable circuit when the pass gate 90 is non-conductive, but on the other hand, as the pass gate 80 is conductive, the data of the input line DIN is written in the node Q and the logic-inverted data of the node Q is written in the node QB. Therefore, the data of nodes Q and QB are determined regardless of the data stored before the power source is shut down. Since the bistable circuit 30 has a symmetrical structure where inputs and outputs of the inverter 10 and the inverter 20 are coupled each other and symmetricallyoperates in a condition that the pass gate 90 is conductive, once nodes Q and QB have the same potential after the power source is shut down, it is impossible to restore the data even though the power source is restored. This is because potentials of nodes Q and QB remain at the same potential and data is determined by external noise and the like at certain timing regardless of the data stored before the power source is shut down when the power source is restored.

A flash memory, an MRAM (Magnetic Random Access Memory), an FeRAM (Ferroelectric Random Access Memory), a PRAM (Phase-change Random Access Memory) and the like are known as a nonvolatile memory circuit where data is not lost even though a power source is shut down. Since data is not lost in these memory circuits even though a power source is shut down, the data can be read out when the power source is restored after that.

Patent Reference 1 discloses an MRAM where ferromagnetic tunnel junction devices are coupled to each of complementary nodes of a latch circuit.

[Patent Reference 1] Japanese Patent Application Publication No. 2006-19008

## DISCLOSURE OF THE INVENTION

# Problems to be Solved by the Invention

An SRAM can write and read data at high speed. On the other hand, a speed of writing and reading data of a flash

memory, an MRAM, an FeRAM, a PRAM and the like is slow. As described above, an SRAM operates at high speed, but data is lost when a power source is shut down. On the other hand, a conventional nonvolatile memory holds data even though a power source is shut down, but has difficulties in a 5 high-speed operation.

An SRAM consumes power because of a leak current during the data-holding-condition (standby condition) which is a condition that a data access is not in progress. If a nonvolatile SRAM can be fabricated, it is possible to achieve both the reduction of power consumption during the standby condition and high speed data-read/write operations.

In addition, as illustrated in FIG. 2, a latch circuit using a CMOS can write data at high speed, and output data by driving an output line at any time. On the other hand, a 15 nonvolatile memory such as a flash memory, an MRAM, an FeRAM, a PRAM writes and reads data at low speed. Furthermore, an operation to extract data from a memory element to an external output line (a readout operation) is necessary. tages of being able to operate at high speed and being able to drive the output line while a power source is supplied, but data is lost when the power source is shut down. On the other hand, a conventional nonvolatile memory holds data even though a power source is shut down, but has difficulties in a high-speed 25 operation. Furthermore, an operation to extract data from a memory element to an external output line (a readout operation) is necessary.

The latch circuit consumes power because of a leak current during a data-holding-condition (standby condition) which is 30 a condition that the pass gate 80 which is a data input gate is non-conductive. If a nonvolatile latch circuit can be fabricated, it is possible to achieve all advantages, that are a reduction of power consumption during the standby condition, a high speed data-write/read operation, and a capability of out- 35 putting data by driving the output line whenever a power source is supplied.

The present invention is made in views of above problems, and the aim of the present invention is to provide a memory circuit, a latch circuit, and a flip-flop circuit that can operate at 40 high speed, and can read out data stored before a power source is shut down when the power source is restored after the power source is shut down.

# Means for Solving the Problems

The present invention is a memory circuit that includes a bistable circuit that stores data; and a ferromagnetic tunnel junction device that nonvolatilely stores the data stored in the bistable circuit according to a magnetization direction of a 50 ferromagnetic electrode free layer, the data nonvolatilely stored in the ferromagnetic tunnel junction device being able to be restored to the bistable circuit. According to the present invention, data writing to and data reading from the bistable circuit can be performed at high speed. In addition, even 55 though a power source is shut down, data nonvolatilely stored in the ferromagnetic tunnel junction device can be restored to the bistable circuit. Even though a power source is recovered after a power source is shut down, it is possible to data stored before the power source is shut down can be read out. There- 60 fore, power consumption of the memory circuit can be reduced by shutting down a power source in a standby condition.

In the above composition, the ferromagnetic tunnel junction device may change the magnetization direction of the 65 ferromagnetic electrode free layer by a current-induced magnetization reversal method.

In the above composition, a first inverter circuit and a second inverter circuit may be coupled in a ring shape in the bistable circuit, and the ferromagnetic tunnel junction device may be coupled to a node to which the first inverter circuit and the second inverter circuit are coupled.

In the above composition, the ferromagnetic tunnel junction device may be coupled between the node and a control line, and become a high resistance as a current flows between the node and the control line, and become a low resistance as a current flows to a counter direction of the current. According to this composition, data can be stored in the ferromagnetic tunnel junction device.

In the above composition, the control line may apply a high level voltage to the ferromagnetic tunnel junction device and further apply a low level voltage when storing the data from the bistable circuit to the ferromagnetic tunnel junction device. According to this composition, data can be stored in the ferromagnetic tunnel junction device.

In the above composition, the control line may apply a low As described above, the latch circuit using CMOS has advan- 20 level or high level voltage to the ferromagnetic tunnel junction device when restoring the data from the ferromagnetic tunnel junction device to the bistable circuit. According to this composition, the data can be restored to the bistable circuit.

> In the above composition, the memory circuit may include a switch that is coupled between the node and the ferromagnetic tunnel junction device, and that becomes conductive when storing the data from the bistable circuit to the ferromagnetic tunnel junction device or when restoring the data from the ferromagnetic tunnel junction device to the bistable circuit. According to this composition, power consumption can be reduced with the switch.

> In the above composition, the switch may include a MOS-FET. According to this composition, the switch can be composed easily.

> In the above composition, the node may include a first node and a second node that are complementary nodes to one another, and the ferromagnetic tunnel junction device may include a first ferromagnetic tunnel junction device which is coupled between the first node and the control line, and a second ferromagnetic tunnel junction device which is coupled between the second node and the control line.

In the above composition, the memory circuit may include a first switch that is provided between the first node and the 45 first ferromagnetic tunnel junction device, and that becomes conductive when storing the data from the bistable circuit to the first ferromagnetic tunnel junction device or when restoring the data from the first tunneling junction device to the bistable circuit; and a second switch that is provided between the second node and the second ferromagnetic tunnel junction device, and that becomes conductive when storing the data from the second ferromagnetic tunnel junction device to the bistable circuit or when restoring the data from the second ferromagnetic tunnel junction device to the bistable circuit. According to this composition, power consumption can be reduced with the first switch and the second switch.

In the above composition, the first switch and the second switch may include a MOSFET respectively. According to this composition, the first switch and the second switch can be composed easily.

In the above composition, the memory circuit may include a third switch that is coupled between the control line and an electric power line which is at a low level or at a high level, the third switch becoming non-conductive when storing the data from the bistable circuit to the first ferromagnetic tunnel junction device and the second ferromagnetic tunnel junction device, and becoming conductive when restoring the data

from the first ferromagnetic tunnel junction device and the second ferromagnetic tunnel junction device to the bistable circuit. According to this composition, high-speed operations become possible.

In the above composition, the memory circuit may include 5 an input/output switch for inputting and outputting data to the node.

In the above composition, the input/output switch may input and output data to the node according a level of a word line.

In the above composition, the input/output switch may include a first input/output switch for inputting and outputting data to the first node, and a second input/output switch for inputting and outputting data to the second node.

In the above composition, the first inverter circuit and the 15 second inverter circuit may be inverter circuits.

In the above composition, the ferromagnetic tunnel junction device may include a ferromagnetic electrode free layer, a ferromagnetic electrode pinned layer, and a tunnel insulation film that is provided between the ferromagnetic electrode 20 free layer and the ferromagnetic electrode pinned layer.

The present invention is a latch circuit that includes a bistable circuit that includes a first logic circuit having one or more inputs and one or more outputs and a second logic circuit having one or more inputs and one or more outputs, 25 and stores data; a first node to which one of outputs of the first logic circuit and one of inputs of the second logic circuit are coupled; a second node to which one of outputs of the second logic circuit and one of inputs of the first logic circuit are coupled; and a ferromagnetic tunnel junction device that is 30 coupled to at least one of the first node and the second node, and nonvolatilely stores data stored in the bistable circuit according to a magnetization direction of a ferromagnetic electrode free layer, complementary data to be stored being output from the first logic circuit and the second logic circuit 35 to the first node and the second node respectively when storing the data from the bistable circuit to the ferromagnetic tunnel junction device, a signal that has the first logic circuit output a logic inversion of the second node to the first node being output to inputs except an input which is coupled to the 40 second node of the first logic circuit, and a signal that has the second logic circuit output a logic inversion of the first node to the second node being output to inputs except an input which is coupled to the first node of the second logic circuit when restoring the data from the ferromagnetic tunnel junc- 45 tion device to the bistable circuit. According to the present invention, data writing to and data outputting to the bistable circuit can be performed at high speed, and the output line can be always driven while a power source is supplied. In addition, even though a power source is shut down, data nonvola- 50 tilely stored in the ferromagnetic tunnel junction device can be restored to the bistable circuit. Thus, even though a power source is recovered after the power source is shut down, data before the power source is shut down can be output. Therefore, in a standby condition, by shutting down a power source, 55 power consumption of the latch circuit can be reduced.

The present invention is a latch circuit that includes a bistable circuit that stores data, and where a first inverter circuit and a second inverter circuit are coupled in a ring shape; a first node and a second node to which the first inverter 60 circuit and the second inverter circuit are coupled, and that are a complementary node to one another; a first input switch for writing the data to the bistable circuit from an input line; a second input switch that behaves in a complementary style to the first input switch, and holds data of the bistable circuit; 65 and a ferromagnetic tunnel junction device that nonvolatilely stores data stored in the bistable circuit according to a mag-

6

netization direction of a ferromagnetic electrode free layer, data nonvolatilely stored in the ferromagnetic tunnel junction device being able to restored to the bistable circuit. According to the present invention, data writing to and data outputting to the bistable circuit can be performed at high speed. In addition, even though a power source is shut down, data nonvolatilely stored in the ferromagnetic tunnel junction device can be restored to the bistable circuit. Thus, even though a power source is recovered after the power source is shut down, data before the power source is shut down can be output. Therefore, in a standby condition, by shutting down a power source, power consumption of the latch circuit can be reduced.

In the above composition, the ferromagnetic tunnel junction device may change the magnetization direction of the ferromagnetic electrode free layer by a current-induced magnetization reversal method.

In the above composition, the ferromagnetic tunnel junction device may be coupled to at least one node of the first node and the second node.

In the above composition, the ferromagnetic tunnel junction device may be coupled between the at least one node and a control line, become a high resistance as a current flows between the at least one node and the control line, and become a low resistance as a current flows to a counter direction of the current. According to this composition, data can be stored to the ferromagnetic tunnel junction device.

In the above composition, the control line may apply a high level voltage to the ferromagnetic tunnel junction device, and further apply a low level voltage when storing the data from the bistable circuit to the ferromagnetic tunnel junction device. According to this composition, data can be stored to the ferromagnetic tunnel junction device.

In the above composition, the control line may apply a low level or high level voltage to the ferromagnetic tunnel junction device when restoring the data from the ferromagnetic tunnel junction device to the bistable circuit. According to this composition, data can be restored to the bistable circuit.

In the above composition, the latch circuit may include a switch that is coupled between the at least one node and the ferromagnetic tunnel junction device, and becomes conductive when storing the data from the bistable circuit to the ferromagnetic tunnel junction device or when restoring the data from the ferromagnetic tunnel junction device to the bistable circuit. According to this composition, power consumption can be reduced with the switch.

In the above composition, the switch may include a MOS-FET. According to this composition, the switch is easily composed.

In the above composition, the ferromagnetic tunnel junction device may include a first ferromagnetic tunnel junction device that is coupled between the first node and the control line, and a second ferromagnetic tunnel junction device that is coupled between the second node and the control line. According to this composition, more stable operations are achieved with the first ferromagnetic tunnel junction device and the second ferromagnetic tunnel junction device.

In the above composition, the latch circuit may include a first switch that is provided between the first node and the first ferromagnetic tunnel junction device, and becomes conductive when storing the data from the bistable circuit to the first ferromagnetic tunnel junction device or when restoring the data from the first ferromagnetic tunnel junction device to the bistable circuit; and a second switch that is provided between the second node and the second ferromagnetic tunnel junction device, and becomes conductive when storing the data to the second ferromagnetic tunnel junction device or when restor-

ing the data to the bistable circuit. According to this composition, power consumption is reduced by the first switch and the second switch.

In the above composition, the first switch and the second switch may include a MOSFET respectively. According to 5 this composition, the first switch and the second switch are easily composed.

In the above composition, the latch circuit may include a third switch that is coupled between the control line and an electric power line which is at a low level or at a high level, the third switch becoming non-conductive when storing the data from the bistable circuit to the first ferromagnetic tunnel junction device and the second ferromagnetic tunnel junction device, and becoming conductive when restoring the data from the first ferromagnetic tunnel junction device and the second ferromagnetic tunnel junction device to the bistable circuit. According to this composition, high-speed operations can be achieved.

In the above composition, the ferromagnetic tunnel junc- 20 tion device may include a ferromagnetic electrode free layer, a ferromagnetic electrode pinned layer, and a tunnel insulation film provided between the ferromagnetic electrode free layer and the ferromagnetic electrode pinned layer.

## Effects of the Invention

According to the present invention, it is possible to write data in and read out data from the bistable circuit at high speed. In addition, even though a power source is shut down, 30 it is possible to restore data nonvolatilely stored in a ferromagnetic tunnel junction device to the bistable circuit. Therefore, it becomes possible to read out data stored before a power source is shut down even though the power source is restored after the power source is shut down.

# BRIEF DESCRIPTION OF THE DRAWINGS

- FIG. 1 is a circuit diagram of a memory circuit used for an

- FIG. 2 is a circuit diagram of a latch circuit used for an integrated circuit;

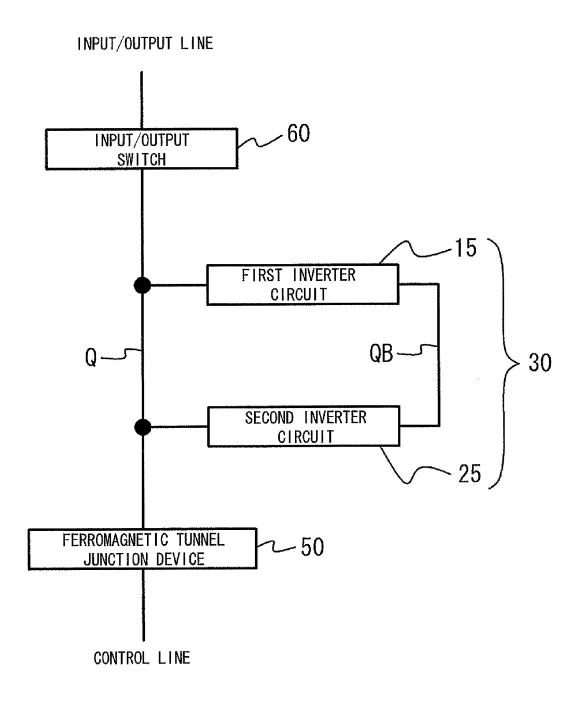

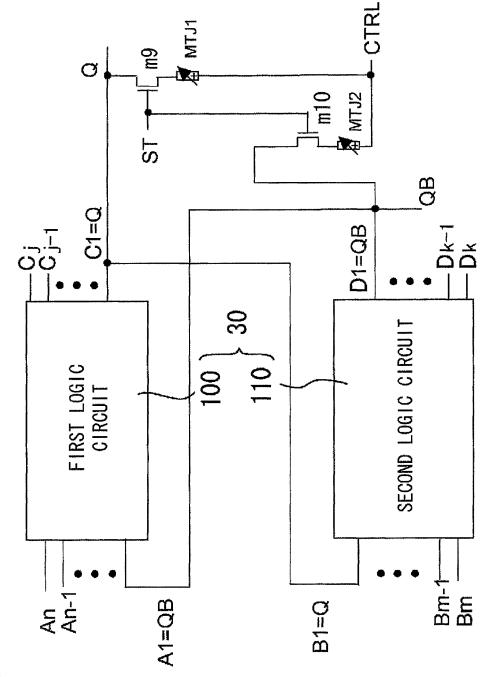

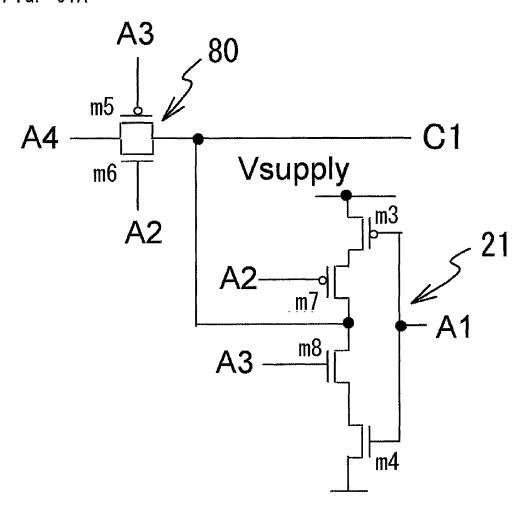

- FIG. 3 is a block diagram of a memory circuit in accordance with a first embodiment;

- FIG. 4A through FIG. 4C are diagrams to describe a fer- 45 output characteristics of an inverter; romagnetic tunnel junction device;

- FIG. 5 is a circuit diagram of a memory circuit in accordance with a second embodiment;

- FIG. 6A and FIG. 6B are diagrams (No. 1) to describe a data store;

- FIG. 7A and FIG. 7B are diagrams (No. 2) to describe a

- FIG. 8 is a diagram (No. 1) to describe a data restoration; FIG. 9A through FIG. 9C are diagrams (No. 2) to describe

- a data restoration; FIG. 10 is a diagram (NO. 3) to describe a data restoration;

- FIG. 11A through FIG. 11C are diagrams (No. 4) to describe a data restoration;

- FIG. 12 is a diagram illustrating INV1 and INV2;

- FIG. 13A and FIG. 13B are diagrams illustrating input/ 60 output characteristics of an inverter;

- FIG. 14A through FIG. 14D are diagrams (No. 5) to describe a data restoration;

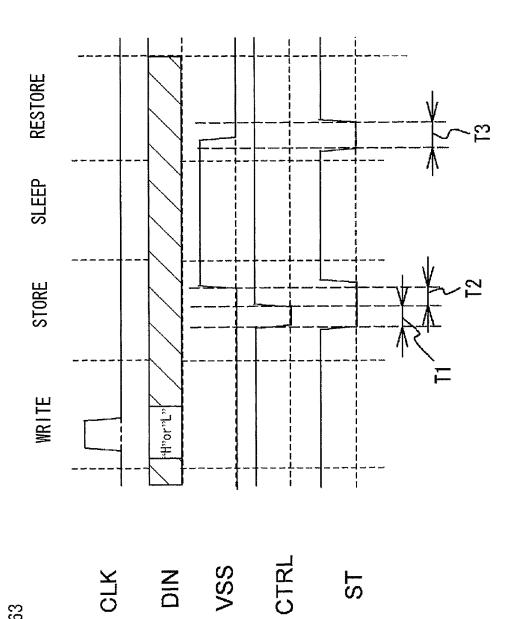

- FIG. 15 is a timing diagram of a second embodiment;

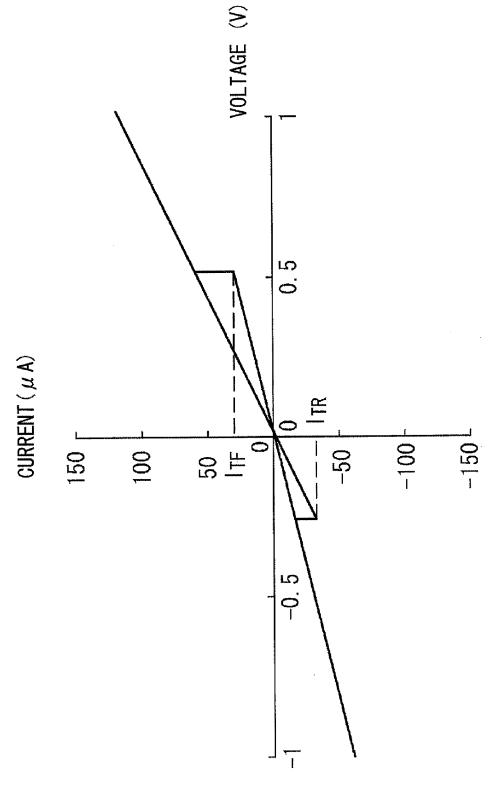

- FIG. 16 is a diagram illustrating current-voltage character- 65 istics of the ferromagnetic tunnel junction device used for a simulation;

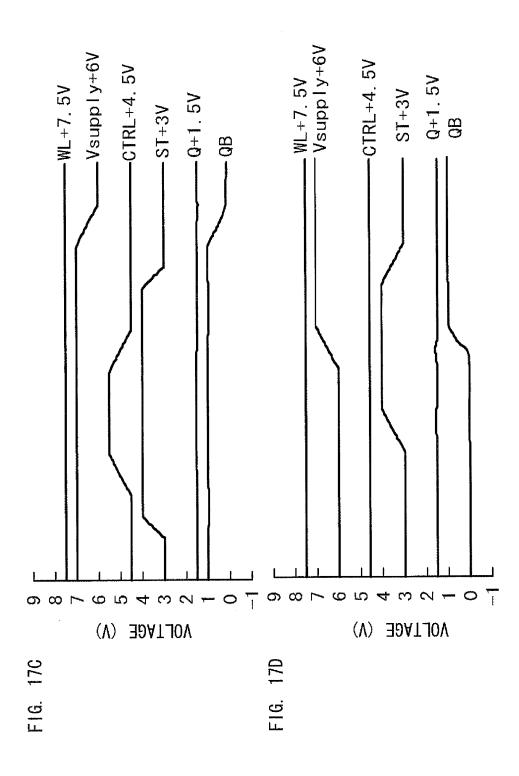

- FIG. 17A through FIG. 17D are diagrams illustrating simulation results of the second embodiment;

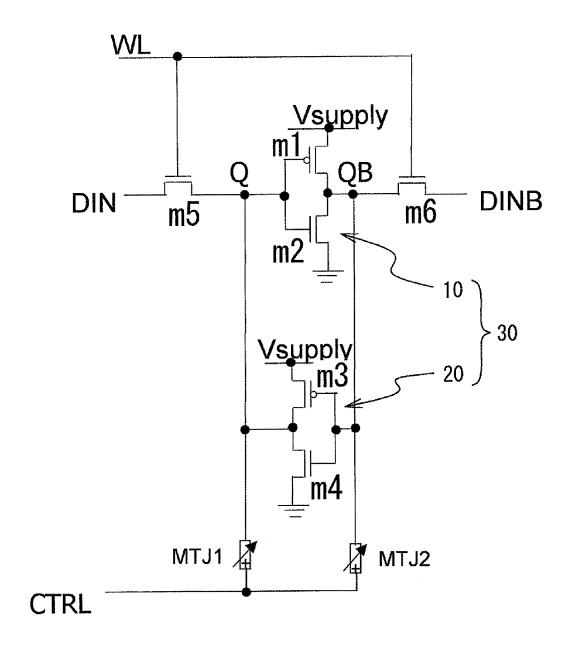

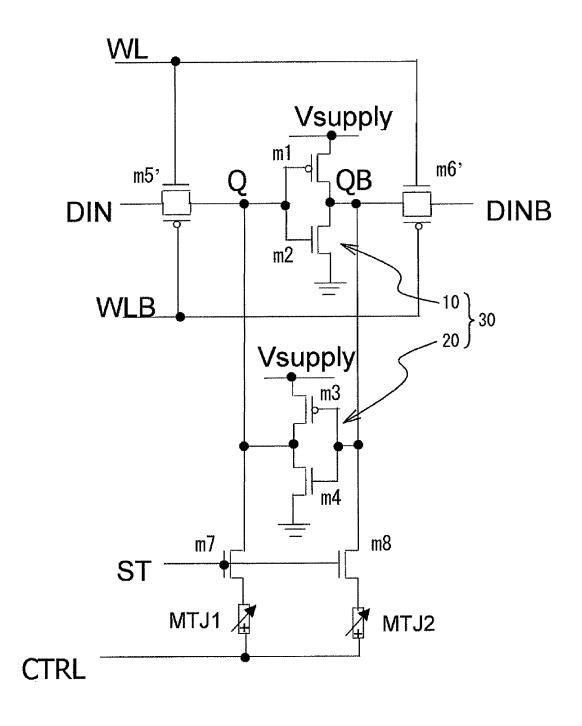

- FIG. 18 is a circuit diagram of a memory circuit in accordance with a third embodiment:

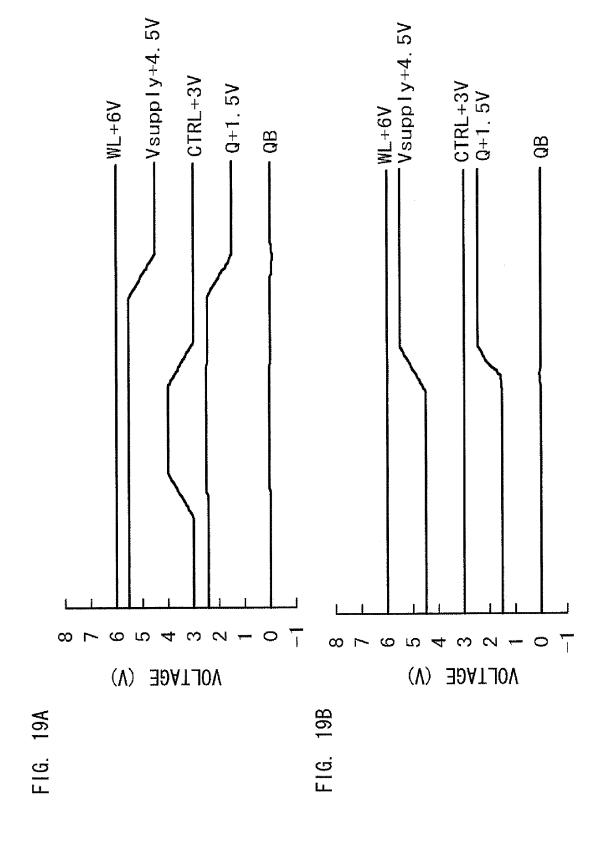

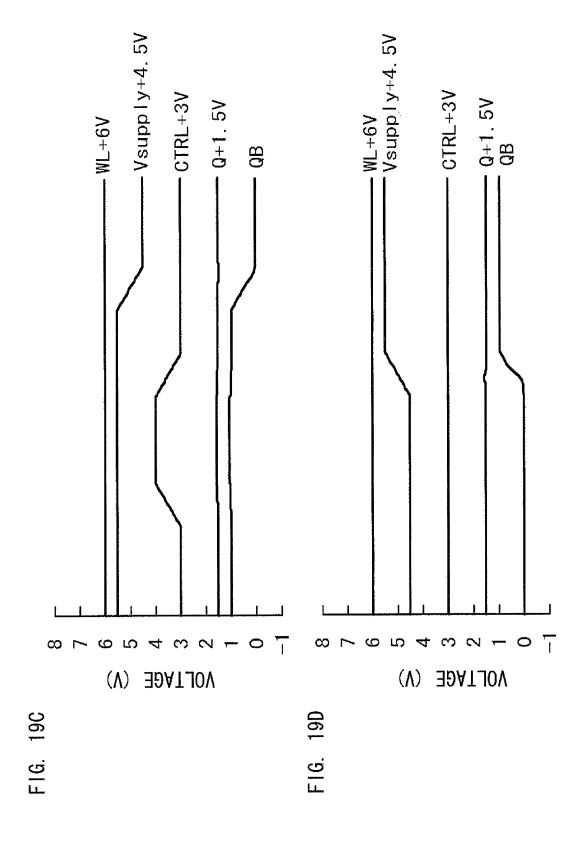

- FIG. 19A through FIG. 19D are diagrams (No. 1) illustrating simulation results of the third embodiment;

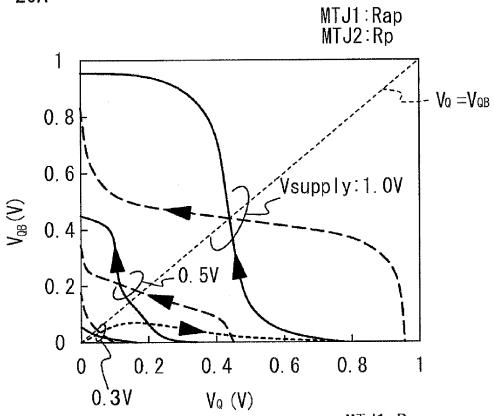

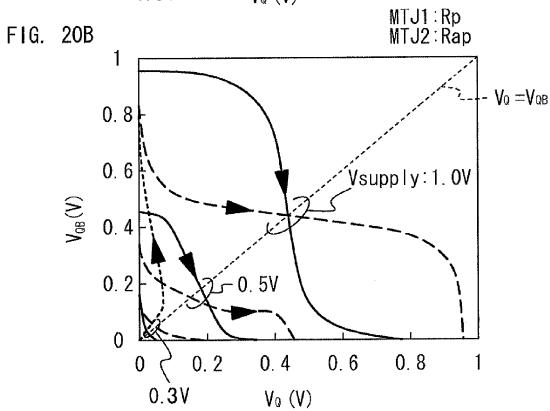

- FIG. 20A and FIG. 20B are diagrams (No. 2) illustrating simulation results of the third embodiment;

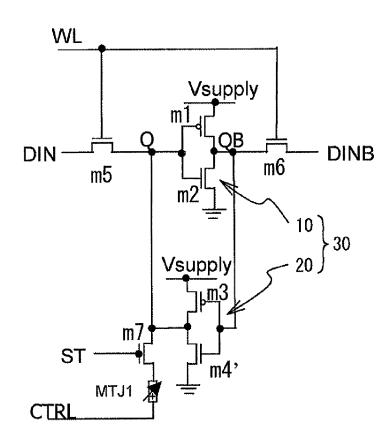

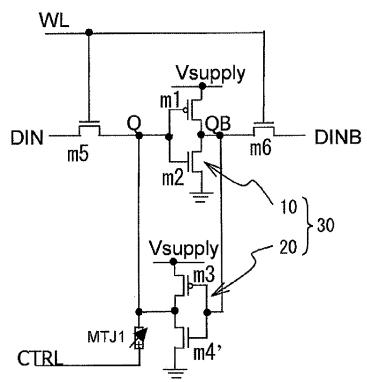

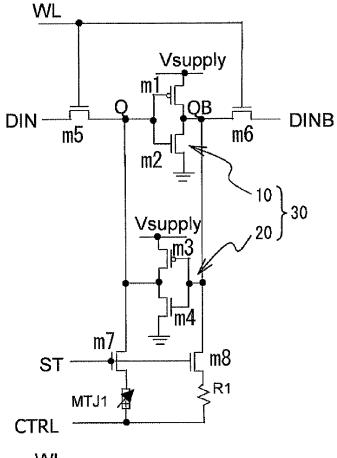

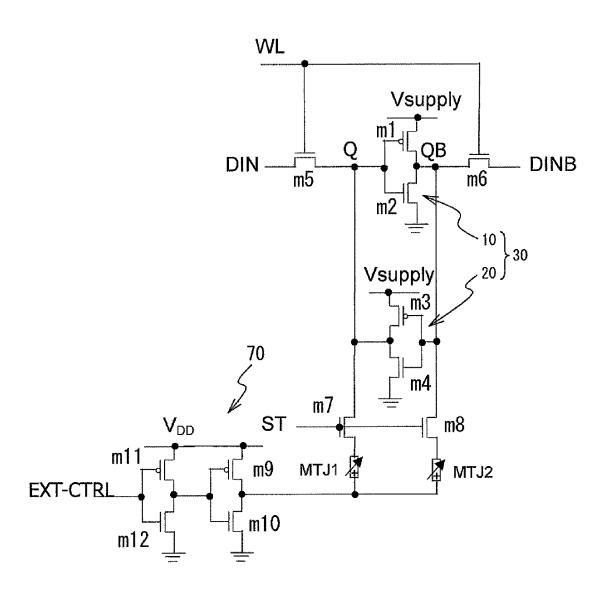

- FIG. 21A and FIG. 21B is circuit diagrams of a memory circuit in accordance with a fourth embodiment;

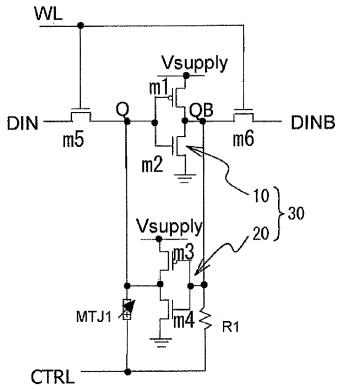

- FIG. 22A and FIG. 22B are circuit diagrams of a memory circuit in accordance with a fifth embodiment;

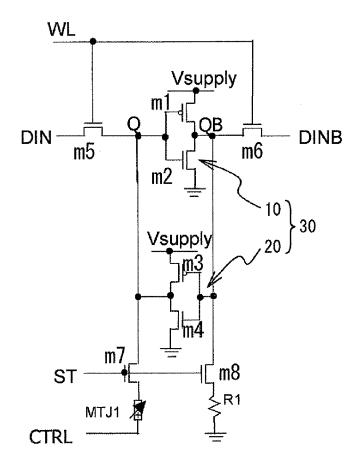

- FIG. 23A and FIG. 23B are circuit diagrams of a memory circuit in accordance with a sixth embodiment;

- FIG. 24 is a circuit diagram of a memory circuit in accordance with a seventh embodiment;

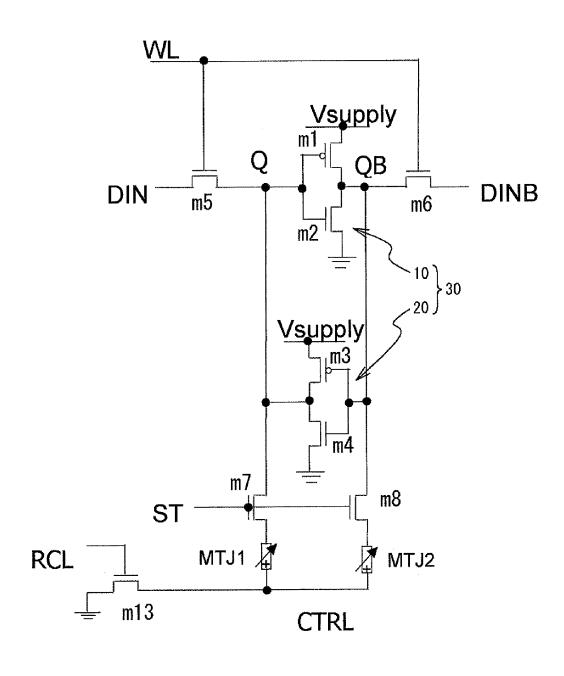

- FIG. 25 is a circuit diagram of a memory circuit in accordance with an eighth embodiment;

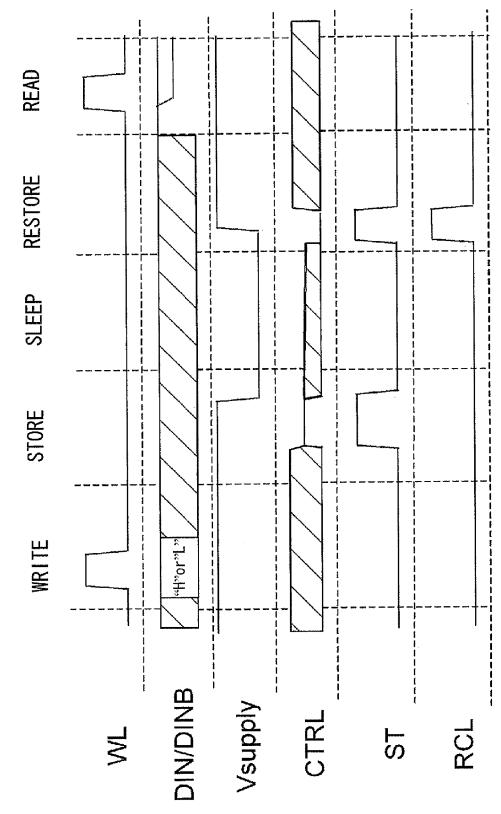

- FIG. **26** is a timing diagram of the eighth embodiment;

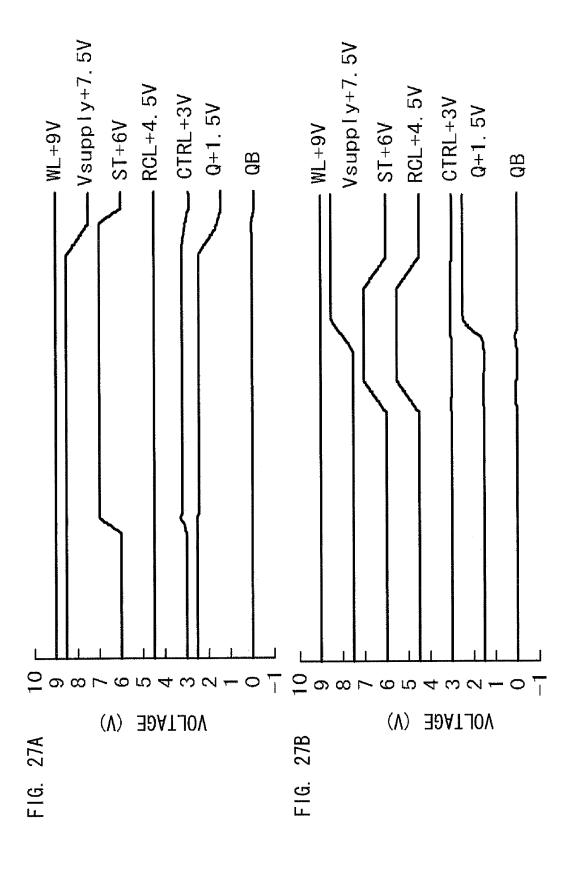

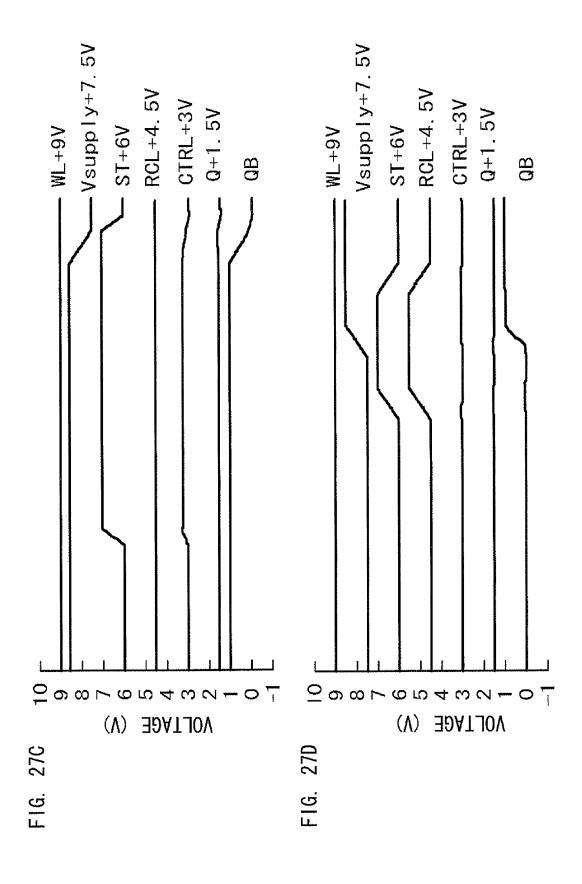

- FIG. 27A through FIG. 27D are diagrams illustrating simulation results of the eighth embodiment;

- FIG. 28 is a circuit diagram of a memory circuit in accordance with a ninth embodiment;

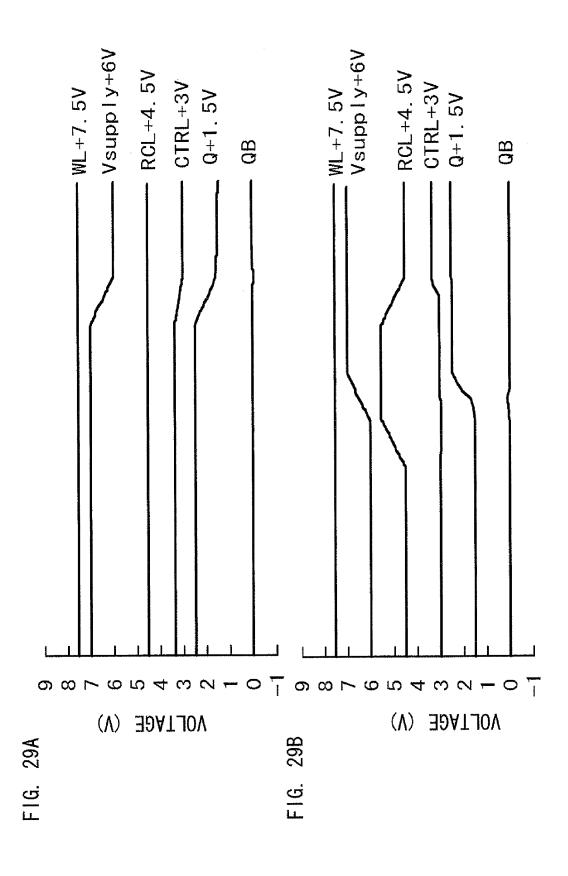

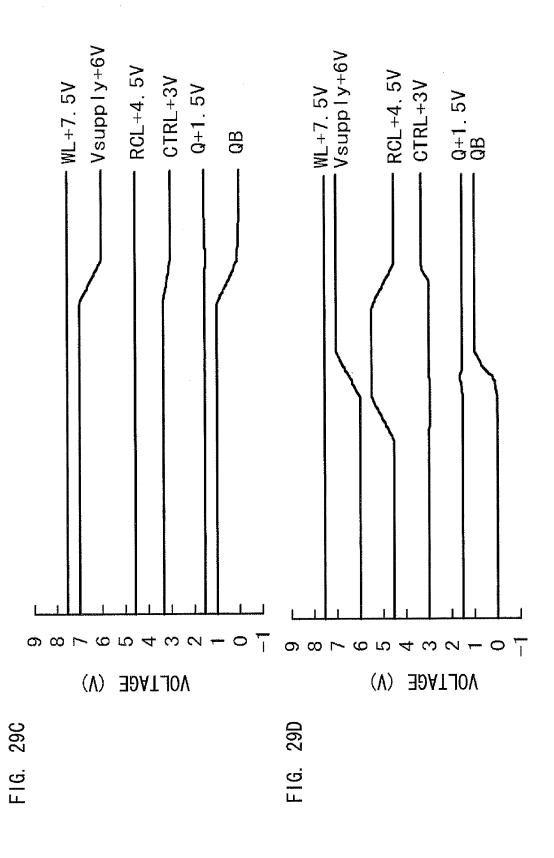

- FIG. 29A through FIG. 29D are diagrams illustrating simulation results of the ninth embodiment;

- FIG. 30 is a circuit diagram of a memory circuit in accordance with a tenth embodiment;

- FIG. 31 is a circuit diagram of a memory circuit in accordance with an eleventh embodiment;

- FIG. 32 is a circuit diagram of a memory circuit in accordance with a twelfth embodiment;

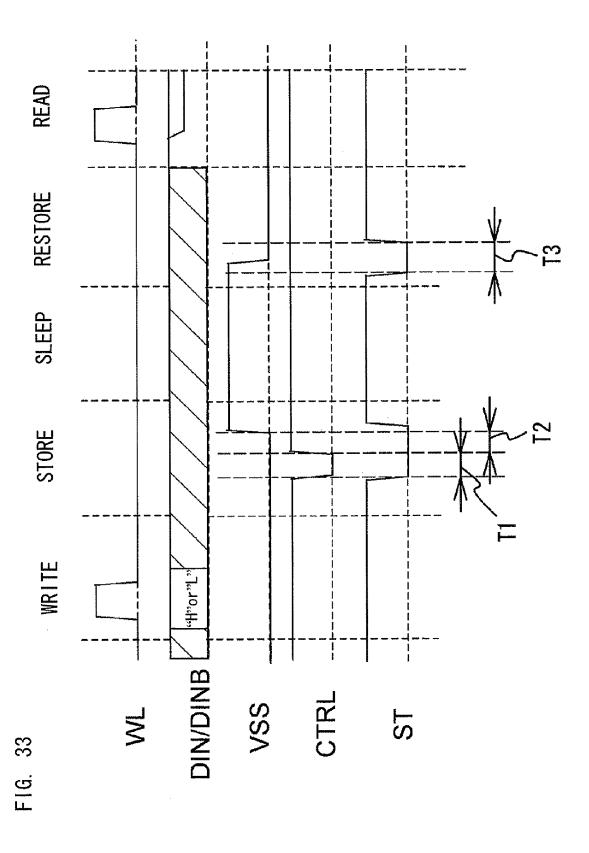

- FIG. 33 is a timing diagram of the twelfth embodiment;

- FIG. 34 is a circuit diagram of a latch circuit in accordance 35 with a thirteenth embodiment;

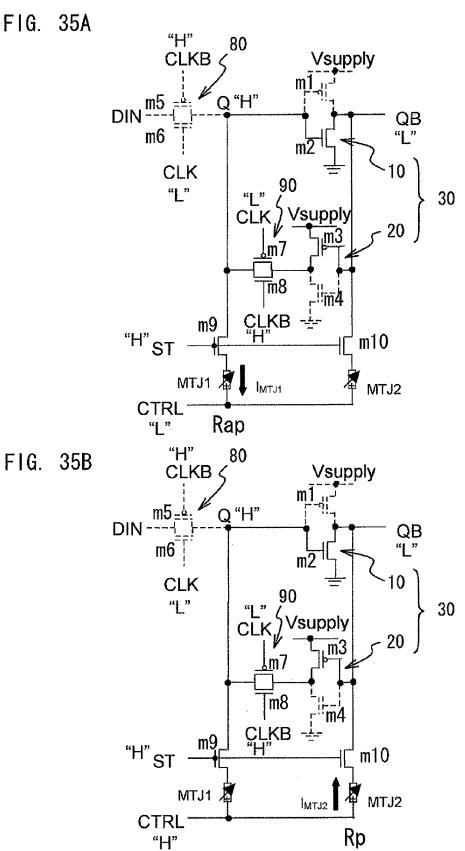

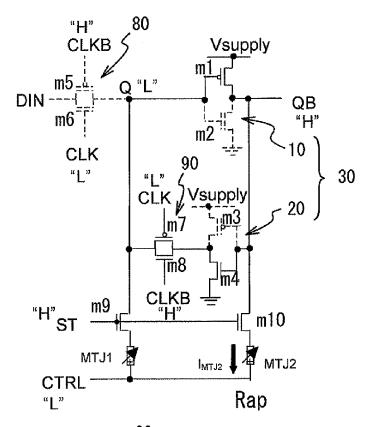

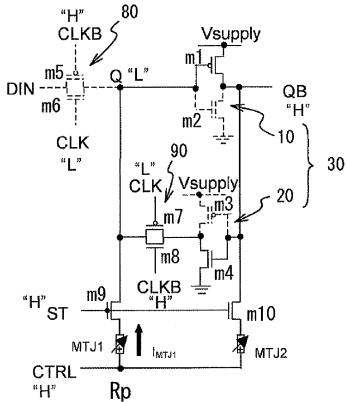

- FIG. 35A and FIG. 35B are diagrams (No. 1) to describe a data store;

- FIG. 36A and FIG. 36B are diagrams (No. 2) to describe a data store:

- FIG. 37 is a diagram (No. 1) to describe a data restoration; FIG. 38A through FIG. 38C are diagrams (No. 2) to

- describe a data restoration; FIG. 39 is a diagram illustrating INV1 and INV2;

- FIG. 40A and FIG. 40B are diagrams illustrating input/

- FIG. 41A through FIG. 41D are diagrams (No. 3) to describe a data restoration:

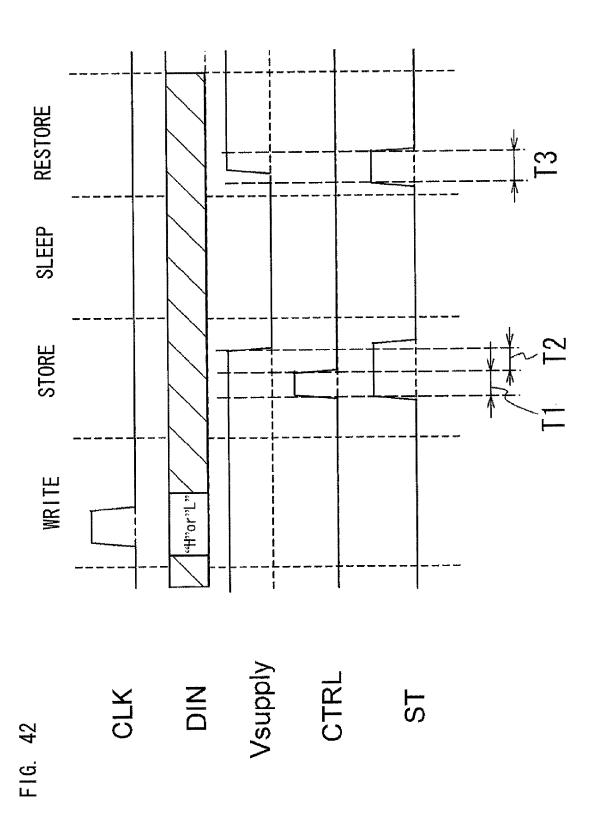

- FIG. 42 is a timing diagram of the thirteenth embodiment;

- FIG. 43 is a diagram illustrating current-voltage character-50 istics of a ferromagnetic tunnel junction device used for a simulation:

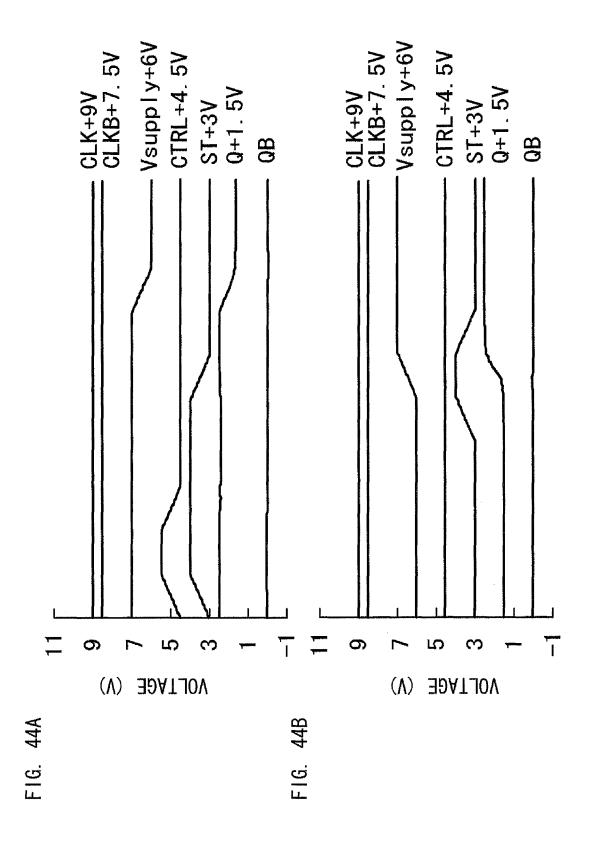

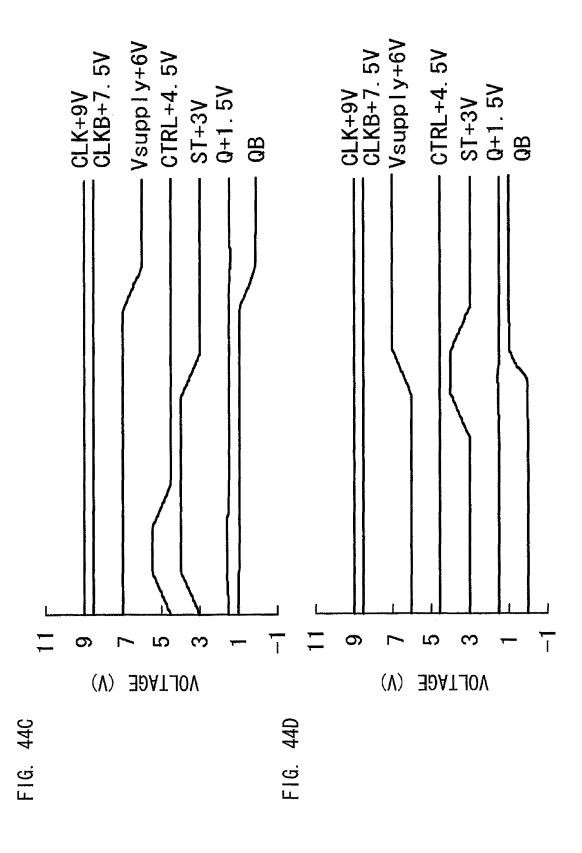

- FIG. 44A through FIG. 44D are diagrams illustrating simulation results of the thirteenth embodiment;

- FIG. 45 is a circuit diagram of a latch circuit in accordance 55 with a fourteenth embodiment;

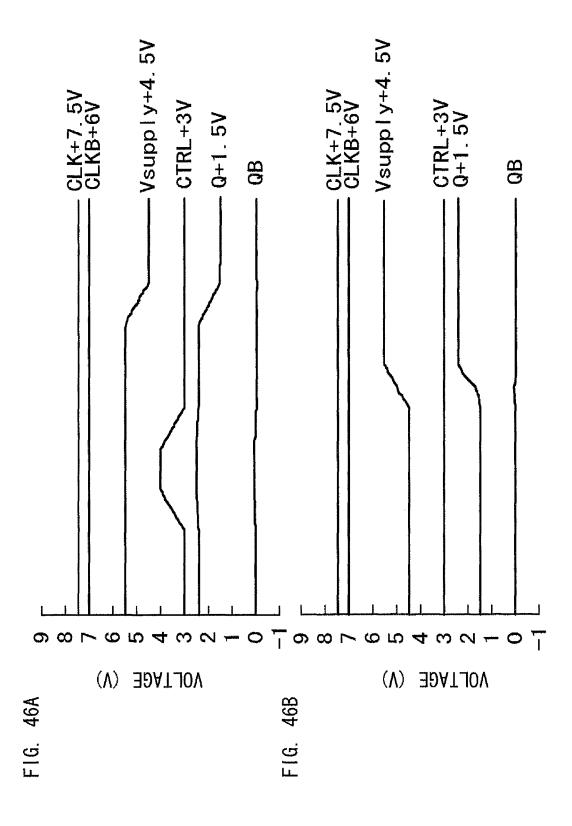

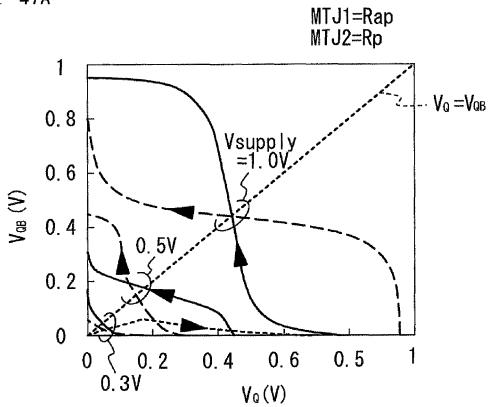

- FIG. 46A through FIG. 46D are diagrams (No. 1) illustrating simulation results of the fourteenth embodiment;

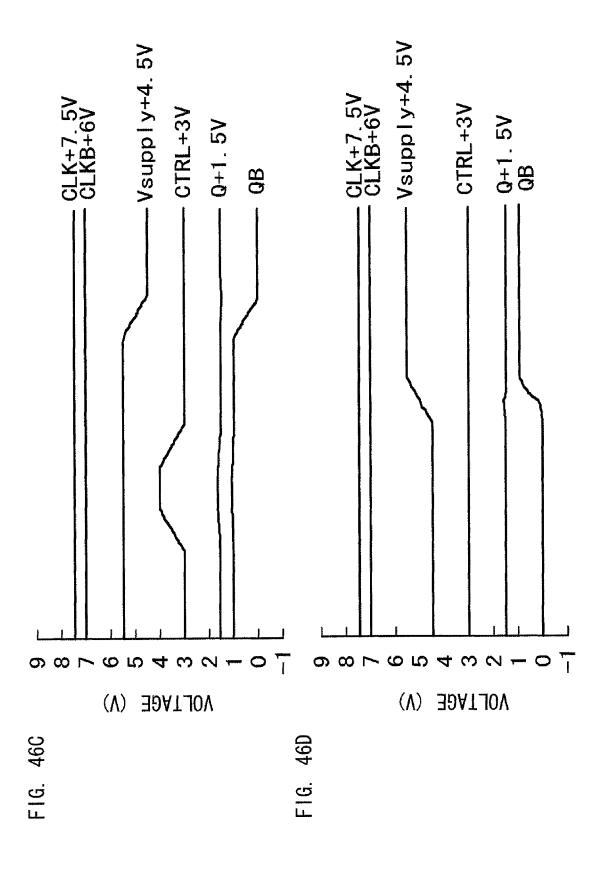

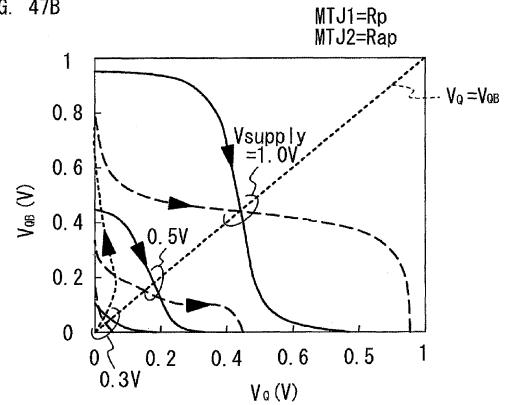

- FIG. 47A and FIG. 47B are diagrams (No. 2) illustrating simulation results of the fourteenth embodiment;

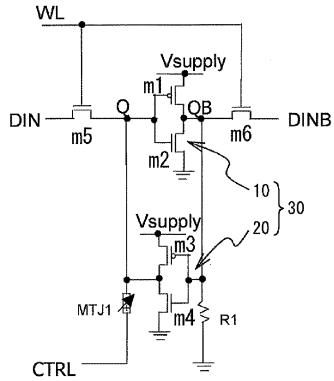

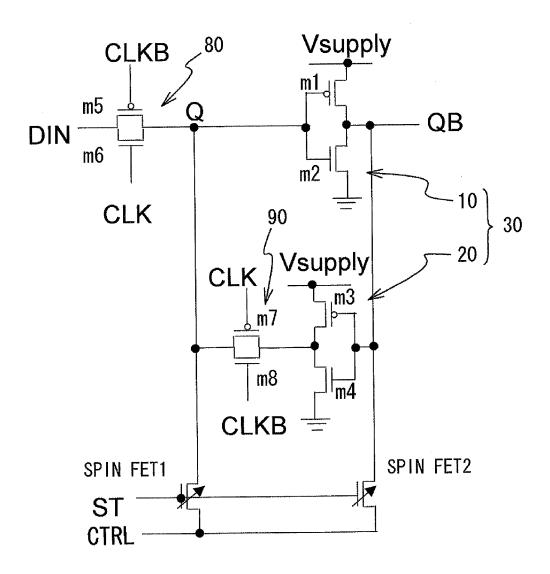

- FIG. 48A and FIG. 48B are circuit diagrams of a latch circuit in accordance with a fifteenth embodiment;

- FIG. 49A and FIG. 49B are circuit diagrams in accordance with a sixteenth embodiment;

- FIG. 50A and FIG. 50B are circuit diagrams of a latch circuit in accordance with a seventeenth embodiment;

- FIG. 51 is a circuit diagram of a latch circuit in accordance with an eighteenth embodiment;

FIG. **52** is a circuit diagram of a latch circuit in accordance with a nineteenth embodiment;

FIG. 53 is a timing diagram of the nineteenth embodiment;

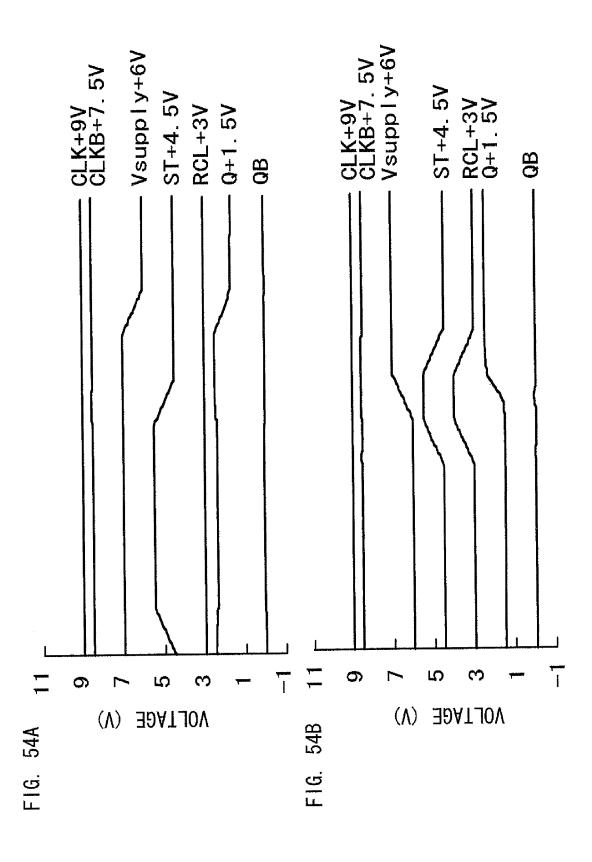

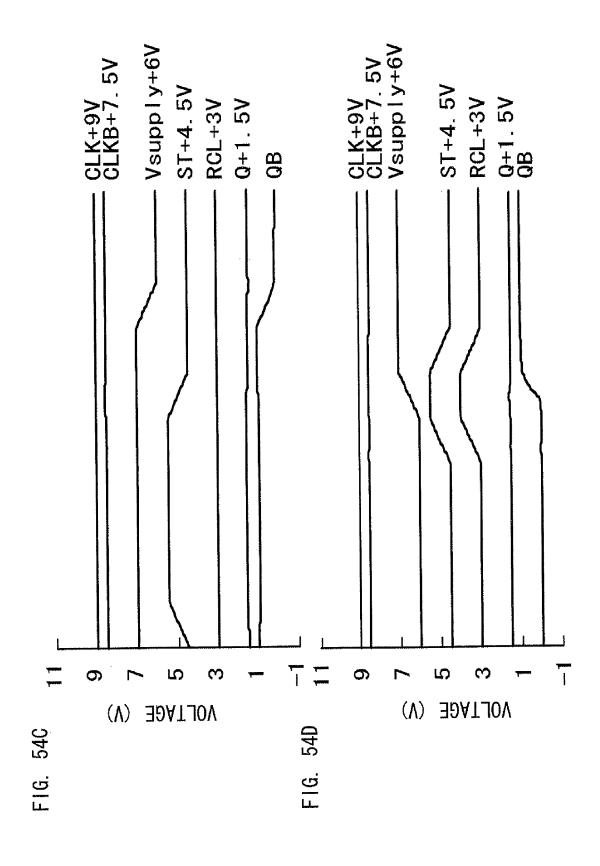

FIG. **54**A through FIG. **54**D are diagrams illustrating simulation results of the nineteenth embodiment:

FIG. **55** is a circuit diagram of a latch circuit in accordance with a twentieth embodiment;

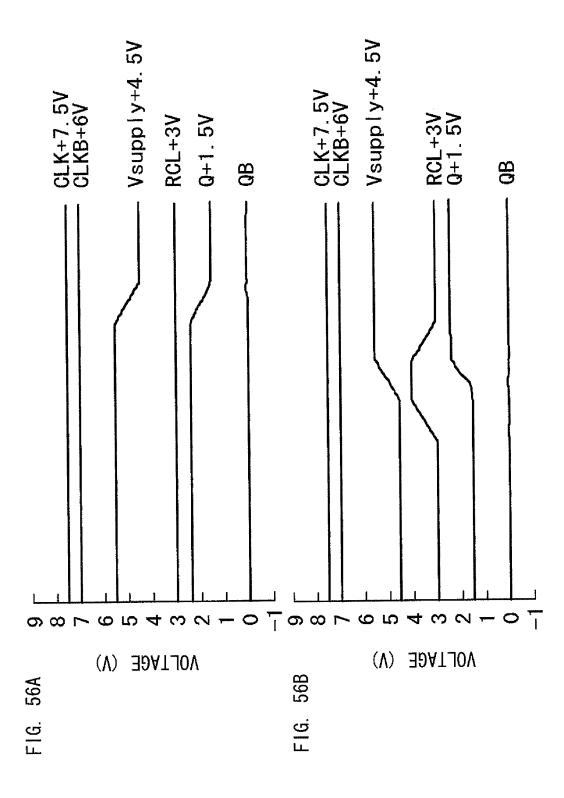

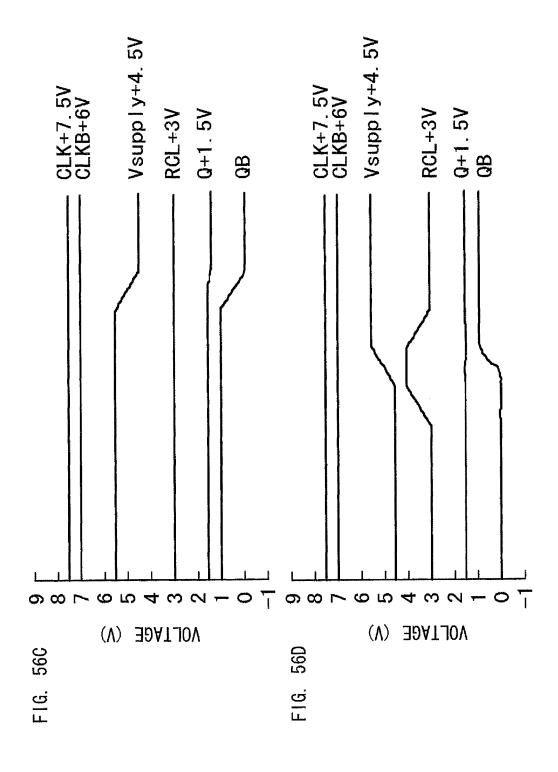

FIG. **56**A through FIG. **56**D are diagrams illustrating simulation results of the twentieth embodiment;

FIG. **57** is a circuit diagram of a latch circuit in accordance with a twenty-first embodiment;

FIG. **58** is a circuit diagram of a latch circuit in accordance with a twenty-second first embodiment;

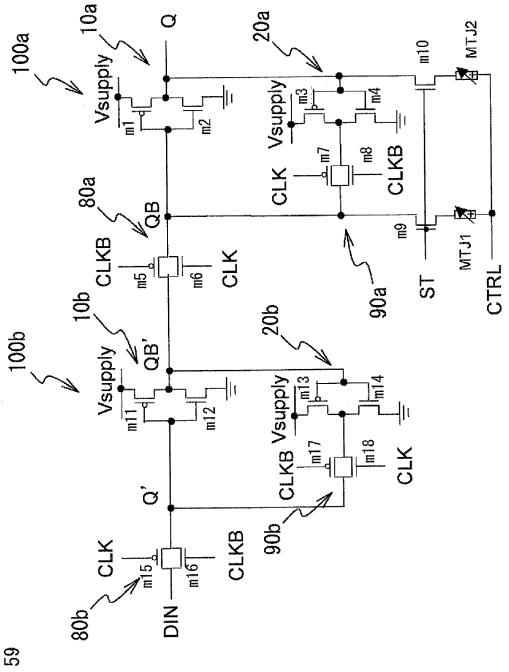

FIG. **59** is a circuit diagram of a flip-flop circuit in accordance with a twenty-third embodiment;

FIG. 60 is a circuit diagram of a latch circuit in accordance with a twenty-fourth embodiment;

FIG. **61**A and FIG. **61**B are circuit diagrams illustrating examples of a first logic circuit and a second logic circuit;

FIG. **62** is a circuit diagram of a latch circuit in accordance <sup>20</sup> with a twenty-fifth embodiment; and

FIG. 63 is a timing diagram of the twenty-fifth embodiment.

# BEST MODES FOR CARRYING OUT THE INVENTION

A description will now be given, with reference to drawings, of embodiments of the present invention.

# First Embodiment

FIG. 3 is a block diagram of a memory circuit in accordance with the first embodiment to explain a principle of the present invention. The memory circuit in accordance with the 35 first embodiment includes a first inverter circuit 15, a second inverter circuit 25, a ferromagnetic tunnel junction (MTJ) device 50, and an input/output switch 60. The first inverter circuit 15 and the second inverter circuit 25 are coupled in a ring shape, and compose a bistable circuit 30. The first 40 inverter circuit 15 and the second inverter circuit 25 are inverters 10 and 20 in FIG. 1 for example. Nodes to which the first inverter circuit 15 and the second inverter circuit 25 are coupled are nodes Q, and QB respectively. The node Q and the node QB are a complementary node to one another, and 45 the state of the bistable circuit 30 becomes stable when the node O and the node OB are at a high level and at a low level respectively, or when the node Q and the node QB are at a low level and at a high level respectively. When the state of the bistable circuit 30 becomes stable, the bistable circuit 30 can 50 store data. The ferromagnetic tunnel junction device 50 nonvolatilely stores data stored in the bistable circuit 30 according to a magnetization direction of a ferromagnetic electrode free layer. Data which is nonvolatilely stored in the ferromagnetic tunnel junction device 50 can be restored to the bistable 55 circuit 30. the input/output switch 60 connects or disconnects the input/output line and the node Q. Data of the input/output line can be stored in the bistable circuit 30 with the connection by the input/output switch 60. In addition, data of the bistable circuit 30 can be read out to the input/output line.

According to the first embodiment, data can be written in or read out from the bistable circuit 30 at about the same high speed as a circuit which does not include the ferromagnetic tunnel junction device 50. The ferromagnetic tunnel junction device 50 nonvolatilely stores data stored in the bistable circuit 30. This makes it possible to restore data which is nonvolatilely stored in the ferromagnetic tunnel junction device

10

**50** to the bistable circuit **30** even though a power source is shut down. Thus, when the power source is restored after the power source is shut down, the data stored before the power source is shut down can be read out.

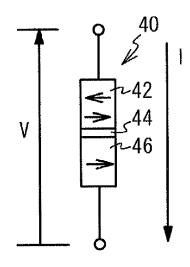

FIG. 4A is a diagram illustrating an example of a ferromagnetic tunnel junction device. A ferromagnetic tunnel junction device 40 includes a ferromagnetic electrode free layer 42, a ferromagnetic electrode pinned layer 46, and a tunnel insulation film 44 located between the ferromagnetic electrode free layer 42 and the ferromagnetic electrode pinned layer 46. The ferromagnetic electrode free layer 42 and the ferromagnetic electrode pinned layer 46 are composed of a ferromagnetic metal, a half-metallic ferromagnet, or a ferromagnetic semiconductor. A magnetization direction of the ferromagnetic electrode free layer 42 is changeable. On the other hand, the magnetization direction is pinned in the ferromagnetic electrode pinned layer 46. A state that magnetization directions of the ferromagnetic electrode free layer 42 and the ferromagnetic electrode pinned layer 46 are parallel is described as a parallel magnetization, and a state of anti-parallel is described as an anti-parallel magnetization.

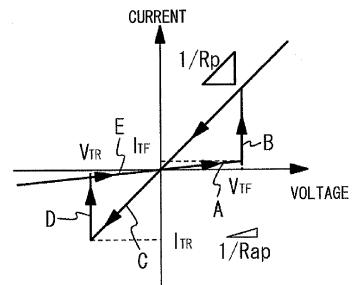

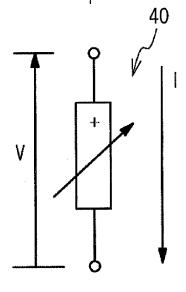

FIG. 4B is a diagram illustrating current-voltage characteristics of the ferromagnetic tunnel junction device 40. As illustrated in FIG. 4A, a voltage applied to the ferromagnetic electrode free layer 42 with reference to the ferromagnetic electrode pinned layer 46 is defined as V, and a current flowing from the ferromagnetic electrode free layer 42 to the ferromagnetic electrode pinned layer 46 is defined as I. Symbols of the ferromagnetic tunnel junction device 40 at this 30 time are defined as illustrated in FIG. 4C. Referring to FIG. 4B, a resistance Rp of the ferromagnetic tunnel junction device 40 in a parallel magnetization state becomes smaller than a resistance Rap of the ferromagnetic tunnel junction device 40 in an anti-parallel magnetization state. Generally, Rp and Rap are functions of a voltage applied to the ferromagnetic tunnel junction, but hereinafter are treated as a resistance value of which is approximately constant. Even when Rp and Rap are not constant resistances, discussions described later are applicable in the same manner. In an anti-parallel magnetization state, when the voltage V applied to the ferromagnetic tunnel junction device 40 becomes large, the current I becomes large with at a slope of a inverse of a resistance Rap (A in FIG. 4B). When the current I exceeds a threshold current  $I_{TE}$ , the magnetization of the ferromagnetic electrode free layer 42 is inverted by majority-spin electrons of the ferromagnetic electrode pinned layer 46 injected from the ferromagnetic electrode pinned layer 46 to the ferromagnetic electrode free layer 42, and a parallel magnetization state is achieved (B in FIG. 4B). This makes a resistance of the ferromagnetic tunnel junction device 40 Rp. On the other hand, when a negative current I flows in a parallel magnetization state (C in FIG. 4B) and exceeds a threshold current  $I_{TR}$ to a negative side, minority-spin electrons of the ferromagnetic electrode free layer 42 of electrons injected from the ferromagnetic electrode free layer 42 to the ferromagnetic electrode pinned layer 46 are reflected by the ferromagnetic electrode pinned layer 46. This makes the magnetization of the ferromagnetic electrode free layer 42 inverted, and an anti-parallel magnetization state is achieved (D in FIG. 4B). As described above, a method of inverting the magnetization direction of the ferromagnetic electrode free layer the magnetization direction of which is changed by the injection of spin-polarized electrons is called as a current-induced magnetization reversal method. The current-induced magnetization reversal method has possibility to reduce power consumption needed for changing a magnetization direction compared to a method to change a magnetization direction by

generating magnetic field. In addition, compared to the method to change the magnetization direction by generating magnetic field, the current-induced magnetization reversal method is insusceptible to a disturb which causes accidental writing and accidental erasure to a cell other than selected cell, and is suitable for high density integration because a problem of stray magnetic field does not exist.

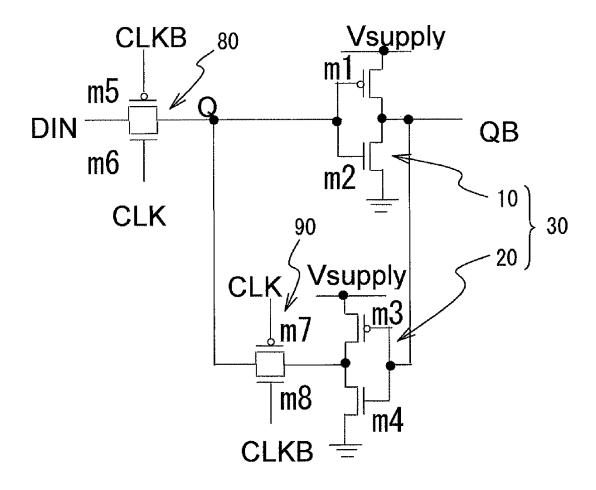

#### Second Embodiment

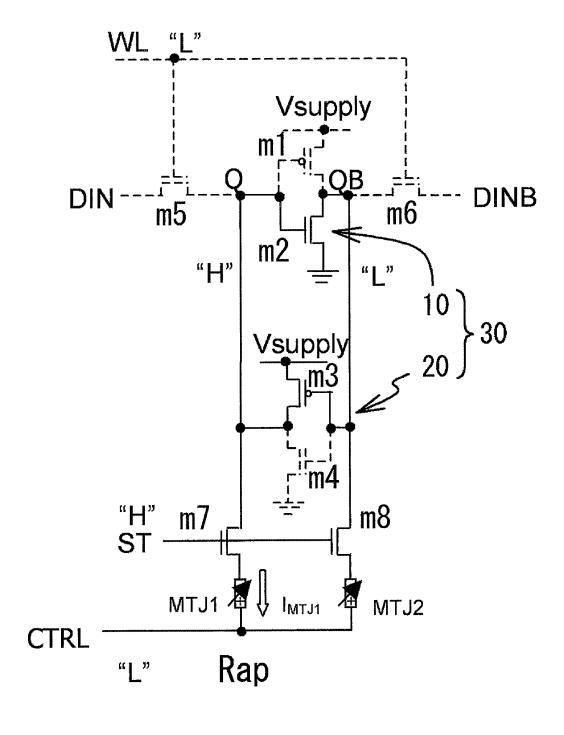

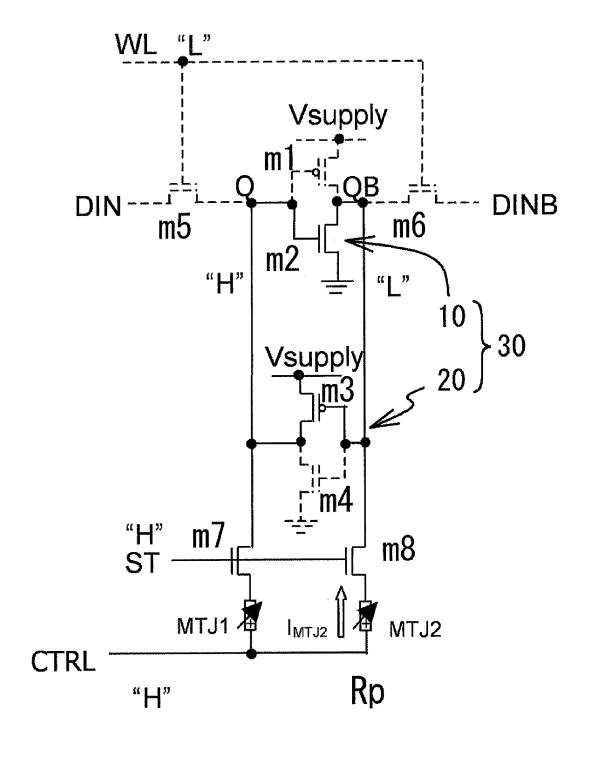

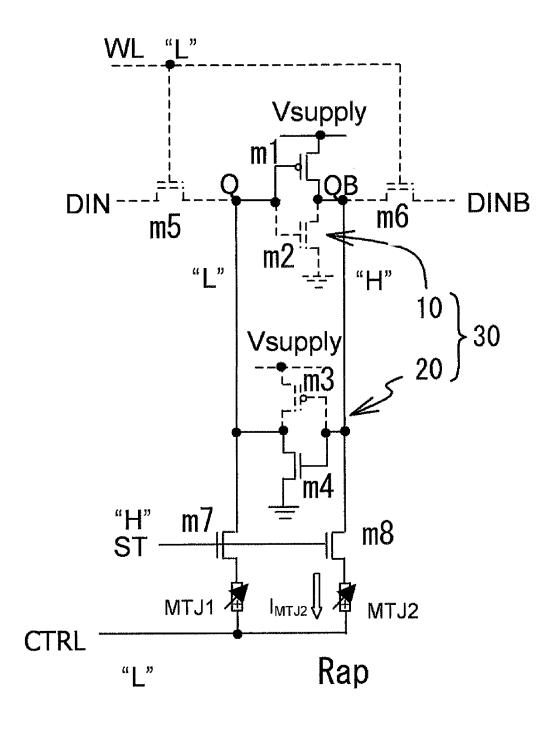

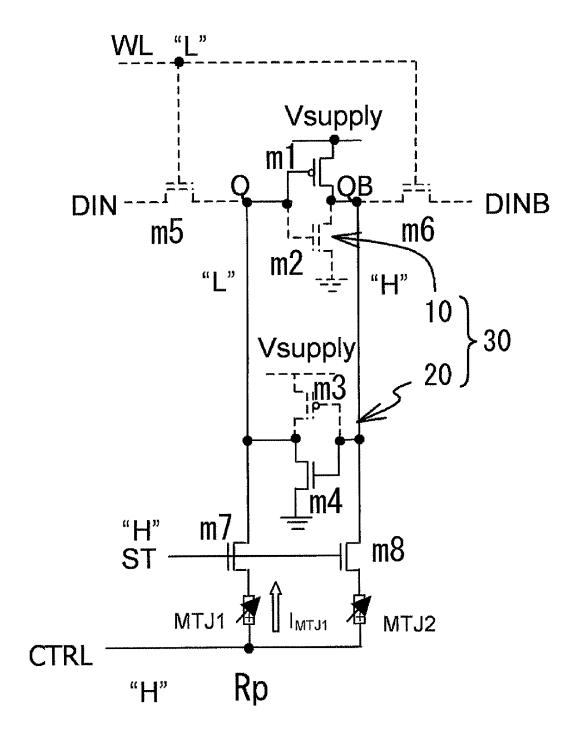

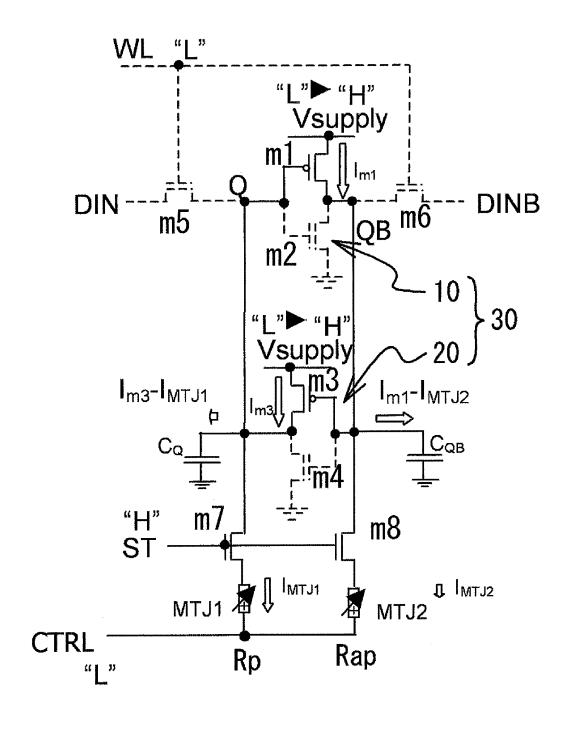

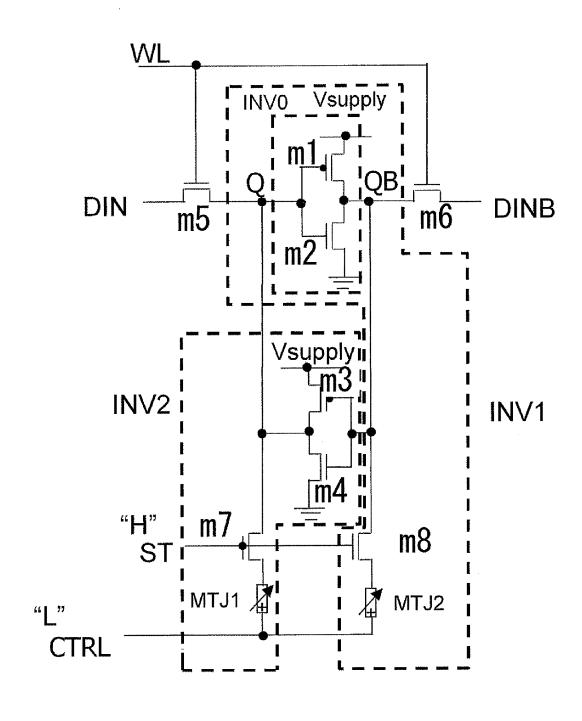

FIG. **5** is a circuit diagram of a memory circuit in accordance with the second embodiment. Referring to FIG. **5**, the memory circuit in accordance with the second embodiment includes n-type FETs m**7** and m**8**, and ferromagnetic tunnel junction devices MTJ**1** and MTJ**2** in addition to the SRAM 15 cell in FIG. **1**. The FET m**7** and the ferromagnetic tunnel junction device MTJ**1** are coupled between the node Q and the control line CTRL, and the FET m**8** and the ferromagnetic tunnel junction device MTJ**2** is coupled between the node QB and the control line CTRL. Gates of FETs m**7** and m**8** are 20 coupled to the switch line ST.

A description will now be given of a behavior of the memory circuit in accordance with the second embodiment. Writing data to and reading data from the bistable circuit 30 are performed in the same way as a conventional SRAM. That 25 is to say that by setting the word line WL to a high level, and making FETs m5 and m6 conductive, data of the input/output lines DIN and DINB are written in the bistable circuit 30. In addition, by making input/output lines DIN and DINB an equipotential floating condition, setting the word line WL to 30 a high level, and making FETs m5 and m6 conductive, data in the bistable circuit 30 can be read out to input/output lines DIN and DINB. By making FETs m5 and m6 non-conductive, data in the bistable circuit 30 is held. When writing, reading, and holding data to/from/in the bistable circuit 30, it 35 is preferable that the switch line ST is at a low level, and FETs m7 and m8 are non-conductive. This can suppress the current between nodes Q and QB and the control line CTRL, and reduce power consumption.

A description will now be given of a method to nonvola- 40 tilely store the data stored in the bistable circuit to ferromagnetic tunnel junction devices MTJ1 and MTJ2. A description will be given of the case that data where the node Q is at a high level "H" and the node QB is at a low level "L" is held first. Hereinafter, in circuit diagrams of FIGS. 6A and 6B, FIGS. 45 7A and 7B, FIGS. 9A through 9C, and FIGS. 11A through 11C, conductive FETs and the like are illustrated with a solid line, and non-conductive FETs and the like are illustrated with a dashed line. Referring to FIG. 6A and FIG. 6B, the word line WL is at a low level. This makes FETs m5 and m6 50 non-conductive, and data is held in the bistable circuit 30. Referring to FIG. 6A, the switch line ST is at a high level and the control line CTRL is at a low level. The current  $I_{MTJ1}$  flows from the node Q to the control line CTRL via the FET m7. If the current  $I_{MTJ1}$  is set to exceed the threshold current  $I_{TR}$ , a 55 resistance of the ferromagnetic tunnel junction device MTJ1 results in a high resistance Rap. Since the node QB is at a low level, a current doesn't flow in the ferromagnetic tunnel junction device MTJ2. Referring to FIG. 6B, the switch line ST is at a high level and the control line CTRL is at a high level. A 60 current  $I_{MTJ2}$  flows from the control line CTRL to the node QB. If the current  $I_{MTJ2}$  is set to exceed the threshold current  $I_{TF}$ , a resistance of the ferromagnetic tunnel junction device MTJ2 results in a low resistance Rp. Since the node Q is at a high level, a current doesn't flow in the ferromagnetic tunnel 65 junction device MTJ1. When a sequence of operations described above is completed, a resistance of the ferromag12

netic tunnel junction device MTJ1 results in a high resistance Rap, and a resistance of the ferromagnetic tunnel junction device MTJ2 results in a low resistance Rp. Any steps in FIG. 6A and FIG. 6B can be performed first.

Referring to FIG. 7A and FIG. 7B, a description will be given of the case that data where the node O is at a low level and the node OB is at a high level is held. Referring to FIG. 7A, when the switch line ST is at a high level and the control line CTRL is at a low level, the ferromagnetic tunnel junction device MTJ2 results in a high resistance Rap because a current  $\mathbf{I}_{MTJ2}$  flows from the node QB to the control line CTRL. Since the node Q is at a low level, a current does not flow in the ferromagnetic tunnel junction device MTJ1. Referring to FIG. 7B, when the switch line ST is at a high level and the control line CTRL is at a high level, the ferromagnetic tunnel junction device MTJ1 results in a low resistance Rp because a current  $I_{MTD}$  flows from the control line CTRL to the node Q. Since the node QB is at a high level, a current does not flow in the ferromagnetic tunnel junction device MTJ2. When a sequence of operations is completed, the resistance of the ferromagnetic tunnel junction device MTJ1 results in a low resistance Rp, and the resistance of the ferromagnetic tunnel junction device MTJ2 results in a high resistance Rap. As described above, data in the bistable circuit 30 can be nonvolatilely stored in ferromagnetic tunnel junction devices MTJ1 and MTJ2.

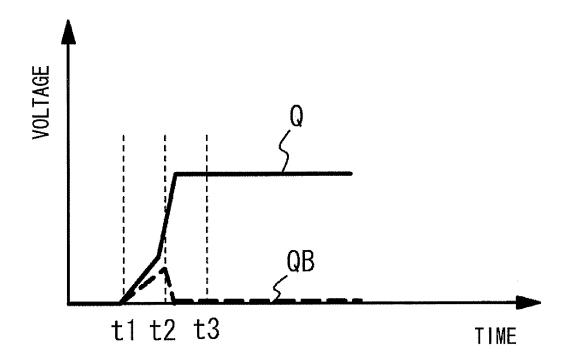

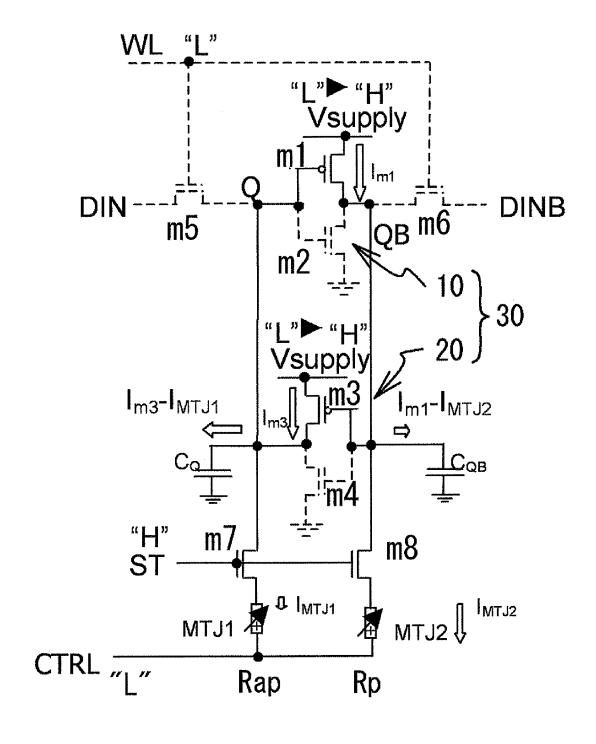

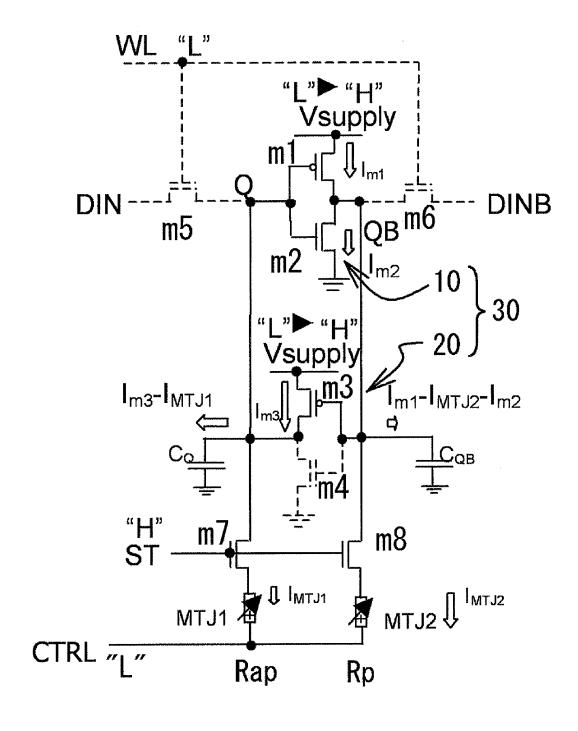

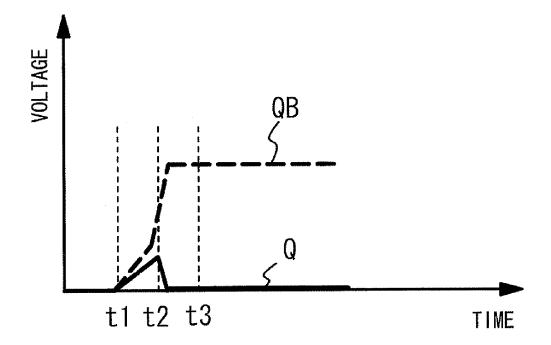

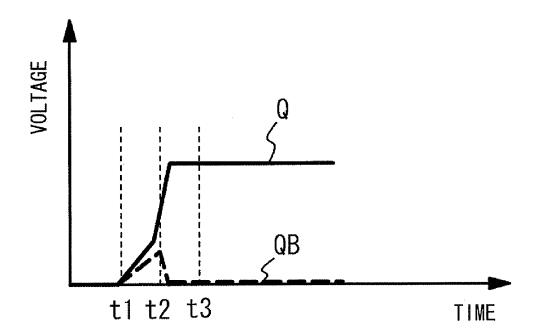

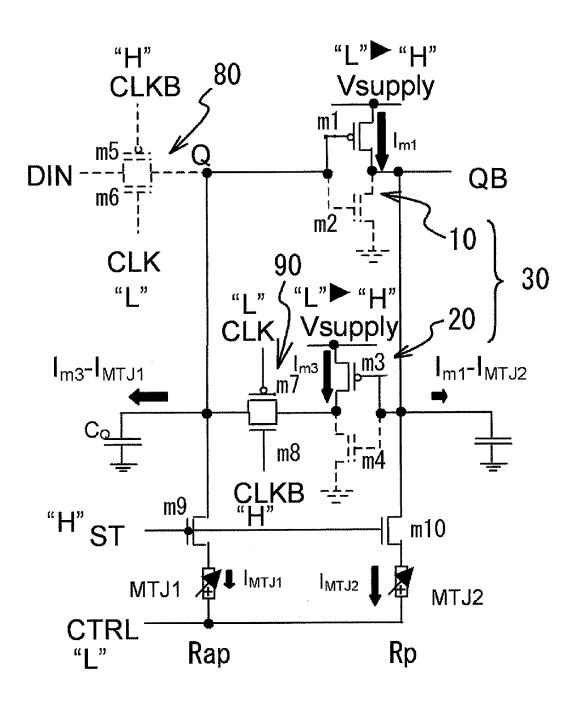

Even when a power source Vsupply is shut down and data in the bistable circuit **30** is lost, resistances of ferromagnetic tunnel junction devices MTJ1 and MTJ2 are held nonvolatilely. A description will now be given of a method of restoring data from ferromagnetic tunnel junction devices MTJ1 and MTJ2 to the bistable circuit **30** after that. FIG. **8** is a diagram illustrating voltages of nodes Q and QB in time for a data restoration to the bistable circuit **30**. FIG. **9**A through **9**C are diagrams to explain conditions of the memory circuit at times t1 through t3 in FIG. **8** respectively. In FIG. **9**A through FIG. **9**C, capacitors  $C_Q$  and  $C_{QB}$  are coupled to nodes Q and QB respectively. Capacitors  $C_Q$  and  $C_{QB}$  are a wiring capacitor or a parasitic capacitor for example.

Referring to FIG. 9A, ferromagnetic tunnel junction devices MTJ1 and MTJ2 are a high resistance Rap and a low resistance Rp respectively. The switch line ST is at a high level at the time t1. A power source voltage is raised to a high level from a low level. Since nodes Q and QB are at a low level, currents  $I_{m1}$  and  $I_{m3}$  flow from a power source Vsupply to nodes Q and QB via FETs m1 and m3 in inverters 10, and 20 respectively. Since the ferromagnetic tunnel junction device MTJ1 is a high resistance Rap, a current  $I_{MTJ1}$  flowing from the node Q to the control line CTRL which is at a low level is small. Since the ferromagnetic tunnel junction device MTJ2 is a low resistance Rp, a current  $I_{MTJ2}$  flowing from the node QB to the control line CTRL which is at a low level is large

Voltages  $\mathbf{V}_Q$  and  $\mathbf{V}_{QB}$  of nodes Q and QB are expressed by following formulas.

$$V_Q\!\!=\!\!\!\int\!\!(I_{m3}\!\!-\!\!I_{m4}\!\!-\!\!I_{MTJ1})/dt/\!C_Q \qquad \qquad \text{formula 1}$$

$$V_{QB} = \int (I_{m1} - I_{m2} - I_{MTJ2})/dt/C_{QB}$$

formula 2

In addition, a relation of magnitude of each current is expressed as follows.

$$\mathbf{I}_{m1}\mathbf{-I}_{m3}\mathbf{>>}\mathbf{I}_{m2}\mathbf{=}\mathbf{I}_{m4}$$

formula 3

$$I_{MTJ1} < I_{MTJ2}$$

formula 4

In addition, capacitances  $C_Q$  and  $C_{QB}$  of capacitors  $C_Q$  and  $C_{QB}$  are expressed as follows.

$$C_Q=C_{QB}$$

formula

Accordingly, a current charging a capacitor  $C_Q$  from the 5 node Q is  $I_{m3}$ – $I_{MTJ1}$ , and a current charging a capacitor  $C_{QB}$  from the node QB is  $I_{m1}$ – $I_{MTJ2}$ . Therefore,

$$V_Q > V_{QB}$$

is obtained.

Accordingly, both voltages  $V_Q$  and  $V_{QB}$  increase between the time t1 and the time t2 in FIG. 8, but  $V_Q$  is larger than  $V_{QB}$ .

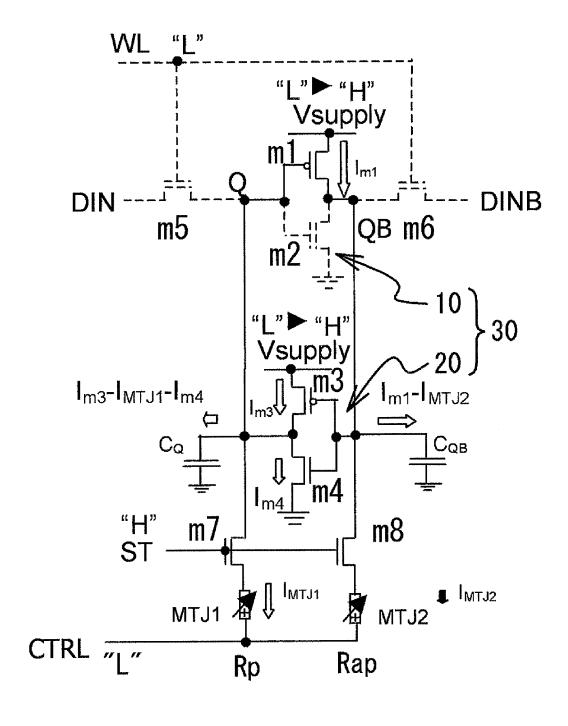

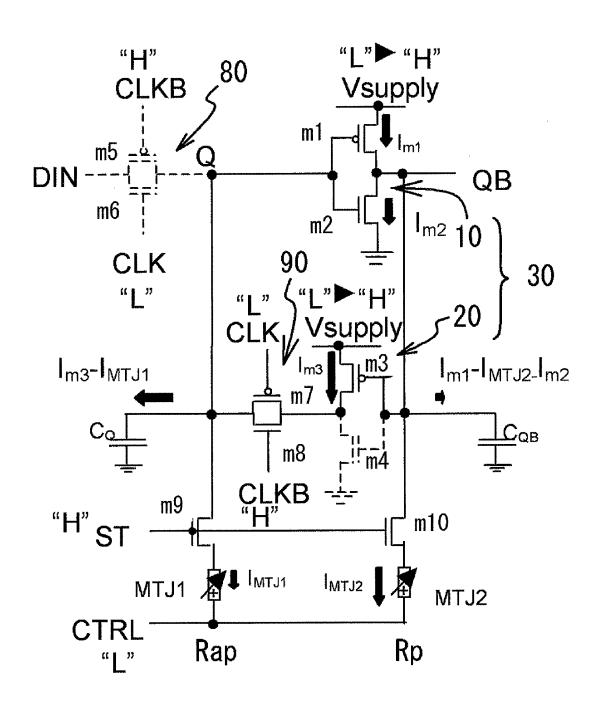

Referring to FIG. 9B, when  $V_Q$  becomes higher than a threshold voltage of the FET m2 composing the inverter 10 at 15 the time t2 in FIG. 8, the FET m2 becomes conductive, and a current  $I_{m2}$  flows in the FET m2. A current charging the capacitor  $C_{QB}$  becomes  $I_{m1}$ – $M_{MT,T2}$ – $I_{m2}$ . If a current  $I_{m2}$  becomes large, the capacitor  $C_{QB}$  discharges, and a voltage of the node OB becomes zero.

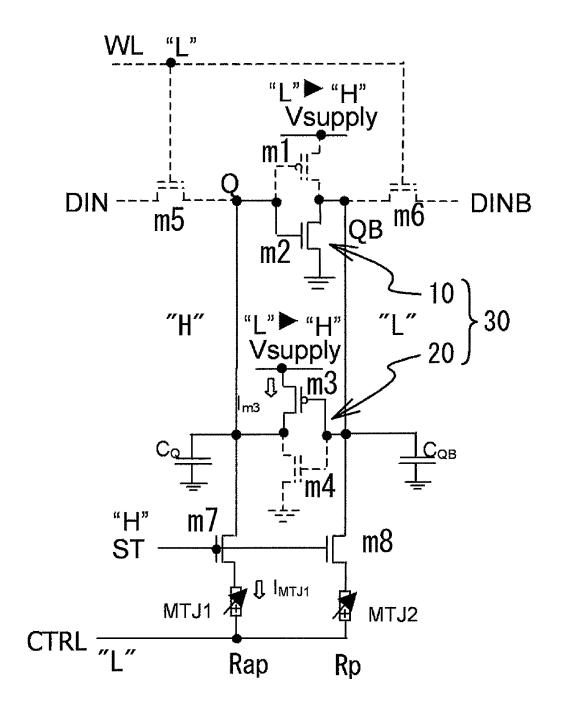

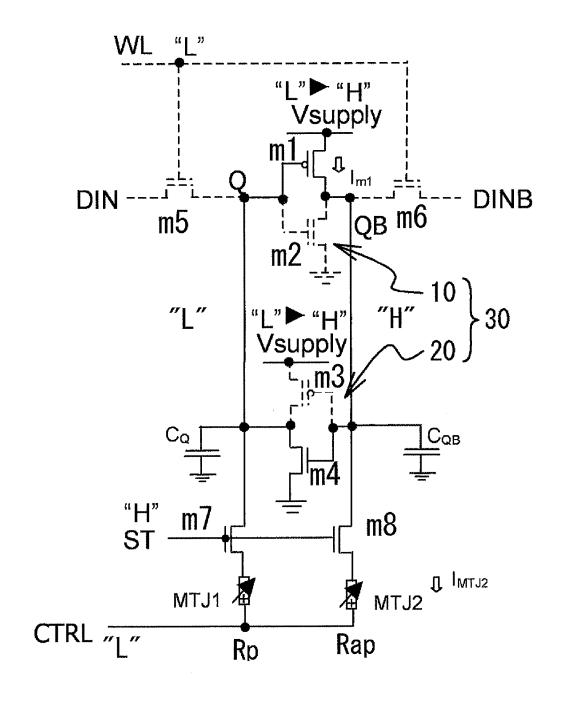

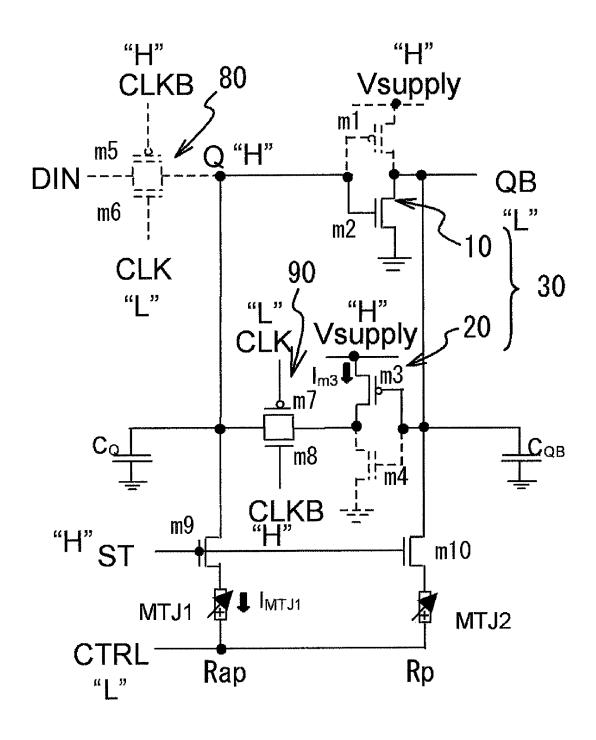

Referring to FIG. 9C, when a steady state is achieved at the time t3 in FIG. 8,  $I_{m3}$  becomes equal to  $I_{MTJ1}$ , the capacitor  $C_Q$  comes to a charged condition, and the capacitor  $C_{QB}$  comes to a discharged condition. This makes the node Q at a high level, and the node QB at a low level, and a data restoration to the 25 bistable circuit 30 from ferromagnetic tunnel junction devices MTJ1 and MTJ2 is completed.

FIG. 10 is a diagram illustrating a data restoration to the bistable circuit 30 in the case that ferromagnetic tunnel junction devices MTJ1 and MTJ2 are a low resistance Rp and a 30 high resistance Rap respectively, contrary to FIG. 8. FIG. 11A through FIG. 11C are diagrams to explain conditions of the memory circuit at times t1 through t3 in FIG. 10 respectively.

Referring to FIG. 11A, when raising a power source voltage to a high level from a low level, both voltages  $V_{\mathcal{Q}}$  and  $V_{\mathcal{QB}}$  is larger than  $V_{\mathcal{Q}}$ . Referring to FIG. 11B, when  $V_{\mathcal{QB}}$  becomes higher than a threshold voltage of the FET m4 composing the inverter 20, the FET m4 becomes conductive and a current Im4 flows. The voltage  $V_{\mathcal{Q}}$  of the node Q descends. Referring to FIG. 11C, when a steady state 40 is achieved, the node Q becomes at a low level, and the node QB becomes at a high level. According to above operations, a data restoration to the bistable circuit 30 from ferromagnetic tunnel junction devices MTJ1 and MTJ2 is completed.

A description will now be given of a data restoration to the 45 bistable circuit 30 from ferromagnetic tunnel junction devices MTJ1 and MTJ2 by focusing on the inverter. As illustrated in FIG. 12, a circuit provided with the inverter 10 and the ferromagnetic tunnel junction device MTJ2 will be described as an inverter INV1, a circuit provided with the 50 inverter 20 and the ferromagnetic tunnel junction device MTJ1 will be described as an inverter INV2, and the inverter 10 or 20 without a ferromagnetic tunnel junction device will be described as an inverter INV0.

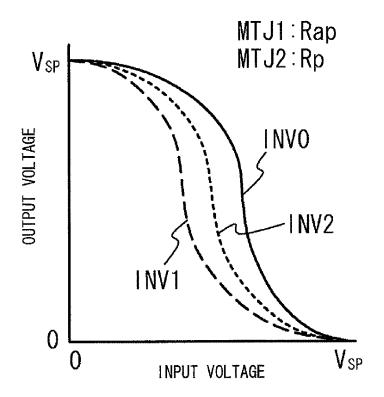

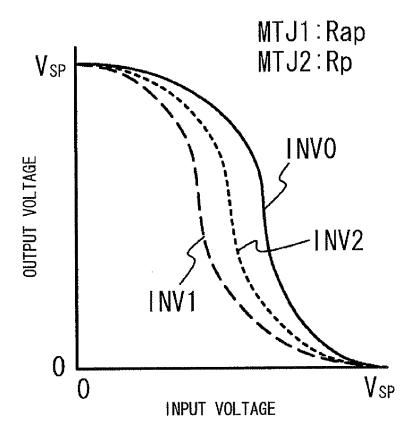

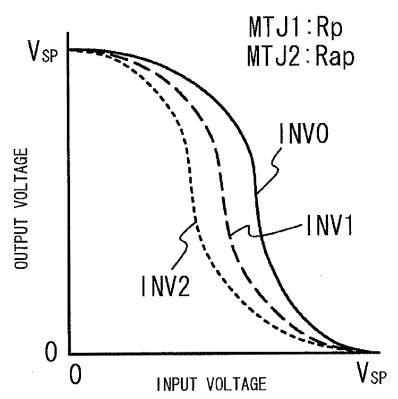

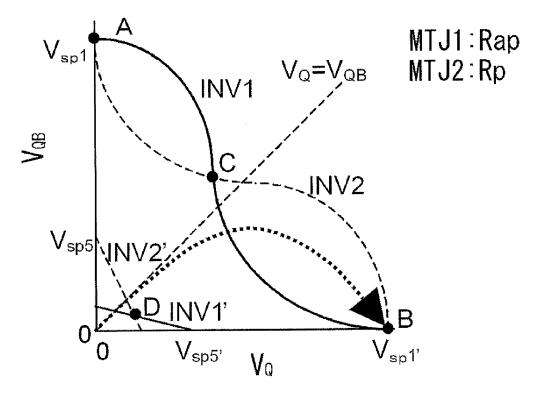

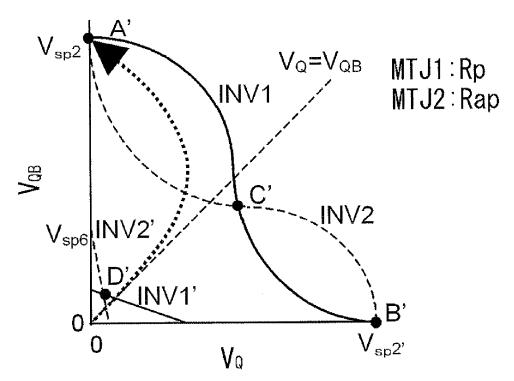

FIG. 13A is a conceptual diagram illustrating input/output 55 characteristics of the inverter in the case that the ferromagnetic tunnel junction device MTJ1 is a high resistance Rap and the ferromagnetic tunnel junction device MTJ2 is a low resistance Rp. Compared to the inverter INV0 without the ferromagnetic tunnel junction device, logic thresholds of 60 inverters INV1 and INV2 to which a ferromagnetic tunnel junction device is added become low. Compared to the inverter INV2 with the ferromagnetic tunnel junction device MTJ1 which is a high resistance Rap, the logic threshold of the inverter INV1 with the ferromagnetic tunnel junction 65 device MTJ2 which is a low resistance Rp becomes further low. Referring to FIG. 13B, when the ferromagnetic tunnel

14

junction device MTJ1 is a low resistance Rp and the ferromagnetic tunnel junction device MTJ2 is a high resistance Rap, the logic threshold of the inverter INV2 becomes low compared to the inverter INV1.

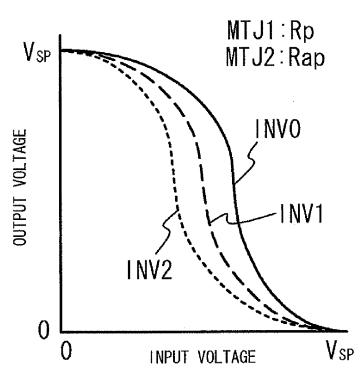

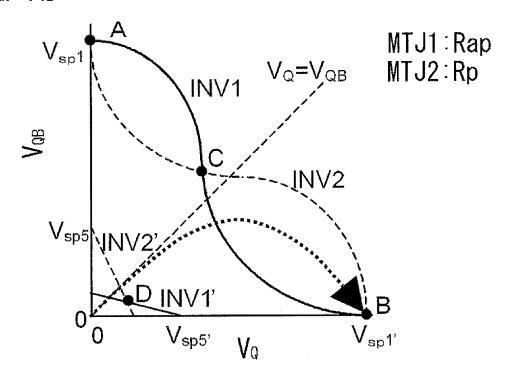

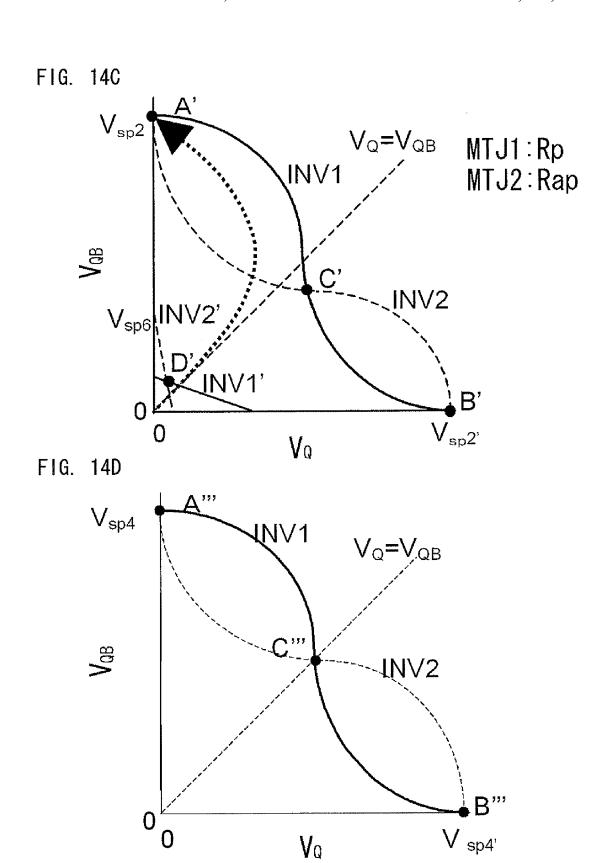

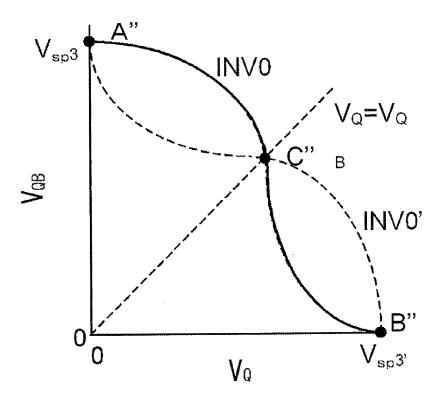

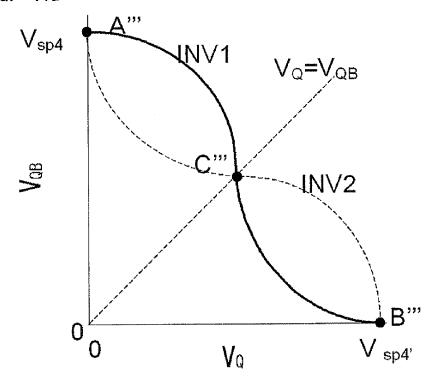

FIG. 14A is a conceptual diagram of a characteristic curve of the bistable circuit composed of the inverter INV0 or INV0' to which a ferromagnetic tunnel junction device is not coupled. Since characteristics of inverters INV0, and INV0' are equal, a switch point C" of the bistable circuit 30 is on the line  $V_{\mathcal{Q}} = V_{\mathcal{QB}}$ . A loop of a characteristic curve between the point A" when  $V_{\mathcal{QB}}$  is equal to a power source voltage Vsp3 and the switch point C" and a loop of a characteristic curve between a point B" when  $V_{\mathcal{Q}}$  is equal to a power source voltage Vsp3' and the point C" are symmetric.

FIG. 14B is a conceptual diagram of a characteristic curve of the bistable circuit 30 in a case that the ferromagnetic tunnel junction device MTJ1 is a high resistance Rap, and the ferromagnetic tunnel junction device MTJ2 is a low resistance Rp. Since input/output characteristics of inverters INV1 20 and INV2 are asymmetric, the switch point C of the bistable circuit 30 lies above the line  $V_Q = V_{QB}$ . A loop of a characteristic curve between the point A when  $V_{OB}$  is equal to a power source voltage  $V_{sp1}$  and the switch point C becomes smaller than a loop of a characteristic curve between the point B when  $V_Q$  is equal to a power source voltage  $V_{sp1}$ , and the point C. A process to raise a power source voltage Vsupply from a ground voltage  $0\,\mathrm{V}$  to a voltage  $\mathrm{V}_{sp1}$  or  $\mathrm{V}_{sp1}$  is considered. At this time, a current  $\mathrm{I}_{MTJ2}$  flowing in the ferromagnetic tunnel junction device MTJ2 is set not to exceed a threshold current  $I_{TR}$ . When a power source voltage Vsupply is equal to a voltage  $V_{sp5}$  or  $V_{sp5}$  which slightly exceeds an absolute value of a threshold voltage of a p-type MOSFET used in the inverter, characteristic curves of the inverter INV1 and the inverter INV2 become INV1' and INV2'. The threshold voltage of the inverter INV2 is lower than that of the inverter INV1. This means that when input voltages to inverters INV1, and INV2 (the voltage of the node Q in the case of the inverter INV2, and the voltage of the node Q in the case of the inverter INV2) are same, in the inverter INV2 more current flows from an output node (the node QB in the case of the inverter INV1, the node QB in the case of the inverter INV1) to a ground. Therefore, the output voltage of the inverter INV2 when the input voltage is 0 V is also lower than that of the inverter INV1. Thus, although a dynamic operating point of the bistable circuit depends on a speed of raising a power source voltage Vsupply and the like, it follows a locus illustrated with a dashed arrow and converges on the point B because the static steady point always lies below the line  $V_O = V_{OB}$ .

FIG. 14C is a conceptual diagram of a characteristic curve of the bistable circuit 30 in the case that the ferromagnetic tunnel junction device MTJ1 is a low resistance Rp and the ferromagnetic tunnel junction device MTJ2 is a high resistance Rap. The switch point C' of the bistable circuit 30 lies below the line  $V_Q = V_{QB}$ . A loop of a characteristic curve between the point A' when  $V_{QB}$  is equal to a power source voltage  $V_{sp2}$  and the switch point C' becomes bigger than a loop of a characteristic curve between the point B' when  $V_Q$  is equal to a power source voltage  $V_{sp2}$ , and the point C'. At this time, a power source voltage  $V_{sp2}$ , and the point C'. At this time, a power source voltage  $V_{sp2}$ , and the point C'. At this time, a power source voltage  $V_{sp2}$  flowing in the ferromagnetic tunnel junction device MTJ1 does not exceed the threshold current  $I_{TR}$ . The dynamic operating point of the bistable circuit 30 follows a locus illustrated with a dashed arrow and converges on the point A' because the static steady point always lies above the line  $V_Q = V_{QB}$ .

In FIGS. 14B and 14C, even though the dynamic operating point becomes  $V_O = V_{OB}$  when raising a power source voltage,

the direction on which the operating point converges does not change and the operating point converges on the point B or point A' because it lies within the characteristic loop which lies above or below the line  $\mathbf{V}_O\!\!=\!\!\mathbf{V}_{OB}$  until just before that.

In FIG. 14B or 14C, once the current IMJ1 or  $I_{MTJ2}$  of the 5 ferromagnetic tunnel junction device MTJ1 or MTJ2 exceeds the threshold current  $I_{TR}$ , ferromagnetic tunnel junction devices MTJ1 and MTJ2 become a high resistance Rap. Therefore, as illustrated in FIG. 14D, logic thresholds of inverters INV1 and INV2 become same, and the switch point 10 C''' becomes on the line  $V_Q = V_{QB}$ . Accordingly, when raising a power source voltage  $V_{SUP}$  to a voltage  $V_{SP4}$  or  $V_{SP4}$  from 0 V, it cannot be determined whether the static steady point converges on the point A''' or on the point B'''. As described above, when restoring data, it is preferable to set currents 15  $I_{MTJ1}$  and  $I_{MTJ2}$  so as not to exceed the threshold current  $J_{TR}$ .

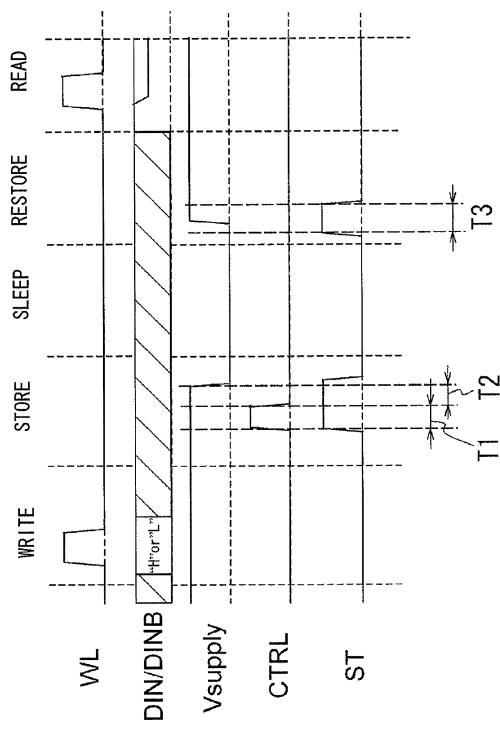

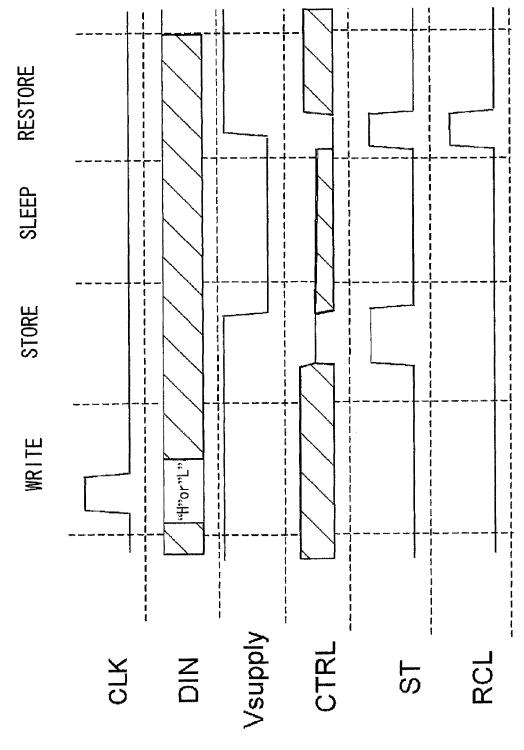

FIG. 15 is a timing diagram illustrating a control of the memory circuit in accordance with the second embodiment. A hatched area indicates that it is not exactly known whether it is at a high level or at a low level. Referring to FIG. 15, a 20 power source voltage V supply is supplied, and the control line CTRL and the switch line ST are at a low level. Writing data to the bistable circuit 30 is performed by setting the word line WL to a high level and setting input/output lines DIN and DINB to a high level or to a low level. Storing data from the 25 bistable circuit 30 to ferromagnetic tunnel junction devices MTJ1, and MTJ2 is performed by setting the switch line ST and the control line CTRL to a high level during the period T1 (corresponding to FIG. 6B and FIG. 7B), and setting the switch line ST to a high level and setting the control line CTRL to a low level during the period T2 (corresponding to FIG. 6A and FIG. 7A).

After that, by setting a power source voltage Vsupply to 0 V, the memory circuit becomes sleep condition. Since a current does not flow in the memory circuit at this time, power 35 consumption can be reduced. Restoring data from ferromagnetic tunnel junction devices MTJ1 and MTJ2 to the bistable circuit 30 is performed by raising a power source voltage Vsupply from 0 V under the condition that the control line CTRL is at a low level and the switch line ST is at a high level 40 during the period T3 (corresponding to FIG. 8 through FIG. 11C). Reading out data from the bistable circuit 30 is performed by setting the word line WL to a high level.

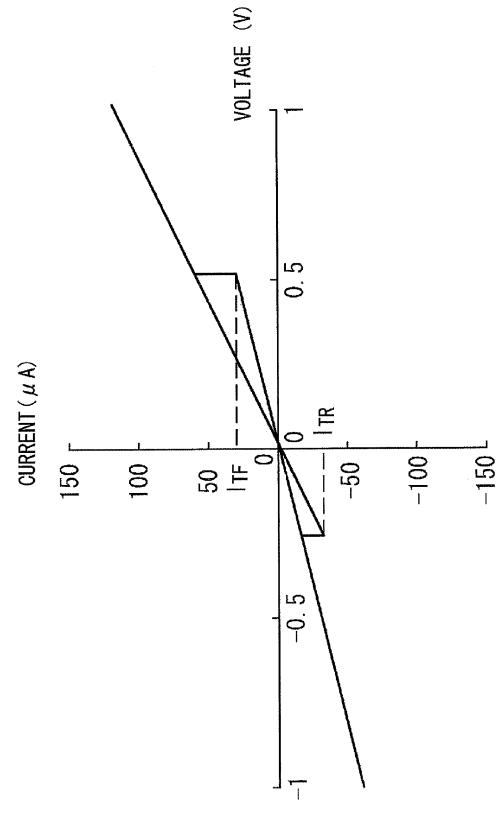

A simulation of the memory circuit in accordance with the second embodiment is performed. FIG. **16** is a diagram of 45 current-voltage characteristics of a ferromagnetic tunnel junction device used for the simulation. Threshold currents  $I_{\mathit{TF}}$  and  $I_{\mathit{TR}}$  are 30  $\mu A$  and  $-30\,\mu A$  respectively, and resistances Rap and Rp are 16.7 k $\Omega$  and 8.33 k $\Omega$  respectively. A channel length L of each FET is 0.07  $\mu m$ , a channel width Wn of an 50 n-type FET is 1.0  $\mu m$ , and a channel width Wp of a p-type FET is 1.5  $\mu m$ .

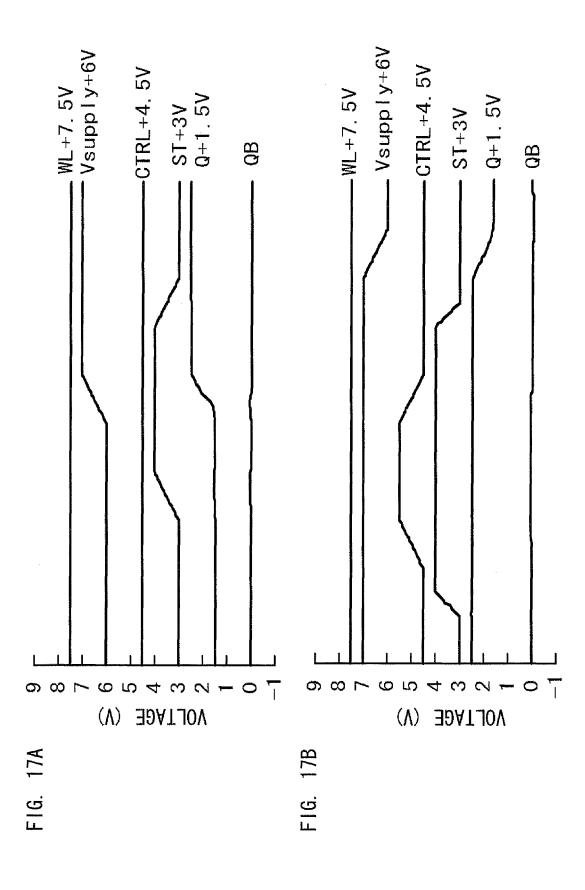

FIG. 17A through FIG. 17D are timing diagrams illustrating simulation results. FIG. 17A is a timing diagram of a storing operation when the node Q is at a high level, and FIG. 55 17B is a timing diagram of a restoring operation after FIG. 17A. FIG. 17C is a timing diagram of a storing operation when the node Q is at a low level, and FIG. 17D is a timing diagram of a restoring operation after FIG. 17C. Each diagram is illustrated by adding 1.5 V to the level of the node Q, 60 3 V to the level of the switch line ST, 4.5 V to the level of the control line CTRL, 6 V to a power source voltage Vsupply, and 7.5 V to the level of the word line WL. A method for storing and a method for restoring are same as described before

In FIG. 17A, the condition that the node Q is at a high level and the node QB is at a low level is stored in the ferromagnetic

16

tunnel junction device. In FIG. 17B, a high level is restored to the node Q, and a low level is restored to the node QB. In the same manner, in FIG. 17C, the condition that the node Q is at a low level and the node QB is at a high level is stored in the ferromagnetic tunnel junction device. In FIG. 17D, a low level is restored to the node Q, and a high level is restored to the node QB. As described above, in the memory circuit in accordance with the second embodiment, it can be confirmed that data stored in ferromagnetic tunnel junction devices MTJ1 and MTJ2 can be restored to the bistable circuit 30 after a power source is restored.

## Third Embodiment

FIG. 18 is a circuit diagram of a memory circuit in accordance with the third embodiment. Compared to diagrams of the second embodiment, the FET m7 and the FET m8 are not provided in the third embodiment. As described, it is not necessary to provide the FET m7 (a first switch) and the FET m8 (a second switch). However, to suppress the current flowing from the bistable circuit 30 to the control line CTRL, it is preferable to provide the FET m7 and the FET m8.

FIG. 19A through FIG. 19D are diagrams illustrating results of simulations, which are performed in the same manner as FIG. 17A through FIG. 17D of the second embodiment, to the memory circuit in accordance with the third embodiment. Each diagram is illustrated by adding 1.5 V to the level of the node Q, 3 V to the level of the control line CTRL, 4.5 V to a power source voltage V supply, and 6 V to the level of the word line WL.

In FIG. 19A, the condition that the node Q is at a high level and the node QB is at a low level is stored in the ferromagnetic tunnel junction device. In FIG. 19B, a high level is restored to the node Q, and a low level is restored to the node QB. In the same manner, in FIG. 19C, the condition that the node Q is at a low level and the node QB is at a high level is stored in the ferromagnetic tunnel junction device. In FIG. 19D, a low level is restored to the node Q and a high level is restored to the node QB. As described above, in the memory circuit in accordance with the third embodiment, it can be confirmed that the data stored in ferromagnetic tunnel junction devices MTJ1 and MTJ2 can be restored to the bistable circuit 30 after a power source is restored.

FIG. 20A illustrates a simulated characteristic curve of the bistable circuit 30 in the case that a resistance of the ferromagnetic tunnel junction device MTJ1 is a high resistance Rap and the ferromagnetic tunnel junction device MTJ2 is a low resistance Rp when a simulation begins. FIG. 20B illustrates a simulated characteristic curve of the bistable circuit 30 in the case that the ferromagnetic tunnel junction device MTJ1 is a low resistance Rp and the ferromagnetic tunnel junction device MTJ2 is a high resistance Rap when a simulation begins. Solid lines are curves corresponding to the inverter INV1, dashed lines are curves corresponding to the inverter INV2, and a simulation is performed with the lone inverter the input/output of which is decoupled. Arrows indicate a sweeping direction. Curves are illustrated when a power source voltage Vsupply is 1.0 V, 0.5 V and 0.3 V. Arrows with a dashed line indicate the locus of the dynamic operating point when raising a power source voltage from 0 V to 1.0 V after composing bistable circuit 30 by coupling the inputs/outputs of inverters INV1 and INV2 each other (when restoring is performed in FIG. 19B and FIG. 19D).

Referring to FIG. **20**A and FIG. **20**B, when a power source voltage Vsupply is 0.3 V or 0.5 V, a characteristic curve is asymmetric. Accordingly, if a power source voltage Vsupply becomes high, the dynamic operating point of the node Q

converges on a low level, and that of the node QB converges on a high level. In FIG. 20B, the dynamic operating point of the node Q converges on a high level, and that of the node QB converges on a low level. When a power source voltage V supply is fixed to 1.0 V, if the input voltage of the inverter INV2  $^{5}$  in FIG. 20A is swept from 0 V to 1 V and the input voltage of the inverter INV1 in FIG. 20B is swept from 1 V to 0 V respectively, a characteristic curve becomes symmetric because the current  $I_{MTJ1}$  or  $I_{MTJ2}$  flowing in the ferromagnetic tunnel junction device MTJ1 or MTJ2 exceeds the threshold current  $I_{TR}$ . As described, it is preferable to set a power source voltage V supply and resistance values Rp and Rap of ferromagnetic tunnel junction devices MTJ1 and MTJ2 so that the current  $I_{MTJ1}$  or  $I_{MTJ2}$  does not exceed the threshold current  $I_{TR}$  during a restoring operation.

#### Fourth Embodiment

As described in the second and third embodiments, it is because logic thresholds of inverters INV1 and INV2 in FIG. 12 trade places according to stored data (see FIG. 13A and FIG. 13B) that the data stored in the ferromagnetic tunnel junction device can be restored to the bistable circuit 30. Therefore, if logic thresholds of the inverter 10 composing the bistable circuit 30 and the inverter INV2 composed by adding the ferromagnetic tunnel junction device MTJ1 to the inverter 20 are adapted to be different according to stored data, data can be restored even though a single ferromagnetic tunnel junction device is provided, Hereinafter, a description will be given of a composition where a single ferromagnetic tunnel junction device is provided.

FIG. 21A and FIG. 21B are circuit diagrams of a memory circuit in accordance with the fourth embodiment. In the fourth embodiment, compared to the second and third 35 embodiments, the channel width of the FET m4' of the inverter 20 is narrower than the channel width of the FET m3 of the inverter 10. In addition, the ferromagnetic tunnel junction device MTJ2 and the FET m8 are not provided. Accordingly, logic thresholds trade places in the input/output char- 40 acteristics of the inverter 10 and the input/output characteristics of the inverter INV2 between the case that a resistance of the ferromagnetic tunnel junction device MTJ1 is a high resistance Rap and the case of a low resistance Rp. In the same manner as the second and third embodiments, the 45 data stored in the ferromagnetic tunnel junction device MTJ1 can be restored to the bistable circuit 30. The FET m7 can be provided as illustrated in FIG. 21A, or does not have to be provided as illustrated FIG. 21B.

# Fifth Embodiment

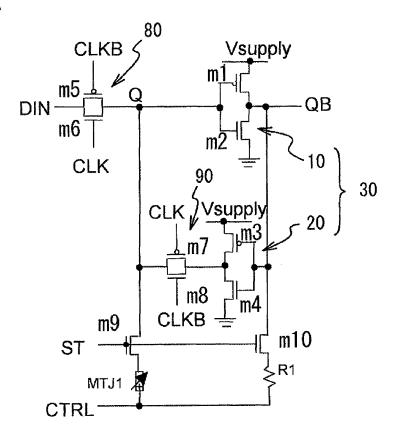

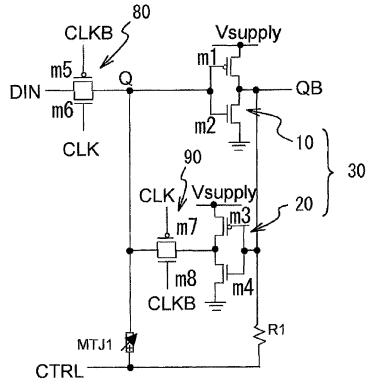

FIG. 22A and FIG. 22B are circuit diagrams of a memory circuit in accordance with the fifth embodiment. In the fifth embodiment, compared to the second and third embodiments, 55 the ferromagnetic tunnel junction device MTJ2 is replaced with a resistance R1. The resistance R1 is set to be between a high resistance Rap and a low resistance Rp of the ferromagnetic tunnel junction device MTJ1. Accordingly, logic thresholds trade places in the input/output characteristics of the inverter INV1 to which the resistance R1 is added and the input/output characteristics of the inverter INV2 between the case that the resistance of the ferromagnetic tunnel junction device MTJ1 is a high resistance Rap and the case that is a low resistance Rp. Therefore, in the same manner as the second 65 and third embodiments, the data stored in the ferromagnetic tunnel junction device MTJ1 can be restored to the bistable

18

circuit 30. The FET m7 and the FET m8 can be provided as illustrated in FIG. 22A, and does not have to be provided as illustrated in FIG. 22B.

#### Sixth Embodiment

FIG. 23A and FIG. 23B are circuit diagrams of a memory circuit in accordance with the sixth embodiment. In the sixth embodiment, compared to the fifth embodiment, a resistance R1 contacts with a ground. Since data in the bistable circuit 30 is stored to the ferromagnetic tunnel junction device MTJ1, it is not necessary for the current to flow in the resistance R1 when the control line CTRL is high level. Therefore, a resistance R1 can contact with a ground. As same with the fifth embodiment, the resistance R1 is set to be between a high resistance Rap and a low resistance Rp. In addition, the FET m7 and the FET m8 can be provided as illustrated in FIG. 23A, and do not have to be provided as illustrated in FIG. 23B.

#### Seventh Embodiment

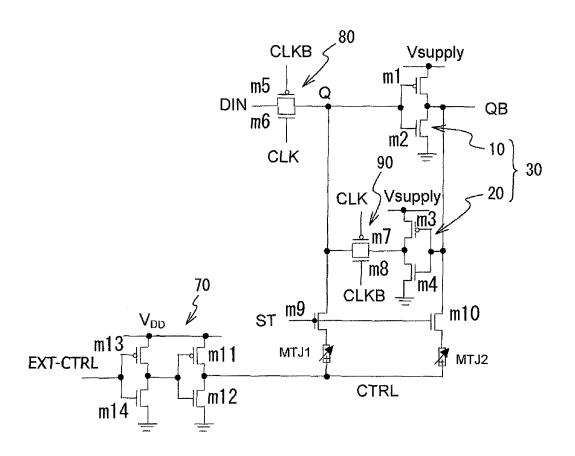

FIG. 24 is a circuit diagram of a memory circuit in accordance with the seventh embodiment. In the seventh embodiment, an output of an amplifier circuit 70 including a two-stage inverter composed of FETs m9 through m12 is coupled to the control line CTRL in FIG. 5 of the second embodiment. An external control line EXT-CTRL is coupled to an input of the amplifier circuit 70, If many memory circuits are controlled with the control line CTRL at the same time, operations will get slow. According to the seventh embodiment, the store and restoration in the memory circuit can be performed at high speed because a signal of the external control line EXT-CTRL is amplified by the amplifier circuit 70.

## Eighth Embodiment

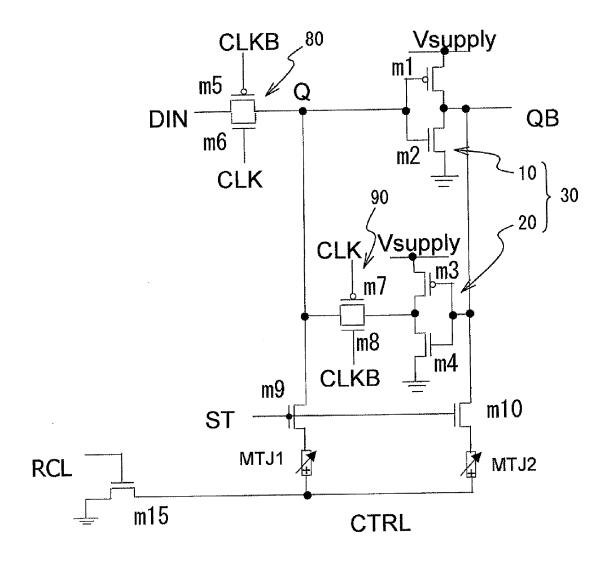

FIG. 25 is a circuit diagram of a memory circuit in accordance with the eighth embodiment. In the eighth embodiment, an n-type MOSFET m13 is coupled between the control line CTRL and a ground, and the gate of the FET m13 is coupled to the second control line RCL. FIG. 26 is a timing diagram of the memory circuit in accordance with the eighth embodiment. When storing, the level of the second control line RCL is at a low level. The FET m13 becomes nonconductive. Therefore, because one of nodes Q and QB has a high level potential and the other has a low level potential, the current flows between the ferromagnetic tunnel junction device MTJ1 and the ferromagnetic tunnel junction device MTJ2, and data in the bistable circuit 30 is stored to ferro-50 magnetic tunnel junction devices MTJ1 and MTJ2. At this time, the voltage of the control line CTRL becomes interlevel between a high level and a low level. When restoring, the second control line RCL is at a high level. As the control line CTRL becomes at a low level, a restoration can be performed in the same manner as the second embodiment. Accordingly, the store and restoration in the memory circuit are performed at high speed regardless of the driving performance of the control line CTRL.

FIG. 27A through FIG. 27D illustrate simulation results of the simulations, which are same as FIG. 17A through FIG. 17D of the second embodiment, to the memory circuit in accordance with the eighth embodiment. As for parameters used for the simulation, threshold currents  $I_{TF}$  and  $I_{TR}$  of the ferromagnetic tunnel junction device are  $15\,\mu\text{A}$  and  $-15\,\mu\text{A}$  respectively, and other parameters are same as the second embodiment. Each diagram is illustrated by adding  $1.5\,\text{V}$  to the level of the node Q,  $3\,\text{V}$  to the level of the control line

CTRL,  $4.5\,\mathrm{V}$  to the second control line RCL,  $6\mathrm{V}$  to the switch line ST,  $7.5\,\mathrm{V}$  to a power source voltage Vsupply, and  $9\,\mathrm{V}$  to the word line WL.

In FIG. 27A, the condition that the node Q is at a high level and the node QB is at a low level is stored in the ferromagnetic tunnel junction device. In FIG. 27B, a high level is restored to the node Q, and a low level is restored to the node QB. In the same manner, in FIG. 27C, the condition that the node Q is at a low level and the node QB is at a high level is stored in the ferromagnetic tunnel junction device. In FIG. 27D, a low level is restored to the node QB and a high level is restored to the node QB. As described above, in the memory circuit in accordance with the eighth embodiment, it is confirmed that the data stored in ferromagnetic tunnel junction devices MTJ1 and MTJ2 can be restored to the bistable circuit 30 after a power source is restored.

#### Ninth Embodiment

FIG. **28** is a circuit diagram of a memory circuit in accordance with the ninth embodiment. In the ninth embodiment, compared to the eighth embodiment, FETs m7 and m8 are not provided. Other components are same as the eighth embodiment. FIG. **29**A through FIG. **29**D are diagrams illustrating simulation results of simulations, which are same as the FIG. **27**A through FIG. **27**D of the eighth embodiment, to the memory circuit in accordance with the ninth embodiment. As for parameters used for simulations, threshold currents  $I_{TF}$  and  $I_{TR}$  of the ferromagnetic tunnel junction device are 6  $\mu$ A and -6  $\mu$ A respectively, a high resistance value Rap and a low resistance value Rp are 50 k $\Omega$  and 25 k $\Omega$  respectively, and other parameters are same as the second embodiment.

In FIG. 29A, the condition that the node Q is at a high level and the node QB is at a low level is stored in the ferromagnetic tunnel junction device. In FIG. 29B, a high level is restored to the node Q and a low level is restored to the node QB. In the same manner, in FIG. 29C, the condition that the node Q is at a low level and the node QB is at a high level is stored in the ferromagnetic tunnel junction device. In FIG. 29D, a low level is restored to the node QB and a high level is restored to the node QB. As described above, it is confirmed that data stored in ferromagnetic tunnel junction devices MTJ1 and MTJ2 can be restored to the bistable circuit 30 also in the memory circuit to which FETs m7 and m8 are not provided in accordance with the ninth embodiment after a power source is 45 restored.

### Tenth Embodiment

FIG. **30** is a circuit diagram of a memory circuit in accordance with the tenth embodiment. In the tenth embodiment, compared to FIG. **5** of the second embodiment, complementary word lines WL and WLB are provided. A pass gate m**5**' is coupled between the node Q and the input/output line DIN, and a pass gate m**6**' is coupled between the node QB and the input/output line DINB. Pass gates m**5**' and m**6**' have a composition where sources of the n-type FET and the p-type FET are coupled each other, and drains of the n-type FET and the p-type FET are coupled each other.

# Eleventh Embodiment

FIG. 31 is a circuit diagram of a memory circuit in accordance with the eleventh embodiment. In the eleventh embodiment, compared to FIG. 5 of the second embodiment, the 65 ferromagnetic tunnel junction device MTJ1 and the FET m7 are replaced with a spin FET 1, and the ferromagnetic tunnel

20

junction device MTJ2 and the FET m8 are replaced with a spin FET 2. As described, a spin FET can be used for the ferromagnetic tunnel junction device. A spin FET is a transistor a conductance of which can be nonvolatilely changed with the magnetization direction, and which has a switching function by a control terminal such as a gate. For example, a spin FET, which is disclosed in International Publication No. 2004-079827 or Journal of the Institute of Electronics, Information and Communication Engineers Vol. 88. No. 7. 2005 PP. 541-550, can be used.

#### Twelfth Embodiment

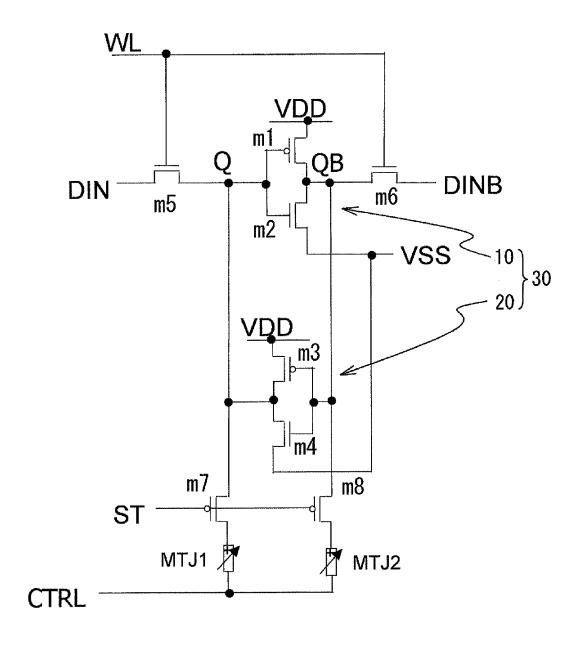

FIG. 32 is a circuit diagram of a memory circuit in accordance with the twelfth embodiment. Compared to the second embodiment, in the twelfth embodiment, inverters 10 and 20 are coupled between power source lines VDD and VSS. In addition, polarities of ferromagnetic tunnel junction devices MTJ1 and MTJ2 are inverted to those of the second embodiment. Accordingly, as the current flows from the node Q or QB to the control line CTRL, the ferromagnetic tunnel junction device MTJ1 or MTJ2 becomes a low resistance Rp, and as the current flows from the control line CTRL to the node Q or QB, the ferromagnetic tunnel junction device MTJ1 or MTJ2 becomes a high resistance Rap. In addition, FETs m7 and m8 are p-type MOSFETs. Other components are same as FIG. 5 of the second embodiment.

FIG. 33 is a timing diagram of the twelfth embodiment. In the twelfth embodiment, shutting down a power source is performed by setting VSS to a high level (VDD level). The level of the control line CTRL and the level of the switch line ST are at a high level in a write mode, sleep mode, and read mode. The switch line ST and the control line CTRL become at a low level during the period T1 of the store, and the switch line ST becomes at a low level and the control line CTRL becomes at a high level during the period T2. Accordingly, data in the bistable circuit 30 is restored to ferromagnetic tunnel junction devices MTJ1 and MTJ2. By setting the switch line to a low level during the period T3 of the restoration, data in ferromagnetic tunnel junction devices MTJ1 and MTJ2 is restored to the bistable circuit 30.

In the twelfth embodiment, the reason why polarities of ferromagnetic tunnel junction devices MTJ1 and MTJ2 are inverted to those of the second embodiment is as follows. For example, when setting the node Q to a high level, to charge the node Q from the control line CTRL against discharge currents of FETs m2 and m4, it is preferable that the ferromagnetic tunnel junction device MTJ1 is a low resistance Rp. Thus, if the polarity of the ferromagnetic tunnel junction device MTJ1 is same as the second embodiment, the ferromagnetic tunnel junction device MTJ1 becomes a high resistance Rap. In addition, the reason why FETs m7 and m8 are pMOSFETs is as follows. In an early stage of the restoration, sources and drains of FETs m7 and m8 are near to a high level. If FETs m7 and m8 are pMOSFETs, by setting the switch line ST to a low level, FETs m7 and m8 are made conductive reliably.

In the third through eleventh embodiments, it is also possible to couple inverters 10 and 20 between a power source line VDD and VSS and to set the polarity of the ferromagnetic tunnel junction device MTJ1 or MTJ2 same as the twelfth embodiment.

According to the second through twelfth embodiments, the ferromagnetic tunnel junction device MTJ1 or MTJ2 is coupled between the node Q or QB, and the control line CTRL. As the current flows between the node Q or QB, and the control line CTRL, the ferromagnetic tunnel junction device MTJ1 or MTJ2 becomes a high resistance, and as the

current flows to counter direction, it becomes a low resistance. Accordingly, by passing the current between the control line CTRL and the node Q or QB according to the level of the node Q or QB, data in the bistable circuit 30 can be stored to the ferromagnetic tunnel junction device.